# **Features**

- High Performance, Low Power AVR<sup>®</sup> 8-Bit Microcontroller

- Advanced RISC Architecture

- 135 Powerful Instructions Most Single Clock Cycle Execution

- 32x8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz and 1.8V

- On-Chip 2-cycle Multiplier

- Non-volatile Program and Data Memories

- 128K Bytes of In-System Self-Programmable Flash

- Endurance: 10'000 Write/Erase Cycles @ 125 °C (25'000 Cycles @ 85 °C)

- 4K Bytes EEPROM

- Endurance: 20'000 Write/Erase Cycles @ 125 ℃ (100'000 Cycles @ 25 ℃) 16K Bytes Internal SRAM

- JTAG (IEEE std. 1149.1 compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash EEPROM, Fuses and Lock Bits through the JTAG interface

- Peripheral Features

- Multiple Timer/Counter & PWM channels

- Real Time Counter with Separate Oscillator

- 10-bit, 330 ks/s A/D Converter; Analog Comparator; On-chip Temperature Sensor

- Master/Slave SPI Serial Interface

- Two Programmable Serial USART

- Byte Oriented 2-wire Serial Interface

- Advanced Interrupt Handler

- Watchdog Timer with Separate On-Chip Oscillator

- Power-on Reset and Low Current Brown-Out Detector

- Advanced Power Save Modes

- Fully integrated Low Power Transceiver for 2.4 GHz ISM Band

- Supported Data Rates: 250 kb/s and 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm RX Sensitivity; TX Output Power up to 3.5 dBm

- Hardware Assisted MAC (Auto-Acknowledge, Auto-Retry)

- 32 Bit IEEE 802.15.4 Symbol Counter

- Baseband Signal Processing

- SFD-Detection, Spreading; De-Spreading; Framing ; CRC-16 Computation

- Antenna Diversity and TX/RX control

- TX/RX 128 Byte Frame Buffer

- Hardware Security (AES, True Random Generator)

- Integrated Crystal Oscillators (32.768 kHz & 16 MHz, external crystal needed)

- I/O and Package

- 38 Programmable I/O Lines

- 64-pad QFN (RoHS/Fully Green)

- Temperature Range: -40 °C to 125 °C Industrial

- Supply voltage range 1.8V to 3.6V with integrated voltage regulators

- Ultra Low Power consumption (1.8 to 3.6V) for Rx/Tx & AVR: <18.6 mA</li>

- CPU Active Mode (16MHz): 4.1 mA

- 2.4GHz Transceiver: RX\_ON 12.5 mA / TX 14.5 mA (maximum TX output power)

- Deep Sleep Mode: <250nA @ 25 ℃

- Speed Grade: 0 16 MHz @ 1.8 3.6V

# **Applications**

- ZigBee<sup>®</sup> / IEEE 802.15.4-2006/2003<sup>™</sup> Full And Reduced Function Device (FFD/RFD)

- General Purpose 2.4GHz ISM Band Transceiver with Microcontroller

- RF4CE, SP100, WirelessHART<sup>™</sup>, ISM Applications and IPv6 / 6LoWPAN

8-bit **AVR**<sup>®</sup> Microcontroller with Low Power 2.4GHz Transceiver for ZigBee and IEEE 802.15.4

# ATmega128RFA1

# PRELIMINARY

8266DS-MCU Wireless-06/12

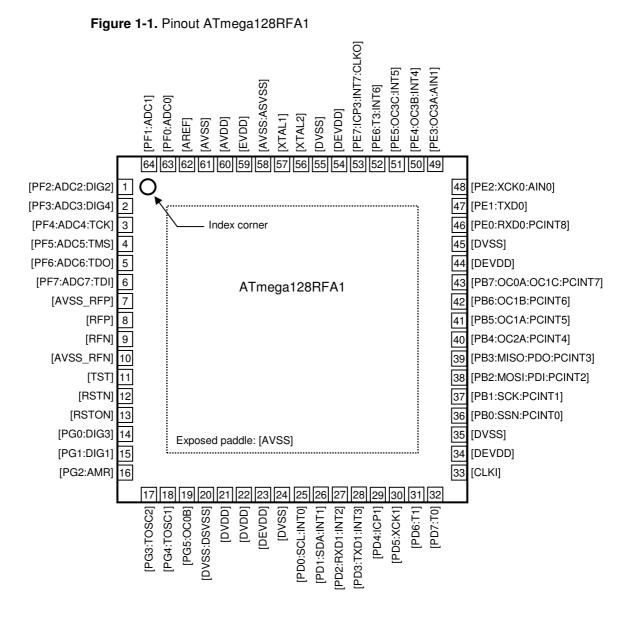

## **1 Pin Configurations**

Note: The large center pad underneath the QFN/MLF package is made of metal and internally connected to AVSS. It should be soldered or glued to the board to ensure good mechanical stability. If the center pad is left unconnected, the package might loosen from the board. It is not recommended to use the exposed paddle as a replacement of the regular AVSS pins.

### 2 Disclaimer

Typical values contained in this datasheet are based on simulation and characterization results of other AVR microcontrollers and radio transceivers manufactured in a similar process technology. Minimum and Maximum values will be available after the device is characterized.

### **3 Overview**

The ATmega128RFA1 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture combined with a high data rate transceiver for the 2.4 GHz ISM band. It is derived from the ATmega1281 microcontroller and the AT86RF231 radio transceiver.

By executing powerful instructions in a single clock cycle, the device achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The radio transceiver provides high data rates from 250 kb/s up to 2 Mb/s, frame handling, outstanding receiver sensitivity and high transmit output power enabling a very robust wireless communication.

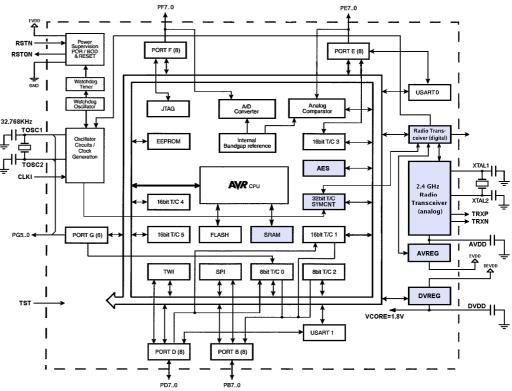

### 3.1 Block Diagram

Figure 3-1 Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All 32 registers are directly connected to the Arithmetic Logic Unit (ALU). Two independent registers can be accessed with one single instruction executed in one clock cycle. The resulting architecture is very code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers. The system includes internal voltage regulation and an advanced power management. Distinguished by the small leakage current it allows an extended operation time from battery.

The radio transceiver is a fully integrated ZigBee solution using a minimum number of external components. It combines excellent RF performance with low cost, small size and low current consumption. The radio transceiver includes a crystal stabilized

fractional-N synthesizer, transmitter and receiver, and full Direct Sequence Spread Spectrum Signal (DSSS) processing with spreading and despreading. The device is fully compatible with IEEE802.15.4-2006/2003 and ZigBee standards.

The ATmega128RFA1 provides the following features: 128K Bytes of In-System Programmable (ISP) Flash with read-while-write capabilities, 4K Bytes EEPROM, 16K Bytes SRAM, up to 35 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), 6 flexible Timer/Counters with compare modes and PWM, USART, a byte oriented 2-wire Serial Interface, a 8 channel, 10 bit analog to digital converter (ADC) with an optional differential input stage with programmable gain, programmable Watchdog Timer with Internal Oscillator, a SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and 6 software selectable power saving modes.

The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the RC oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main RC oscillator and the asynchronous timer continue to run.

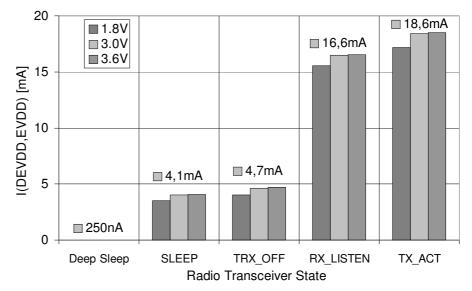

Typical supply current of the microcontroller with CPU clock set to 16MHz and the radio transceiver for the most important states is shown in the Figure 3-2 below.

Figure 3-2 Radio transceiver and microcontroller (16MHz) supply current

The transmit output power is set to maximum. If the radio transceiver is in SLEEP mode the current is dissipated by the AVR microcontroller only.

In Deep Sleep mode all major digital blocks with no data retention requirements are disconnected from main supply providing a very small leakage current. Watchdog timer, MAC symbol counter and 32.768kHz oscillator can be configured to continue to run.

4

The device is manufactured using Atmel's high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system trough an SPI serial interface, by a conventional nonvolatile memory programmer, or by on on-chip boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the boot Flash section will continue to run while the application Flash section is updated, providing true Read-While-Write operation. By combining an 8 bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega128RFA1 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega128RFA1 AVR is supported with a full suite of program and system development tools including: C compiler, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

#### **3.2 Pin Descriptions**

| -                     |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3.2.1 EVDD            | External analog supply voltage.<br>External digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 3.2.2 DEVDD           |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 3.2.3 AVDD            | Regulated analog supply voltage (internally generated).                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 3.2.4 DVDD            | Regulated digital supply voltage (internally generated).                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 3.2.5 DVSS            | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 3.2.6 AVSS            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                       | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 3.2.7 Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. |  |  |  |

|                       | Port B also provides functions of various special features of the ATmega128RFA1.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3.2.8 Port D (PD7PD0) | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running. |  |  |  |

|                       | Port D also provides functions of various special features of the ATmega128RFA1.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3.2.9 Port E (PE7PE0) | Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running. |  |  |  |

|                        | Port E also provides functions of various special features of the ATmega128RFA1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2.10 Port F (PF7PF0) | Port F is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                       |

|                        | Port F also provides functions of various special features of the ATmega128RFA1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.11 Port G (PG5PG0) | Port G is a 6-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. However the driver strength of PG3 and PG4 is reduced compared to the other port pins. The output voltage drop ( $V_{OH}$ , $V_{OL}$ ) is higher while the leakage current is smaller. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                        | Port G also provides functions of various special features of the ATmega128RFA1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.12 AVSS_RFP        | AVSS_RFP is a dedicated ground pin for the bi-directional, differential RF I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.13 AVSS_RFN        | AVSS_RFN is a dedicated ground pin for the bi-directional, differential RF I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.14 RFP             | RFP is the positive terminal for the bi-directional, differential RF I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2.15 RFN             | RFN is the negative terminal for the bi-directional, differential RF I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2.16 RSTN            | Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.2.17 RSTON           | Reset output. A low level on this pin indicates a reset initiated by the internal reset sources or the pin RSTN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.18 XTAL1           | Input to the inverting 16MHz crystal oscillator amplifier. In general a crystal between XTAL1 and XTAL2 provides the 16MHz reference clock of the radio transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.19 XTAL2           | Output of the inverting 16MHz crystal oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2.20 AREF            | Reference voltage output of the A/D Converter. In general this pin is left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.21 TST             | Programming and test mode enable pin. If pin TST is not used pull it to low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2.22 CLKI            | Input to the clock system. If selected, it provides the operating clock of the microcontroller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### 3.3 Unused Pins

Floating pins can cause power dissipation in the digital input stage. They should be connected to an appropriate source. In normal operation modes the internal pull-up resistors can be enabled (in Reset all GPIO are configured as input and the pull-up resistors are still not enabled).

Bi-directional I/O pins shall not be connected to ground or power supply directly.

The digital input pins TST and CLKI must be connected. If unused pin TST can be connected to AVSS while CLKI should be connected to DVSS.

Output pins are driven by the device and do not float. Power supply pins respective ground supply pins are connected together internally.

XTAL1 and XTAL2 shall never be forced to supply voltage at the same time.

#### 3.4 Compatibility to ATmega1281/2561

The basic AVR feature set of the ATmega128RFA1 is derived from the ATmega1281/2561. Address locations and names of the implemented modules and registers are unchanged as long as it fits the target application of a very small and power efficient radio system. In addition, several new features were added.

Backward compatibility of the ATmega128RFA1 to the ATmega1281/2561 is provided in most cases. However some incompatibilities between the microcontrollers exist.

#### 3.4.1 Port A and Port C

Port A and Port C are not implemented. The associated registers are available but will not provide any port control. Remaining ports are kept at their original address location to not require changes of existing software packages.

#### 3.4.2 External Memory Interface

The alternate pin function "External Memory interface" using Port A and Port C is not implemented due to the missing ports.

The large internal data memory (SRAM) does not require an external memory and the associated parallel interface. It keeps the system radiation (EMC) at a very small level to provide very high sensitivity at the antenna input.

#### 3.4.3 High Voltage Programming Mode

Alternate pin function BS2 (high voltage programming) of pin PA0 is mapped to a different pin. Entering the parallel programming mode is controlled by the TST pin.

#### 3.4.4 AVR Oscillators and External Clock

The AVR microcontroller can utilize the high performance crystal oscillator of the 2.4GHz transceiver connected to the pins XTAL1 and XTAL2. An external clock can be applied to the microcontroller using the clock input CLKI.

#### 3.4.5 Analog Frontend

The ATmega128RFA1 has a new A/D converter. Software compatibility is basically assured. Nevertheless to benefit from the higher conversion speeds and the better performance some changes are required.

# **4 Application Circuits**

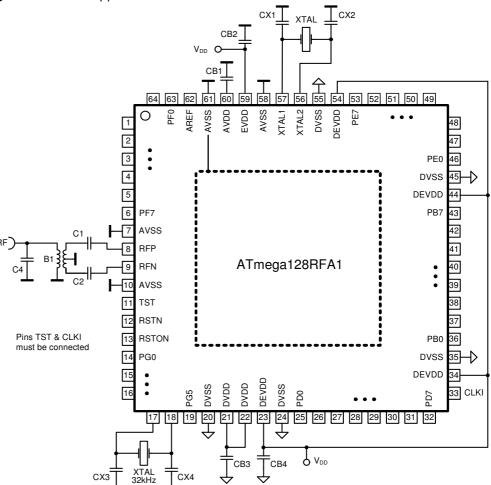

### 4.1 Basic Application Schematic

A basic application schematic of the ATmega128RFA1 with a single-ended RF connector is shown in Figure 4-1 below and the associated Bill of Material in Table 4-1 on page 9. The 50 $\Omega$  single-ended RF input is transformed to the 100 $\Omega$  differential RF port impedance using Balun B1. The capacitors C1 and C2 provide AC coupling of the RF input to the RF port, capacitor C4 improves matching.

The power supply bypass capacitors (CB2, CB4) are connected to the external analog supply pin (EVDD, pin 59) and external digital supply pin (DEVDD, pin 23). Pins 34, 44 and 54 supply the digital port pins.

Floating pins can cause excessive power dissipation (e.g. during power on). They should be connected to an appropriate source. GPIO shall not be connected to ground or power supply directly.

The digital input pins TST and CLKI must be connected. If pin TST will never be used it can be connected to AVSS while an unused pin CLKI could be connected to DVSS (see chapter "Unused Pins" on page 7).

8

Capacitors CB1 and CB3 are bypass capacitors for the integrated analog and digital voltage regulators to ensure stable operation and to improve noise immunity. Capacitors should be placed as close as possible to the pins and should have a low-resistance and low-inductance connection to ground to achieve the best performance.

The crystal (XTAL), the two load capacitors (CX1, CX2), and the internal circuitry connected to pins XTAL1 and XTAL2 form the 16MHz crystal oscillator for the 2.4GHz transceiver. To achieve the best accuracy and stability of the reference frequency, large parasitic capacitances must be avoided. Crystal lines should be routed as short as possible and not in proximity of digital I/O signals. This is especially required for the High Data Rate Modes.

The 32.768 kHz crystal connected to the internal low power (sub 1µA) crystal oscillator provides a stable time reference for all low power modes including 32 Bit IEEE 802.15.4 Symbol Counter ("MAC Symbol Counter") and real time clock application using the asynchronous timer T/C2 ("Timer/Counter2 with PWM and Asynchronous Operation"). Total shunt capacitance including CX3, CX4 should not exceed 15pF across both pins. The very low supply current of the oscillator requires careful layout of the PCB and any leakage path must be avoided.

Crosstalk and radiation from switching digital signals to the crystal pins or the RF pins can degrade the system performance. The programming of minimum drive strength settings for the digital output signal is recommended (see "DPDS0 - Port Driver Strength Register 0").

| Designator               | Description                                                      | Value                                              | Manufacturer                     | Part Number                          | Comment                  |     |

|--------------------------|------------------------------------------------------------------|----------------------------------------------------|----------------------------------|--------------------------------------|--------------------------|-----|

| B1                       | SMD balun<br>SMD balun / filter                                  | 2.4 GHz                                            | Wuerth<br>Johanson<br>Technology | 748421245<br>2450FB15L0001           | Filter included          |     |

| CB1<br>CB3<br>CB2<br>CB4 | LDO VREG<br>bypass capacitor<br>Power supply bypass<br>capacitor | 1 μF<br>(100nF minimum)<br>1 μF<br>(100nF minimum) | AVX<br>Murata                    | 0603YD105KAT2A<br>GRM188R61C105KA12D | X5R 10%<br>(0603)        | 16V |

| CX1, CX2                 | 16MHz crystal load capacitor                                     | 12 pF                                              | AVX<br>Murata                    | 06035A120JA<br>GRP1886C1H120JA01     | COG 5%<br>(0603)         | 50V |

| CX3, CX4                 | 32.768kHz crystal load capacitor                                 | 12 25 pF                                           |                                  |                                      |                          |     |

| C1, C2                   | RF coupling capacitor                                            | 22 pF                                              | Epcos<br>Epcos<br>AVX            | B37930<br>B37920<br>06035A220JAT2A   | C0G 5%<br>(0402 or 0603) | 50V |

| C4 (optional)            | RF matching                                                      | 0.47 pF                                            | Johnstech                        |                                      |                          |     |

| XTAL                     | Crystal                                                          | CX-4025 16 MHz<br>SX-4025 16 MHz                   | ACAL Taitjen<br>Siward           | XWBBPL-F-1<br>A207-011               |                          |     |

| XTAL 32kHz               | Crystal                                                          |                                                    |                                  |                                      | Rs=100 kOhm              |     |

#### Table 4-1. Bill of Materials (BoM)

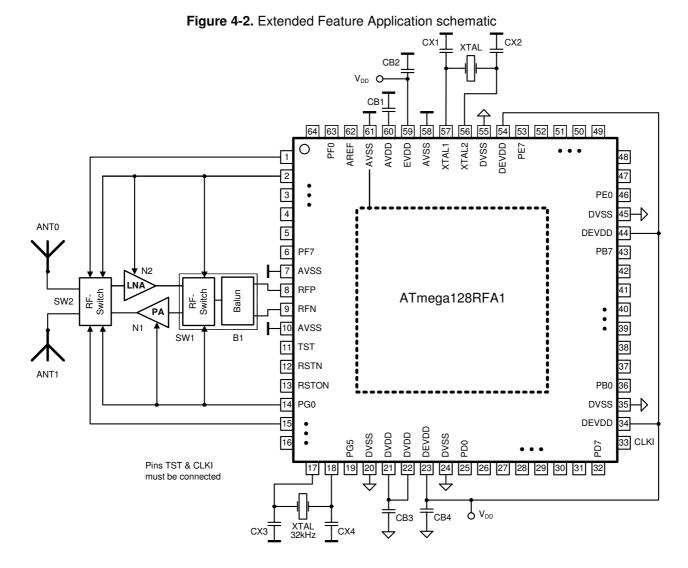

### 4.2 Extended Feature Set Application Schematic

The ATmega128RFA1 supports additional features like:

- Security Module (AES)

- High Data Rate Mode up to 2MBits/s

- Antenna Diversity using alternate pin function DIG1/2 at Port G and F

• RX/TX Indicator using alternate pin function DIG3/4 at Port G and F

An extended feature set application schematic illustrating the use of the ATmega128RFA1 Extended Feature Set, is shown in Figure 4-2 below.

Although this example shows all additional hardware features combined, it is possible to use all features separately or in various combinations.

### **5** Revision history

Please note that the referring page numbers in this section are referring to this document. The referring revision in this section are referring to the document revision

Rev. 8266DS-MCU Wireless-06/12

- 1. Order of revision history changed

- 2. Endurance changed (page 1)

Rev. 8266CS-MCU Wireless-08/11

- 1. Typos corrected (units style)

- 2. Associated pin of internal net ASVSS corrected

#### Rev. 8266BS-MCU Wireless-03/11

- 1. Pin Information added (TST, CLKI)

- 2. Application Schematics modified

- 3. Temperature and endurance modified

#### Rev. 8266AS-MCU Wireless-12/09

1. Initial release

# **Table of Contents**

| 1 Pin Configurations                           |    |  |

|------------------------------------------------|----|--|

| 2 Disclaimer                                   | 2  |  |

| 3 Overview                                     |    |  |

| 3.1 Block Diagram                              |    |  |

| 3.2 Pin Descriptions                           |    |  |

| 3.3 Unused Pins                                | 7  |  |

| 3.4 Compatibility to ATmega1281/2561           | 7  |  |

| 4 Application Circuits                         | 8  |  |

| 4.1 Basic Application Schematic                | 8  |  |

| 4.2 Extended Feature Set Application Schematic | 9  |  |

| 5 Revision history                             |    |  |

| Table of Contents                              | 12 |  |

#### Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support avr@atmel.com Sales Contact www.atmel.com/contacts

Literature Request www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifically provided otherwise, Atmel product as any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2012 Atmel Corporation. All rights reserved. Atmel®, Atmel logo and combinations thereof, AVR® and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.