# **PTN3360A**

# Enhanced performance HDMI/DVI level shifter with inverting HPD

Rev. 02 — 8 October 2009

**Product data sheet**

### 1. General description

The PTN3360A is a high-speed level shifter device which converts four lanes of low-swing AC-coupled differential input signals to DVI v1.0 and HDMI v1.3a compliant open-drain current-steering differential output signals, up to 2.5 Gbit/s per lane. Each of these lanes provides a level-shifting differential buffer to translate from low-swing AC-coupled differential signaling on the source side, to TMDS-type DC-coupled differential current-mode signaling terminated into 50  $\Omega$  to 3.3 V on the sink side. Additionally, the PTN3360A provides a single-ended active buffer for voltage translation of the HPD signal from 5 V on the sink side to 1.1 V on the source side and provides a channel for level shifting of the DDC channel (consisting of a clock and a data line) between 3.3 V source-side and 5 V sink-side. The DDC channel is implemented using pass-gate technology providing level shifting as well as disablement (isolation between source and sink) of the clock and data lines.

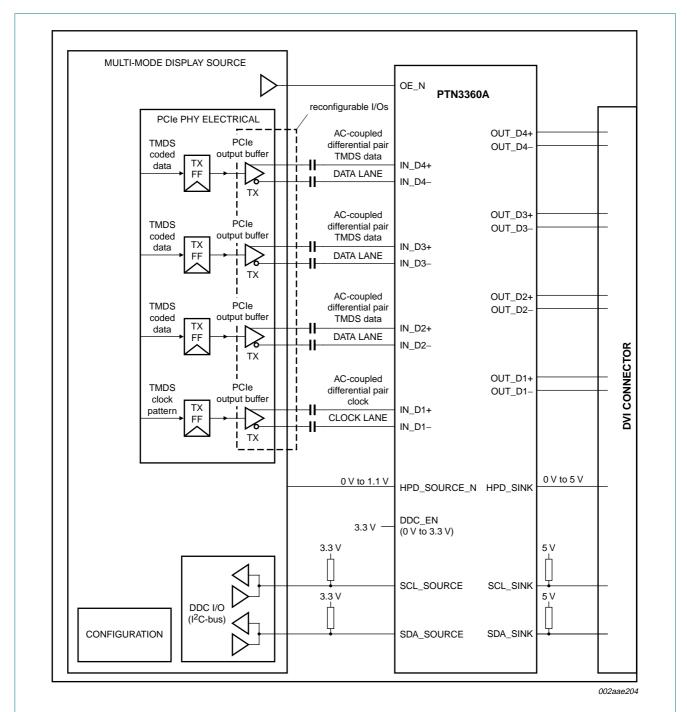

The low-swing AC-coupled differential input signals to the PTN3360A typically come from a display source with multi-mode I/O, which supports multiple display standards, e.g., DisplayPort, HDMI and DVI. While the input differential signals are configured to carry DVI or HDMI coded data, they do not comply with the electrical requirements of the DVI v1.0 or HDMI v1.3a specification. By using PTN3360A, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1.

The PTN3360A main high-speed differential lanes feature low-swing self-biasing differential inputs which are compliant to the electrical specifications of *DisplayPort Standard v1.1* and/or *PCI Express Standard v1.1*, and open-drain current-steering differential outputs compliant to DVI v1.0 and HDMI v1.3a electrical specifications. The I<sup>2</sup>C-bus channel level-translates the DDC signals between 3.3 V (source) and 5.0 V (sink).

The PTN3360A is a fully featured HDMI as well as DVI level shifter. It is functionally equivalent to PTN3300A but provides higher speed performance and higher ESD robustness. The PTN3360A is also equivalent to PTN3360B with the exception that PTN3360A provides inverting level shifting on the HPD channel.

PTN3360A is powered from a single 3.3 V power supply consuming a small amount of power (120 mW typ.) and is offered in a 48-terminal HVQFN48 package.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

Remark: TMDS clock and data lanes can be assigned arbitrarily and interchangeably to D[4:1].

Fig 1. Typical application system diagram

#### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

#### 2. Features

#### 2.1 High-speed TMDS level shifting

- Converts four lanes of low-swing AC-coupled differential input signals to DVI v1.0 and HDMI v1.3a compliant open-drain current-steering differential output signals

- TMDS level shifting operation up to 2.5 Gbit/s per lane (250 MHz character clock)

- Integrated 50  $\Omega$  termination resistors for self-biasing differential inputs

- Back-current safe outputs to disallow current when device power is off and monitor is on

- Disable feature to turn off TMDS inputs and outputs and to enter low-power state

### 2.2 DDC level shifting

- Integrated DDC level shifting (3.3 V source to 5 V sink side)

- 0 Hz to 400 kHz I<sup>2</sup>C-bus clock frequency

- Back-power safe sink-side terminals to disallow backdrive current when power is off or when DDC is not enabled

### 2.3 HPD level shifting

- HPD inverting level shift from 0 V on the sink side to 1.1 V on the source side, or from 5 V on the sink side to 0 V on the source side

- Integrated 200 k $\Omega$  pull-down resistor on HPD sink input guarantees 'input LOW' when no display is plugged in

- Back-power safe design on HPD\_SINK to disallow backdrive current when power is off

#### 2.4 General

- Power supply 3.3 V ± 10 %

- ESD resilience to 8 kV HBM, 500 V CDM

- Power-saving modes (using output enable)

- Back-current-safe design on all sink-side main link, DDC and HPD terminals

- Transparent operation: no re-timing or software configuration required

### 3. Ordering information

Table 1. Ordering information

| Type number | Package | age                                                                                                               |          |  |  |  |  |  |  |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

|             | Name    | Description                                                                                                       | Version  |  |  |  |  |  |  |

| PTN3360ABS  | HVQFN48 | plastic thermal enhanced very thin quad flat package; no leads; 48 terminals; body $7\times7\times0.85~\text{mm}$ | SOT619-1 |  |  |  |  |  |  |

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

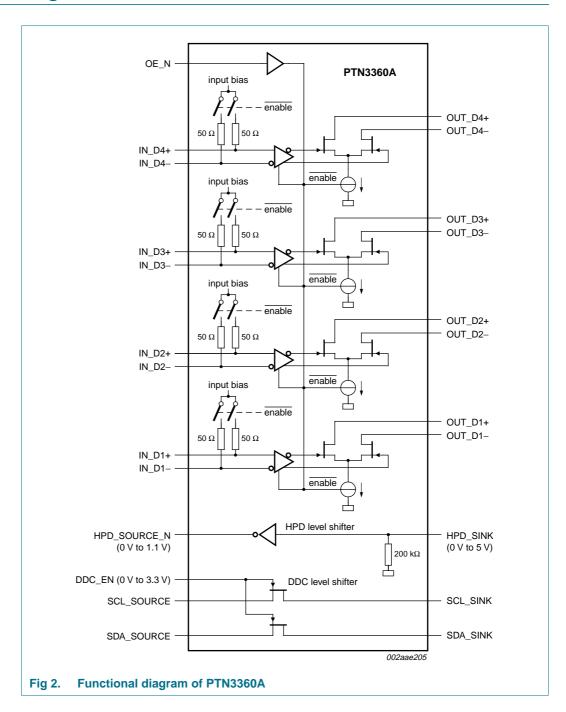

### 4. Functional diagram

**PTN3360A NXP Semiconductors**

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

#### **Pinning information** 5.

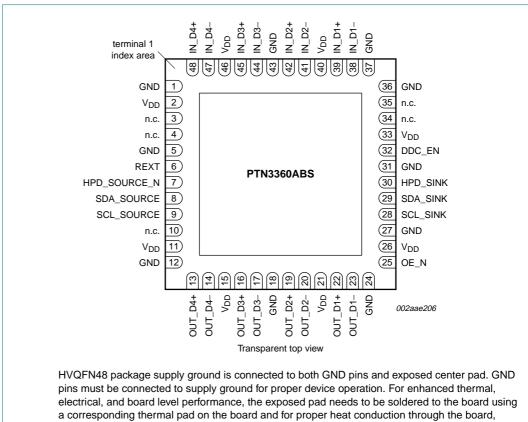

### 5.1 Pinning

thermal vias need to be incorporated in the PCB in the thermal pad region.

Fig 3. Pin configuration for HVQFN48

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 5.2 Pin description

Table 2. Pin description

| Symbol     | Pin             | Туре                                | Description                                                                                                                                                                                 |

|------------|-----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE_N, IN_C | Ox and OUT_Dx s | ignals                              |                                                                                                                                                                                             |

| OE_N       | 25              | 3.3 V low-voltage CMOS single-ended | Output Enable and power saving function for high-speed differential level shifter path.                                                                                                     |

|            |                 | input                               | When OE_N = HIGH:                                                                                                                                                                           |

|            |                 |                                     | IN_Dx termination = high-impedance                                                                                                                                                          |

|            |                 |                                     | OUT_Dx outputs = high-impedance; zero output current                                                                                                                                        |

|            |                 |                                     | When OE_N = LOW:                                                                                                                                                                            |

|            |                 |                                     | IN_Dx termination = $50 \Omega$                                                                                                                                                             |

|            |                 |                                     | OUT_Dx outputs = active                                                                                                                                                                     |

| IN_D4+     | 48              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D4+ makes a differential pair with IN_D4 The input to this pin must be AC coupled externally.   |

| IN_D4-     | 47              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D4- makes a differential pair with IN_D4+. The input to this pin must be AC coupled externally. |

| IN_D3+     | 45              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D3+ makes a differential pair with IN_D3 The input to this pin must be AC coupled externally.   |

| IN_D3-     | 44              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D3- makes a differential pair with IN_D3+. The input to this pin must be AC coupled externally. |

| IN_D2+     | 42              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D2+ makes a differential pair with IN_D2 The input to this pin must be AC coupled externally.   |

| IN_D2-     | 41              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D2- makes a differential pair with IN_D2+. The input to this pin must be AC coupled externally. |

| IN_D1+     | 39              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D1+ makes a differential pair with IN_D1 The input to this pin must be AC coupled externally.   |

| IN_D1-     | 38              | Self-biasing<br>differential input  | Low-swing differential input from display source with PCI Express electrical signalling. IN_D1– makes a differential pair with IN_D1+. The input to this pin must be AC coupled externally. |

| OUT_D4+    | 13              | TMDS differential output            | HDMI compliant TMDS output. OUT_D4+ makes a differential pair with OUT_D4 OUT_D4+ is in phase with IN_D4+.                                                                                  |

| OUT_D4-    | 14              | TMDS differential output            | HDMI compliant TMDS output. OUT_D4- makes a differential pair with OUT_D4+. OUT_D4- is in phase with IN_D4                                                                                  |

| OUT_D3+    | 16              | TMDS differential output            | HDMI compliant TMDS output. OUT_D3+ makes a differential pair with OUT_D3 OUT_D3+ is in phase with IN_D3+.                                                                                  |

| OUT_D3-    | 17              | TMDS differential output            | HDMI compliant TMDS output. OUT_D3- makes a differential pair with OUT_D3+. OUT_D3- is in phase with IN_D3                                                                                  |

| OUT_D2+    | 19              | TMDS differential output            | HDMI compliant TMDS output. OUT_D2+ makes a differential pair with OUT_D2 OUT_D2+ is in phase with IN_D2+.                                                                                  |

| OUT_D2-    | 20              | TMDS differential output            | HDMI compliant TMDS output. OUT_D2- makes a differential pair with OUT_D2+. OUT_D2- is in phase with IN_D2                                                                                  |

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

Table 2.

Pin description ...continued

| Table 2. Pin de   | scription                                     | continued                                |                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin                                           | Туре                                     | Description                                                                                                                                                                                                                                                                                                                                  |

| OUT_D1+           | 22                                            | TMDS differential output                 | HDMI compliant TMDS output. OUT_D1+ makes a differential pair with OUT_D1 OUT_D1+ is in phase with IN_D1+.                                                                                                                                                                                                                                   |

| OUT_D1-           | 23                                            | TMDS differential output                 | HDMI compliant TMDS output. OUT_D1- makes a differential pair with OUT_D1+. OUT_D1- is in phase with IN_D1                                                                                                                                                                                                                                   |

| HPD and DDC sig   | ınals                                         |                                          |                                                                                                                                                                                                                                                                                                                                              |

| HPD_SINK          | 30                                            | 5 V CMOS<br>single-ended input           | 0 V to 5 V (nominal) input signal. This signal comes from the DVI or HDMI sink. A HIGH value indicates that the sink is connected; a LOW value indicates that the sink is disconnected. HPD_SINK is pulled down by an integrated 200 k $\Omega$ pull-down resistor.                                                                          |

| HPD_SOURCE_<br>N  | 7                                             | 1.1 V CMOS single-ended output           | 0 V to 1.1 V (nominal) output signal. This is level-shifted <b>logic-inverted</b> version of the HPD_SINK signal.                                                                                                                                                                                                                            |

| SCL_SOURCE        | 9                                             | single-ended 3.3 V<br>open-drain DDC I/O | $3.3\ \mbox{V}$ source-side DDC clock I/O. Pulled up by external termination to $3.3\ \mbox{V}.$                                                                                                                                                                                                                                             |

| SDA_SOURCE        | 8                                             | single-ended 3.3 V<br>open-drain DDC I/O | $3.3\ \mbox{V}$ source-side DDC data I/O. Pulled up by external termination to $3.3\ \mbox{V}.$                                                                                                                                                                                                                                              |

| SCL_SINK          | 28                                            | single-ended 5 V<br>open-drain DDC I/O   | 5 V sink-side DDC clock I/O. Pulled up by external termination to 5 V.                                                                                                                                                                                                                                                                       |

| SDA_SINK          | 29                                            | single-ended 5 V<br>open-drain DDC I/O   | 5 V sink-side DDC data I/O. Pulled up by external termination to 5 V.                                                                                                                                                                                                                                                                        |

| DDC_EN            | 32                                            | 3.3 V CMOS input                         | Enables the DDC buffer and level shifter.                                                                                                                                                                                                                                                                                                    |

|                   |                                               |                                          | When DDC_EN = LOW, buffer/level shifter is disabled.                                                                                                                                                                                                                                                                                         |

|                   |                                               |                                          | When DDC_EN = HIGH, buffer and level shifter are enabled.                                                                                                                                                                                                                                                                                    |

| Supply and groun  | nd                                            |                                          |                                                                                                                                                                                                                                                                                                                                              |

| $V_{DD}$          | 2, 11, 15,<br>21, 26, 33,<br>40, 46           | 3.3 V DC supply                          | Supply voltage; 3.3 V $\pm$ 10 %.                                                                                                                                                                                                                                                                                                            |

| V <sub>CC</sub>   | -                                             |                                          |                                                                                                                                                                                                                                                                                                                                              |

| GND[1]            | 1, 5, 12,<br>18, 24, 27,<br>31, 36, 37,<br>43 | ground                                   | Supply ground. All GND pins must be connected to ground for proper operation.                                                                                                                                                                                                                                                                |

| Feature control s | ignals                                        |                                          |                                                                                                                                                                                                                                                                                                                                              |

| REXT              | 6                                             | analog I/O                               | Current sense port used to provide an accurate current reference for the differential outputs OUT_Dx. For best output voltage swing accuracy, use of a 10 k $\Omega$ resistor (1 % tolerance) from this terminal to GND is recommended. May also be left open-circuit or tied to either V <sub>DD</sub> or GND. See Section 6.2 for details. |

| Miscellaneous     |                                               |                                          |                                                                                                                                                                                                                                                                                                                                              |

| n.c.              | 3, 4, 10,<br>34, 35                           | no connection to the die                 | Not connected. May be left open-circuit or tied to GND or $V_{\text{DD}}$ either directly or via a resistor.                                                                                                                                                                                                                                 |

|                   |                                               |                                          |                                                                                                                                                                                                                                                                                                                                              |

<sup>[1]</sup> HVQFN48 package supply ground is connected to both GND pins and exposed center pad. GND pins must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias need to be incorporated in the PCB in the thermal pad region.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 6. Functional description

Refer to Figure 2 "Functional diagram of PTN3360A".

The PTN3360A level shifts four lanes of low-swing AC-coupled differential input signals to DVI and HDMI compliant open-drain current-steering differential output signals, up to 2.5 Gbit/s per lane. It has integrated 50  $\Omega$  termination resistors for AC-coupled differential input signals. An enable signal OE\_N can be used to turn off the TMDS inputs and outputs, thereby minimizing power consumption. The TMDS outputs, HPD\_SINK input and DDC\_SINK I/Os are back-power safe to disallow current flow from a powered sink while the PTN3360A is unpowered.

The PTN3360A's DDC channel provides active level shifting and buffering, allowing 3.3 V source-side termination and 5 V sink-side termination. The sink-side DDC ports are equipped with a rise time accelerator enabling drive of long cables or high bus capacitance. This enables the system designer to isolate bus capacitance to meet HDMI DDC version 1.3a distance specification. The PTN3360A offers back-power safe sink-side I/Os to disallow backdrive current from the DDC clock and data lines when power is off or when DDC is not enabled. An enable signal DCC\_EN enables the DDC level shifter block.

The PTN3360A also provides voltage translation for the Hot Plug Detect (HPD) signal from 0 V to 5 V on the sink side, inverting and level-shifting to 1.1V/0 V on the source side.

The PTN3360A does not re-time any data. It contains no state machines except for the DDC/I<sup>2</sup>C-bus block. No inputs or outputs of the device are latched or clocked. Because the PTN3360A acts as a transparent level shifter, no reset is required.

#### 6.1 Enable and disable features

PTN3360A offers different ways to enable or disable functionality, using the Output Enable (OE\_N) and DDC Enable (DDC\_EN) inputs. Whenever the PTN3360A is disabled, the device will be in Standby mode and power consumption will be minimal; otherwise the PTN3360A will be in Active mode and power consumption will be nominal. These two inputs each affect the operation of PTN3360A differently: OE\_N affects only the TMDS channels, and DDC\_EN affects only the DDC channel. HPD\_SINK does not affect either of the channels. The following sections and truth table describe their detailed operation.

### 6.1.1 Hot plug detect

The HPD channel of PTN3360A functions as a level-shifting buffer to pass the HPD logic signal from the display sink device (via input HPD\_SINK) on to the display source device (via output HPD\_SOURCE\_N).

The output logic state of HPD\_SOURCE\_N output always follows the inverse logic state of input HPD\_SINK, regardless of whether the device is in Active or Standby mode.

#### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 6.1.2 Output Enable function (OE\_N)

When input OE\_N is asserted (active LOW), the IN\_Dx and OUT\_Dx signals are fully functional. Input termination resistors are enabled and the internal bias circuits are turned on.

When OE\_N is de-asserted (inactive HIGH), the OUT\_Dx outputs are in a high-impedance state and drive zero output current. The IN\_Dx input buffers are disabled and IN\_Dx termination is disabled. Power consumption is minimized.

**Remark:** Note that OE\_N has no influence on the HPD\_SINK input, HPD\_SOURCE\_N output, or the SCL and SDA level shifters. OE\_N only affects the high-speed TMDS channel.

### 6.1.3 DDC channel enable function (DDC\_EN)

The DDC\_EN pin is active HIGH and can be used to isolate a badly behaved slave. When DDC\_EN is LOW, the DDC channel is turned off. The DDC\_EN input should never change state during an I<sup>2</sup>C-bus operation. Note that disabling DDC\_EN during a bus operation will hang the bus, while enabling DDC\_EN during bus traffic would corrupt the I<sup>2</sup>C-bus operation. Hence, DDC\_EN should only be toggled while the bus is idle. (See I<sup>2</sup>C-bus specification).

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

#### 6.1.4 Enable/disable truth table

Table 3. HPD\_SINK, OE\_N and DDC\_EN enabling truth table

| Inputs   |             |        | Channels                                   |                                        |                                                                                      |                  |                            |  |

|----------|-------------|--------|--------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|------------------|----------------------------|--|

| HPD_SINK | OE_N<br>[1] | DDC_EN | IN_Dx                                      | OUT_Dx <sup>[3]</sup>                  | DDC[4]                                                                               | HPD_SOURCE_N [5] |                            |  |

| LOW      | LOW         | LOW    | 50 $\Omega$ termination to $V_{RX(bias)}$  | enabled                                | high-impedance                                                                       | HIGH             | Active;<br>DDC<br>disabled |  |

| LOW      | LOW         | HIGH   | $50~\Omega~termination \\ to~V_{RX(bias)}$ | enabled                                | SDA_SINK<br>connected to<br>SDA_SOURCE<br>and SCL_SINK<br>connected to<br>SCL_SOURCE | HIGH             | Active;<br>DDC<br>enabled  |  |

| LOW      | HIGH        | LOW    | high-impedance                             | high-impedance;<br>zero output current | high-impedance                                                                       | HIGH             | Standby                    |  |

| LOW      | HIGH        | HIGH   | high-impedance                             | high-impedance;<br>zero output current | SDA_SINK<br>connected to<br>SDA_SOURCE<br>and SCL_SINK<br>connected to<br>SCL_SOURCE | HIGH             | Standby;<br>DDC<br>enabled |  |

| HIGH     | LOW         | LOW    | 50 $\Omega$ termination to $V_{RX(bias)}$  | enabled                                | high-impedance                                                                       | LOW              | Active;<br>DDC<br>disabled |  |

| HIGH     | LOW         | HIGH   | 50 $\Omega$ termination to $V_{RX(bias)}$  | enabled                                | SDA_SINK<br>connected to<br>SDA_SOURCE<br>and SCL_SINK<br>connected to<br>SCL_SOURCE | LOW              | Active;<br>DDC<br>enabled  |  |

| HIGH     | HIGH        | LOW    | high-impedance                             | high-impedance;<br>zero output current | high-impedance                                                                       | LOW              | Standby                    |  |

| HIGH     | HIGH        | HIGH   | high-impedance                             | high-impedance;<br>zero output current | SDA_SINK<br>connected to<br>SDA_SOURCE<br>and SCL_SINK<br>connected to<br>SCL_SOURCE | LOW              | Standby;<br>DDC<br>enabled |  |

<sup>[1]</sup> A HIGH level on input OE\_N disables only the TMDS channels.

<sup>[2]</sup> A LOW level on input DDC\_EN disables only the DDC channel.

<sup>[3]</sup> OUT\_Dx channels 'enabled' means outputs OUT\_Dx toggling in accordance with IN\_Dx differential input voltage switching.

<sup>[4]</sup> DDC channel 'enabled' means SDA\_SINK is connected to SDA\_SOURCE and SCL\_SINK is connected to SCL\_SOURCE.

<sup>[5]</sup> The HPD\_SOURCE\_N output logic state always follows the inverse of the HPD\_SINK input logic state.

#### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

#### 6.2 Analog current reference

The REXT pin (pin 6) is an analog current sense port used to provide an accurate current reference for the differential outputs OUT\_Dx. For best output voltage swing accuracy, use of a 10 k $\Omega$  resistor (1 % tolerance) connected between this terminal and GND is recommended.

If an external 10 k $\Omega$   $\pm$  1 % resistor is not used, this pin can be left open-circuit, or connected to GND or V<sub>DD</sub>, either directly (0  $\Omega$ ) or using pull-up or pull-down resistors of value less than 10 k $\Omega$ . In any of these cases, the output will function normally but at reduced accuracy over voltage and temperature of the following parameters: output levels (V<sub>OL</sub>), differential output voltage swing, and rise and fall time accuracy.

### 6.3 Backdrive current protection

The PTN3360A is designed for backdrive prevention on all sink-side TMDS outputs, sink-side DDC I/Os and the HPD\_SINK input. This supports user scenarios where the display is connected and powered, but the PTN3360A is unpowered. In these cases, the PTN3360A will sink no more than a negligible amount of leakage current, and will block the display (sink) termination network from driving the power supply of the PTN3360A or that of the inactive DVI or HDMI source.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 7. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions        | Min          | Max            | Unit |

|------------------|---------------------------------|-------------------|--------------|----------------|------|

| $V_{DD}$         | supply voltage                  |                   | -0.3         | +4.6           | V    |

| VI               | input voltage                   | 3.3 V CMOS inputs | -0.3         | $V_{DD} + 0.5$ | V    |

|                  |                                 | 5.0 V CMOS inputs | -0.3         | 6.0            | V    |

| T <sub>stg</sub> | storage temperature             |                   | -65          | +150           | °C   |

| V <sub>ESD</sub> | electrostatic discharge voltage | HBM               | <u>[1]</u> - | 8000           | V    |

|                  |                                 | CDM               | [2] _        | 500            | V    |

<sup>[1]</sup> Human Body Model: ANSI/EOS/ESD-S5.1-1994, standard for ESD sensitivity testing, Human Body Model - Component level; Electrostatic Discharge Association, Rome, NY, USA.

### 8. Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol                | Parameter                                    | Conditions                                 |            | Min | Тур      | Max | Unit |

|-----------------------|----------------------------------------------|--------------------------------------------|------------|-----|----------|-----|------|

| $V_{DD}$              | supply voltage                               |                                            |            | 3.0 | 3.3      | 3.6 | V    |

| VI                    | input voltage                                | 3.3 V CMOS inputs                          |            | 0   | -        | 3.6 | V    |

|                       |                                              | 5.0 V CMOS inputs                          |            | 0   | -        | 5.5 | V    |

| $V_{I(AV)}$           | average input voltage                        | IN_Dn+, IN_Dn- inputs                      | <u>[1]</u> | -   | 0        | -   | V    |

| R <sub>ref(ext)</sub> | external reference resistance <sup>[2]</sup> | connected between pin REXT (pin 6) and GND |            | -   | 10 ± 1 % | -   | kΩ   |

| T <sub>amb</sub>      | ambient temperature                          | operating in free air                      |            | -40 | -        | +85 | °C   |

<sup>[1]</sup> Input signals to these pins must be AC-coupled.

### 8.1 Current consumption

Table 6. Current consumption

| Symbol          | Parameter      | Conditions                                      | Min | Тур | Max | Unit |

|-----------------|----------------|-------------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> | supply current | OE_N = 0; Active mode                           | 10  | 35  | 50  | mA   |

|                 |                | OE_N = 1 <b>and</b> DDC_EN = 0;<br>Standby mode | -   | 8.0 | 1.5 | mA   |

<sup>[2]</sup> Charged-Device Model: ANSI/EOS/ESD-S5.3-1-1999, standard for ESD sensitivity testing, Charged-Device Model - Component level; Electrostatic Discharge Association, Rome, NY, USA.

<sup>[2]</sup> Operation without external reference resistor is possible but will result in reduced output voltage swing accuracy. For details, see Section 6.2.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 9. Characteristics

### 9.1 Differential inputs

Table 7. Differential input characteristics for IN\_Dx signals

|                       |                                         | _                                        |            |       |     |       |      |

|-----------------------|-----------------------------------------|------------------------------------------|------------|-------|-----|-------|------|

| Symbol                | Parameter                               | Conditions                               |            | Min   | Тур | Max   | Unit |

| UI                    | unit interval <sup>[1]</sup>            |                                          | [2]        | 360   | -   | 4000  | ps   |

| $V_{RX\_DIFFp-p}$     | differential input peak-to-peak voltage |                                          | [3]        | 0.175 | -   | 1.200 | V    |

| T <sub>RX_EYE</sub>   | receiver eye time                       | minimum eye width at IN_Dx input pair    |            | 8.0   | -   | -     | UI   |

| $V_{i(cm)M(AC)}$      | peak common-mode input voltage (AC)     | includes all frequencies<br>above 30 kHz | <u>[4]</u> | -     | -   | 100   | mV   |

| $Z_{RX\_DC}$          | DC input impedance                      |                                          |            | 40    | 50  | 60    | Ω    |

| V <sub>RX(bias)</sub> | bias receiver voltage                   |                                          | [5]        | 1.0   | 1.2 | 1.4   | V    |

| Z <sub>I(se)</sub>    | single-ended input impedance            | inputs in high-impedance state           | [6]        | 100   | -   | -     | kΩ   |

<sup>[1]</sup> UI (unit interval) =  $t_{bit}$  (bit time).

<sup>[2]</sup> UI is determined by the display mode. Nominal bit rate ranges from 250 Mbit/s to 2.5 Gbit/s per lane. Nominal UI at 2.5 Gbit/s = 400 ps. 360 ps = 400 ps - 10 %.

<sup>[3]</sup>  $V_{RX\_DIFFp-p} = 2 \times |V_{RX\_D+} - V_{RX\_D-}|$ . Applies to IN\_Dx signals.

$<sup>\</sup>begin{split} [4] \quad & V_{i(cm)M(AC)} = |V_{RX\_D+} + V_{RX\_D-}| \: / \: 2 - V_{RX(cm)}. \\ & V_{RX(cm)} = DC \: (avg) \: of \: |V_{RX\_D+} + V_{RX\_D-}| \: / \: 2. \end{split}$

<sup>[5]</sup> Intended to limit power-up stress on chip set's PCIe output buffers.

<sup>[6]</sup> Differential inputs will switch to a high-impedance state when OE\_N is LOW.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 9.2 Differential outputs

The level shifter's differential outputs are designed to meet HDMI version 1.3 and DVI version 1.0 specifications.

Table 8. Differential output characteristics for OUT\_Dx signals

|                     | •                                      | _ 0                                                                                                                       |            |                        |                        |                        |      |

|---------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------|------------------------|------------------------|------------------------|------|

| Symbol              | Parameter                              | Conditions                                                                                                                |            | Min                    | Тур                    | Max                    | Unit |

| V <sub>OH(se)</sub> | single-ended HIGH-level output voltage |                                                                                                                           | <u>[1]</u> | $V_{TT} - 0.01$        | $V_{TT}$               | V <sub>TT</sub> + 0.01 | V    |

| V <sub>OL(se)</sub> | single-ended LOW-level output voltage  |                                                                                                                           | [2]        | V <sub>TT</sub> – 0.60 | V <sub>TT</sub> – 0.50 | $V_{TT}-0.40$          | V    |

| $\Delta V_{O(se)}$  | single-ended output voltage variation  | logic 1 and logic 0 state applied respectively to differential inputs IN_Dn; R <sub>ref(ext)</sub> connected; see Table 5 | [3]        | 400                    | 500                    | 600                    | mV   |

| l <sub>OZ</sub>     | OFF-state output current               | single-ended                                                                                                              |            | -                      | -                      | 10                     | μΑ   |

| t <sub>r</sub>      | rise time                              | 20 % to 80 %                                                                                                              | <u>[4]</u> | 75                     | -                      | 160                    | ps   |

| t <sub>f</sub>      | fall time                              | 80 % to 20 %                                                                                                              | <u>[4]</u> | 75                     | -                      | 160                    | ps   |

| t <sub>sk</sub>     | skew time                              | intra-pair                                                                                                                | <u>[5]</u> | -                      | -                      | 10                     | ps   |

|                     |                                        | inter-pair                                                                                                                | [6]        | -                      | -                      | 250                    | ps   |

| t <sub>jit</sub>    | jitter time                            | jitter contribution                                                                                                       | <u>[7]</u> | -                      | -                      | 7.4                    | ps   |

|                     |                                        |                                                                                                                           |            |                        |                        |                        |      |

<sup>[1]</sup>  $V_{TT}$  is the DC termination voltage in the HDMI or DVI sink.  $V_{TT}$  is nominally 3.3 V.

<sup>[2]</sup> The open-drain output pulls down from  $V_{TT}$ .

<sup>[3]</sup> Swing down from TMDS termination voltage (3.3 V  $\pm$  10 %).

<sup>[4]</sup> Maximum rise/fall time at 2.5 Gbit/s = 400 ps. 360 ps = 400 ps - 10 %.

<sup>[5]</sup> This differential skew budget is in addition to the skew presented between IN\_D+ and IN\_D- paired input pins.

<sup>[6]</sup> This lane-to-lane skew budget is in addition to skew between differential input pairs.

<sup>[7]</sup> Jitter budget for differential signals as they pass through the level shifter.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 9.3 HPD\_SINK input, HPD\_SOURCE\_N output

Table 9. HPD characteristics

| Symbol          | Parameter                 | Conditions                                                         |            | Min | Тур | Max | Unit |

|-----------------|---------------------------|--------------------------------------------------------------------|------------|-----|-----|-----|------|

| $V_{IH}$        | HIGH-level input voltage  | HPD_SINK                                                           | [1]        | 2.0 | 5.0 | 5.3 | V    |

| $V_{IL}$        | LOW-level input voltage   | HPD_SINK                                                           |            | 0   | -   | 8.0 | V    |

| I <sub>LI</sub> | input leakage current     | HPD_SINK                                                           | [2]        | -   | -   | 10  | μΑ   |

| $V_{OH}$        | HIGH-level output voltage | HPD_SOURCE_N; $I_{OH} = 100 \mu A$ ;<br>HPD_SINK = LOW             |            | 0.7 | -   | 1.1 | V    |

| $V_{OL}$        | LOW-level output voltage  | HPD_SOURCE_N; $I_{OH}$ = 100 $\mu$ A;<br>HPD_SINK = HIGH           |            | 0   | -   | 0.2 | V    |

| t <sub>PD</sub> | propagation delay         | from HPD_SINK to HPD_SOURCE_N; 50 % to 50 %; $C_L = 10 \text{ pF}$ | [3]        | -   | -   | 200 | ns   |

| t <sub>t</sub>  | transition time           | HPD_SOURCE_N rise/fall;<br>10 % to 90 %; $C_L = 10 \text{ pF}$     | [4]        | 1   | -   | 20  | ns   |

| R <sub>pd</sub> | pull-down resistance      | HPD_SINK input pull-down resistor                                  | <u>[5]</u> | 100 | 200 | 300 | kΩ   |

<sup>[1]</sup> Low-speed input changes state on cable plug/unplug.

### 9.4 OE\_N, DDC\_EN inputs

Table 10. OE\_N, DDC\_EN and DDET input characteristics

| Symbol          | Parameter                | Conditions | Min          | Тур | Max | Unit |

|-----------------|--------------------------|------------|--------------|-----|-----|------|

| $V_{IH}$        | HIGH-level input voltage |            | 2.0          | -   | -   | V    |

| $V_{IL}$        | LOW-level input voltage  |            | -            | -   | 8.0 | V    |

| I <sub>LI</sub> | input leakage current    | OE_N pin   | <u>[1]</u> _ | -   | 10  | μΑ   |

<sup>[1]</sup> Measured with input at  $V_{IH}$  maximum and  $V_{IL}$  minimum.

#### 9.5 DDC characteristics

Table 11. DDC characteristics

| Symbol           | Parameter                            | Conditions                                                     | Min | Тур | Max | Unit |  |

|------------------|--------------------------------------|----------------------------------------------------------------|-----|-----|-----|------|--|

| f <sub>clk</sub> | clock frequency                      | SCL_SOURCE, SDA_SOURCE, SCL_SINK, SDA_SINK                     | -   | -   | 400 | kHz  |  |

| ON state         | (DDC_EN = HIGH)                      |                                                                |     |     |     |      |  |

| R <sub>ON</sub>  | ON resistance                        | pass gate in ON state; $I_O = 15$ mA; $V_O = 0.4$ V            | -   | 7   | 30  | Ω    |  |

| $V_{O(sw)}$      | switch output voltage                | source side; $V_I$ = 3.3 V; $I_O$ = -100 $\mu A$               | 1.7 | 2.1 | 2.5 | V    |  |

|                  |                                      | sink side; $V_I = 5.0 \text{ V}$ ; $I_O = -100 \mu\text{A}$    | 1.7 | 2.1 | 2.5 | V    |  |

| C <sub>io</sub>  | input/output capacitance             | $V_{I} = 3.3 \text{ V}$                                        | -   | 5   | 10  | pF   |  |

| OFF state        | e (DDC_EN = LOW)                     |                                                                |     |     |     |      |  |

| I <sub>LI</sub>  | input leakage current                | source side; 0 V < $V_I$ < 3.3 V                               | -10 | -   | +10 | μΑ   |  |

|                  |                                      | sink side; $0 \text{ V} < \text{V}_{\text{I}} < 5.0 \text{ V}$ | -10 | -   | +10 | μΑ   |  |

| C <sub>io</sub>  | input/output capacitance             | V <sub>I</sub> = 3.3 V                                         | -   | 1   | 5   | pF   |  |

| PTN3360A_2       | © NXP B.V. 2009. All rights reserved |                                                                |     |     |     |      |  |

<sup>[2]</sup> Measured with HPD\_SINK at  $V_{IH}$  maximum and  $V_{IL}$  minimum.

<sup>[3]</sup> Time from HPD\_SINK changing state to HPD\_SOURCE\_N changing state. Includes HPD\_SOURCE\_N rise/fall time.

<sup>[4]</sup> Time required to transition from  $V_{OH}$  to  $V_{OL}$  or from  $V_{OL}$  to  $V_{OH}$ .

<sup>[5]</sup> Guarantees HPD\_SINK is LOW when no display is plugged in.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

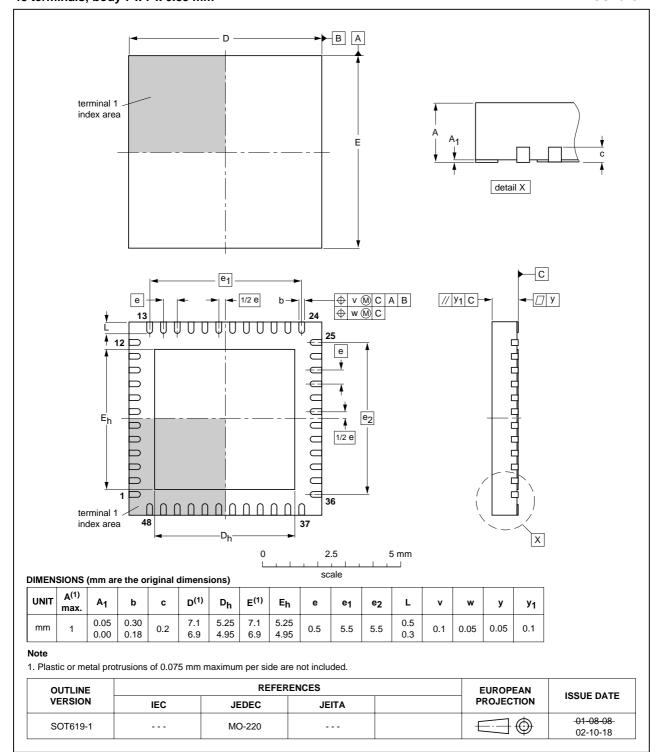

### 10. Package outline

HVQFN48: plastic thermal enhanced very thin quad flat package; no leads; 48 terminals; body 7 x 7 x 0.85 mm

SOT619-1

Fig 4. Package outline SOT619-1 (HVQFN48)

#### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 11. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365 "Surface mount reflow soldering description"*.

#### 11.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

#### 11.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 11.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

## Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 11.4 Reflow soldering

Key characteristics in reflow soldering are:

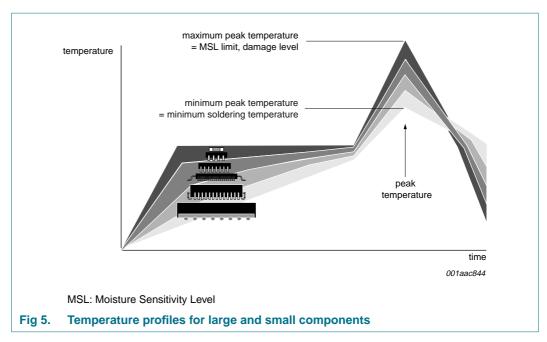

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 5</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 12 and 13

Table 12. SnPb eutectic process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |       |

|------------------------|---------------------------------|-------|

|                        | Volume (mm³)                    |       |

|                        | < 350                           | ≥ 350 |

| < 2.5                  | 235                             | 220   |

| ≥ 2.5                  | 220                             | 220   |

Table 13. Lead-free process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |

|------------------------|---------------------------------|-------------|--------|

|                        | Volume (mm³)                    |             |        |

|                        | < 350                           | 350 to 2000 | > 2000 |

| < 1.6                  | 260                             | 260         | 260    |

| 1.6 to 2.5             | 260                             | 250         | 245    |

| > 2.5                  | 250                             | 245         | 245    |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 5.

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

For further information on temperature profiles, refer to Application Note *AN10365* "Surface mount reflow soldering description".

### 12. Abbreviations

Table 14. Abbreviations

| Acronym              | Description                                 |

|----------------------|---------------------------------------------|

| CDM                  | Charged-Device Model                        |

| DDC                  | Data Display Channel                        |

| DVI                  | Digital Visual Interface                    |

| ESD                  | ElectroStatic Discharge                     |

| HBM                  | Human Body Model                            |

| HDMI                 | High-Definition Multimedia Interface        |

| HPD                  | Hot Plug Detect                             |

| I <sup>2</sup> C-bus | Inter-IC bus                                |

| I/O                  | Input/Output                                |

| TMDS                 | Transition Minimized Differential Signaling |

### 13. Revision history

Table 15. Revision history

| Document ID    | Release date           | Data sheet status              | Change notice             | Supersedes                    |

|----------------|------------------------|--------------------------------|---------------------------|-------------------------------|

| PTN3360A_2     | 20091008               | Product data sheet             | -                         | PTN3360A_1                    |

| Modifications: | Table 8 "Diff sentence | erential output characteristic | es for OUT_Dx signals", T | able note [7]: deleted second |

| PTN3360A_1     | 20090504               | Product data sheet             | -                         | -                             |

#### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 14. Legal information

#### 14.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 14.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 14.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Limiting values** — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

#### 14.4 Licenses

#### Purchase of NXP ICs with HDMI technology

Use of an NXP IC with HDMI technology in equipment that complies with the HDMI standard requires a license from HDMI Licensing LLC, 1060 E. Arques Avenue Suite 100, Sunnyvale CA 94085, USA, e-mail: admin@hdmi.org.

#### 14.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### 15. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### Enhanced HDMI/DVI level shifter with inverting 1.1 V HPD

### 16. Contents

| 1                      | General description                                       | . 1      |

|------------------------|-----------------------------------------------------------|----------|

| 2                      | Features                                                  |          |

| 2.1                    | High-speed TMDS level shifting                            | . 3      |

| 2.2                    | DDC level shifting                                        |          |

| 2.3                    | HPD level shifting                                        |          |

| 2.4                    | General                                                   |          |

| 3                      | Ordering information                                      |          |

| 4                      | Functional diagram                                        | . 4      |

| 5                      | Pinning information                                       | . 5      |

| 5.1                    | Pinning                                                   |          |

| 5.2                    | Pin description                                           | . 6      |

| 6                      | Functional description                                    | . 8      |

| 6.1                    | Enable and disable features                               |          |

| 6.1.1                  | Hot plug detect                                           |          |

| 6.1.2                  | Output Enable function (OE_N)                             |          |

| 6.1.3                  | DDC channel enable function (DDC_EN)                      |          |

| 6.1.4                  | Enable/disable truth table                                |          |

| 6.2<br>6.3             | Analog current reference                                  |          |

| ი.ა<br><b>7</b>        | •                                                         |          |

|                        | Limiting values                                           |          |

| 8                      | Recommended operating conditions                          |          |

| 8.1                    | Current consumption                                       |          |

| 9                      | Characteristics                                           |          |

| 9.1                    | Differential inputs                                       |          |

| 9.2<br>9.3             | Differential outputs                                      | 14<br>15 |

| 9.3<br>9.4             | HPD_SINK input, HPD_SOURCE_N output . OE_N, DDC_EN inputs | 15       |

| 9. <del>4</del><br>9.5 | DDC characteristics                                       | 15       |

| 10                     | Package outline                                           |          |

| 11                     | Soldering of SMD packages                                 |          |

| 11.1                   | Introduction to soldering                                 | 17       |

| 11.2                   | Wave and reflow soldering                                 | 17       |

| 11.3                   | Wave soldering                                            |          |

| 11.4                   | Reflow soldering                                          |          |

| 12                     | Abbreviations                                             | 19       |

| 13                     | Revision history                                          |          |

| 14                     | Legal information                                         |          |

| 14.1                   | Data sheet status                                         |          |

| 14.2                   | Definitions                                               |          |

| 14.3                   | Disclaimers                                               |          |

| 14.4                   | Licenses                                                  |          |

| 14.5                   | Trademarks                                                | 20       |

| 15                     | Contact information                                       | 20       |

| 16                     | Contents                                                  | 21       |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2009.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 8 October 2009

Document identifier: PTN3360A\_2

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP:

PTN3360ABS,518