# INTEGRATED CIRCUITS

Preliminary specification Supersedes data of 1999 Dec 20 2000 Jan 25

|                 | -           |

|-----------------|-------------|

|                 | $\cap \cap$ |

| ХA              | -1.5        |

| <i>_ / \/ \</i> |             |

| XA 16-bit microcontroller family                                              |

|-------------------------------------------------------------------------------|

| 32K/1024 OTP CAN transport layer controller                                   |

| 1 UART, 1 SPI Port, CAN 2.0B, 32 CAN ID filters, transport layer co-processor |

| FEATURES IN COMMON WITH XA-G3                    |

|--------------------------------------------------|

| XA-C3 SPECIFIC FEATURES                          |

| XA-C3 CAN AND CTL FEATURES                       |

| LOGIC SYMBOL AND BLOCK DIAGRAM                   |

| UPGRADING XA-G3 DESIGNS TO CAN                   |

|                                                  |

| 44-Pin PLCC Package                              |

| 44-pin LQFP package                              |

| LOGIC SYMBOL                                     |

| BLOCK DIAGRAM                                    |

| PIN DESCRIPTIONS                                 |

| SPECIAL FUNCTION REGISTERS                       |

| MEMORY-MAPPED REGISTERS                          |

| XA-C3 TIMER/COUNTERS                             |

| Timer 0 and Timer 1    12                        |

| New Enhanced Mode 0    13                        |

| Mode 1                                           |

| Mode 2                                           |

| Mode 3                                           |

| New Timer-Overflow Toggle Output                 |

| Timer T2                                         |

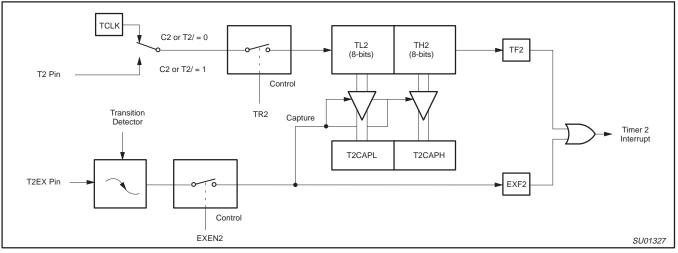

| Capture Mode                                     |

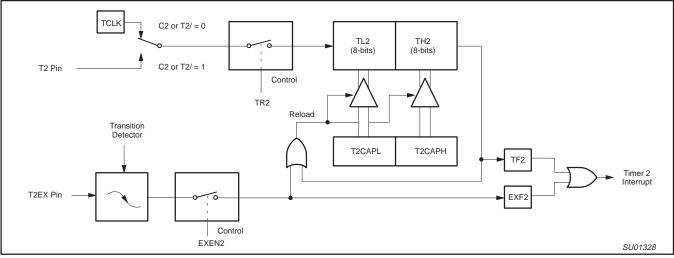

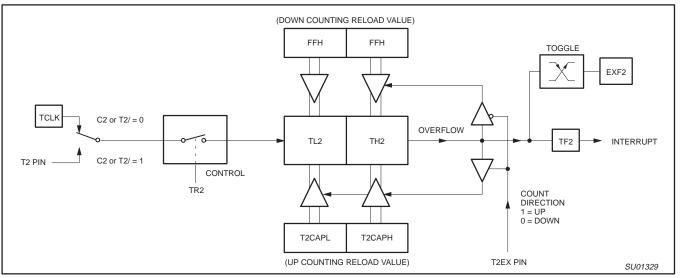

| Auto-Reload Mode (Up or Down Counter) 14         |

| Baud Rate Generator Mode                         |

| Programmable Clock-Out                           |

| WATCHDOG TIMER                                   |

| Watchdog Function                                |

| Watchdog Control Register (WDCON)                |

| Watchdog Detailed Operation                      |

| WDCON Register Bit Definitions                   |

| UART                                             |

| Serial Port Control Register                     |

| Transmit Interrupt Flag                          |

| 9-Bit Mode                                       |

| Bypassing Double-Buffering                       |

| CLOCKING SCHEME AND BAUD RATE GENERATION         |

| Clock Rates for all UART Modes                   |

| Baud Rates for UART Modes 0 and 2                |

| Baud Rate Calculations for UART Modes 0 and 2 20 |

| Baud Rates for UART Modes 1 and 3 20             |

| Baud Rate Calculations for UART Modes 1 and 3 20 |

| Baud Rate calculations for UART Mode 1 and 3:    |

| Using Timer 2 to Generate Baud Rates             |

| UART Interrupt Scheme                            |

| Multiprocessor Communications                    |

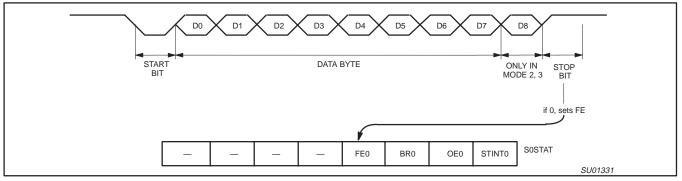

| Error Handling, Status Flags and Break Detect    |

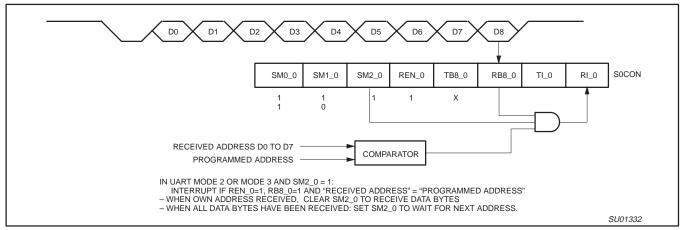

| Automatic Address Recognition                    |

| INPUT/OUTPUT PORT PIN CONFIGURATION              |

GENERAL DESCRIPTION .....

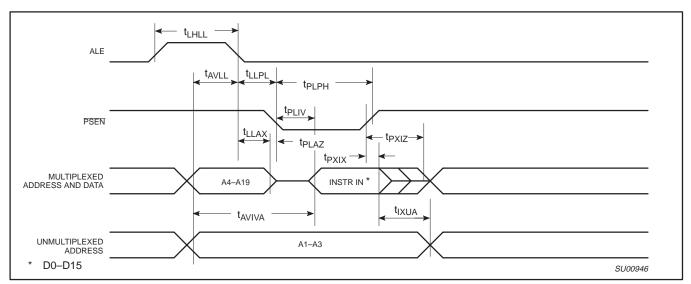

EXTERNAL BUS

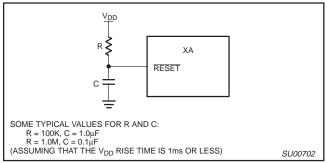

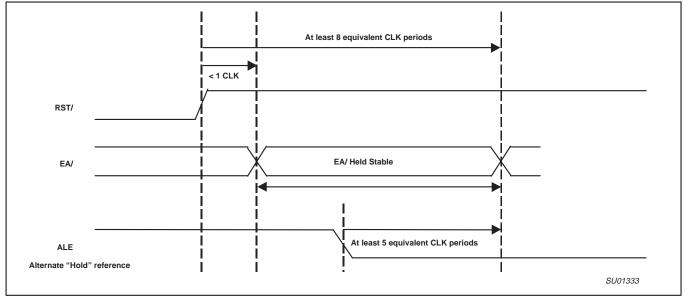

RESET .....

RST/Pin Properties and Requirements .....

Power-On Reset

Other Reset Effects .....

XA-C3

## XA 16-bit microcontroller family 32K/1024 OTP CAN transport layer controller 1 UART, 1 SPI Port, CAN 2.0B, 32 CAN ID filters, transport layer co-processor

| Reset Timing                                      | 24 |

|---------------------------------------------------|----|

| Power Reduction Modes                             | 24 |

| Interrupts                                        | 24 |

| Interrupt Types                                   | 24 |

| Interrupt Structures                              | 25 |

| Event Interrupt Handling                          | 25 |

| Interrupt Priority Details                        | 25 |

| ABSOLUTE MAXIMUM RATINGS                          | 26 |

| DC ELECTRICAL CHARACTERISTICS                     | 27 |

| AC ELECTRICAL CHARACTERISTICS                     | 28 |

| EPROM CHARACTERISTICS                             | 34 |

| Security Bits                                     | 34 |

| XA-C3 OVERVIEW                                    | 35 |

|                                                   | 35 |

| Definition of Terms                               | 35 |

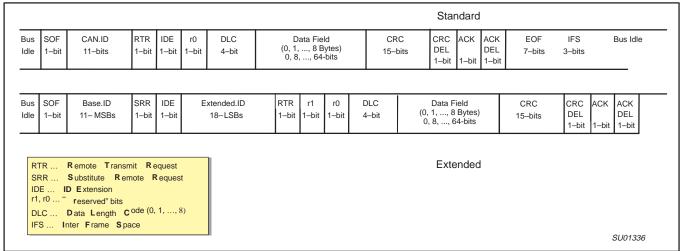

| Standard and Extended CAN Frames                  | 35 |

| Acceptance Filtering                              | 35 |

| Message Object                                    | 35 |

| CAN Arbitration ID                                | 35 |

| Screener ID                                       | 35 |

| Match ID                                          | 35 |

|                                                   |    |

| Mask                                              | 35 |

| CTL                                               | 35 |

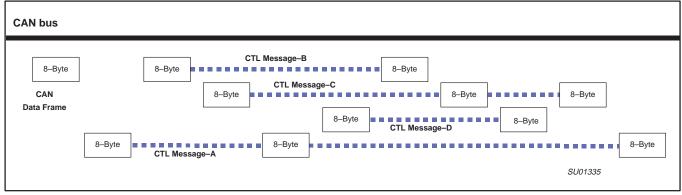

| Fragmented Message                                | 36 |

| Message Buffer                                    | 36 |

| MMR                                               | 36 |

| CTL/CAN Functionality of the XA-C3                | 36 |

| Message Objects / Message Management              | 36 |

| Acceptance Filtering                              | 36 |

| Message Storage                                   | 36 |

| Transmit Pre–Arbitration                          | 36 |

| Remote Frame Handling                             | 37 |

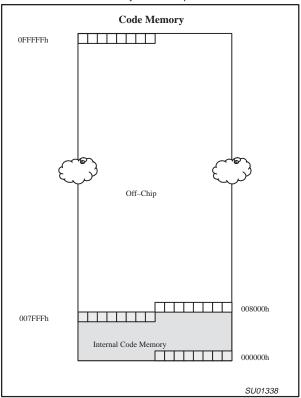

| MEMORY MAPS                                       | 37 |

| Data Memory Space                                 |    |

| Code Memory Space                                 |    |

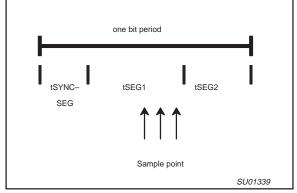

| CAN CORE BLOCK (CCB)                              | 37 |

| CAN Bus Timing                                    | 37 |

| CAN System Clock                                  | 37 |

| Samples Per Bit                                   | 37 |

| Location of Sample Point                          | 38 |

| Synchronization Jump Width                        | 38 |

| CANBTR: CAN Bus Timing Register                   | 38 |

| CAN Command and Status Registers                  | 38 |

| Two Modes in CAN Core Operation                   | 38 |

| CANCMR: CAN Command Register                      | 38 |

| CANSTR: CAN Status Register                       | 38 |

| CAN/CTL MESSAGE HANDLER                           | 39 |

| Message Objects                                   | 39 |

| Receive Message Objects and the Receive Process   | 39 |

| Acceptance Filtering                              | 39 |

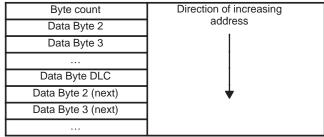

| Message Storage                                   | 41 |

| Message Assembly                                  | 42 |

| Transmit Message Objects and the Transmit Process | 45 |

| ······································            |    |

Pre–Arbitration Based on Priority (default mode) .....

XA-C3

## XA 16-bit microcontroller family 32K/1024 OTP CAN transport layer controller 1 UART, 1 SPI Port, CAN 2.0B, 32 CAN ID filters, transport layer co-processor

| Pre–Arbitration Based on Object Number                           | 45       |

|------------------------------------------------------------------|----------|

| Message Retrieval                                                | 46       |

| Transmission of Fragmented Messages                              | 46       |

| RTR Handling                                                     | 46       |

| Receiving an RTR Frame                                           | 46       |

| Transmitting an RTR Frame                                        | 46       |

| Data integrity issues                                            | 46       |

| Using the Semaphore Bits, SEM1 and SEM0                          | 46       |

| Avoiding Data Corruption for Transmit Message Objects            | 47       |

| OSEK, DEVICENET, AND CANOPEN FRAMES OF INTEREST                  | 47       |

| OSEK ConsecutiveFrame                                            | 47       |

| DeviceNet I/O Message                                            | 47       |

| CANopen Download Domain Segment Request                          | 47       |

| CANopen Auto–Acknowledge Tx Response to Download Domain Segment  | 47       |

| CANOPER Adito-Acknowledge TX Response to Download Domain Segment | 47<br>47 |

|                                                                  |          |

| Rx and Tx Message Complete Interrupts                            | 47       |

| Rx Buffer Full Interrupt                                         | 48       |

| Message Error Interrupt                                          | 49       |

| Tx Buffer Underflow                                              | 49       |

| Fragmentation Error                                              | 49       |

| Frame Error Interrupt                                            | 49       |

| Bus Error                                                        | 49       |

| Pre–Buffer Overflow                                              | 49       |

| Arbitration Lost                                                 | 50       |

| Error Warning                                                    | 50       |

| Error Passive                                                    | 50       |

| Bus Off                                                          | 50       |

| CAN Interrupt Registers                                          | 50       |

| CANINTFLG (CAN Interrupt Flag Register)                          | 50       |

| FESTR (Frame Error Status Register)                              | 51       |

| FEENR (Frame Error Enable Register)                              | 51       |

| MCIR (Message Complete Info Register)                            | 51       |

| MEIR (Message Error Info Register)                               | 51       |

| MCPLH (Message Complete Status Flags High)                       | 51       |

| MCPLL (Message Complete Status Flags Low)                        | 52       |

| TxERC (Tx Error Counter)                                         | 52       |

| RxERC (Rx Error Counter)                                         | 52       |

|                                                                  | 52       |

| EWLR (Error Warning Limit Register)                              | -        |

| ECCR (Error Code Capture Register)                               | 52       |

| ALCR (Arbitration Lost Capture Register)                         | 52       |

|                                                                  | 53       |

| POWER-DOWN AND IDLE MODE                                         | 53       |

| Background: XA Power–Down and Idle modes                         | 53       |

| XA-C3 Idle Mode                                                  | 53       |

| XA-C3 Power–Down Mode                                            | 53       |

| CAN Sleep Enable                                                 | 53       |

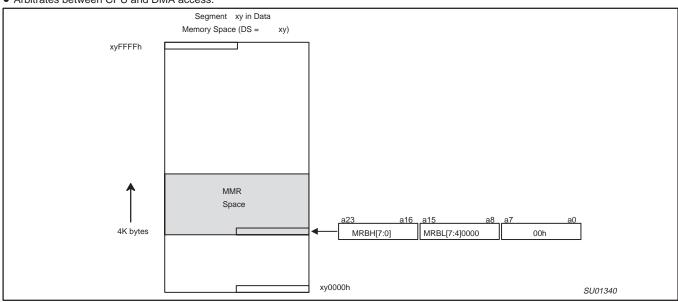

| MEMORY INTERFACE UNIT                                            | 54       |

| General Description                                              | 54       |

| Summary of features                                              | 54       |

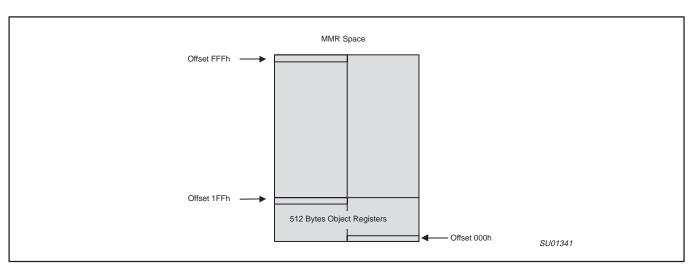

| Memory Mapped Registers (MMRs)                                   | 54       |

| Special Function Register MRBH                                   | 55       |

| Special Function Register MRBL                                   | 55       |

| On–Chip Message Buffer RAM (XRAM)                                | 55       |

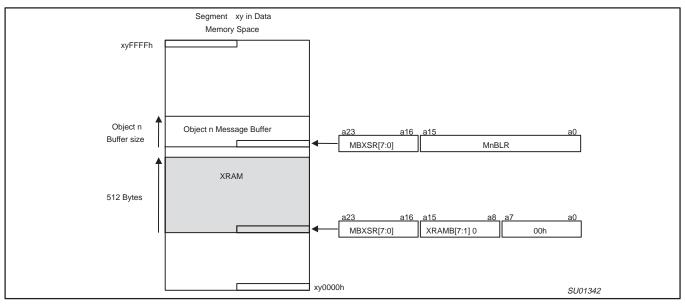

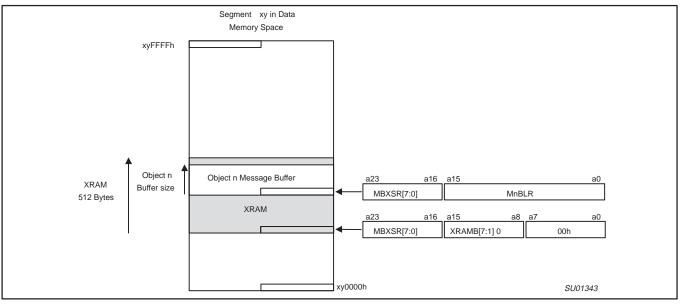

| MBXSR (Message Buffer and XRAM Segment Register)                 | 56       |

XA-C3

| XRAMB (XRAM Base Address)                                               | 57 |

|-------------------------------------------------------------------------|----|

| MIFCNTL (SFR)                                                           |    |

| MIFBTRL (Memory Interface Bus Timing Register Low, MMR)                 |    |

| MIFBTRH (Memory Interface Bus Timing Register High, MMR)Bus Arbitration |    |

| SPI Port                                                                | -  |

| SPICFG (MMR)                                                            |    |

| SPIDATA (MMR)                                                           |    |

| SPICS (MMR)                                                             |    |

| XA 16-bit microcontroller family                                              |

|-------------------------------------------------------------------------------|

| 32K/1024 OTP CAN transport layer controller                                   |

| 1 UART, 1 SPI Port, CAN 2.0B, 32 CAN ID filters, transport layer co-processor |

# LIST OF FIGURES

| Figure 1. 44-pin PLCC package                                                                                 |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Figure 2. 44-pin PLCC package                                                                                 |  |  |  |  |  |

| Logic Symbol                                                                                                  |  |  |  |  |  |

| Figure 4. XA-C3 Simplified Block Diagram                                                                      |  |  |  |  |  |

| Figure 5. System Configuration Register (SCR)                                                                 |  |  |  |  |  |

| Figure 6. Timer/Counter Mode Control (TMOD) Register                                                          |  |  |  |  |  |

| Figure 7. Timer/Counter Control (TCON) Register 13                                                            |  |  |  |  |  |

| Figure 8. Timer/Counter 2 Control (T2CON) Register                                                            |  |  |  |  |  |

| Figure 9. Timer 0 and 1 Extended Status (TSTAT)                                                               |  |  |  |  |  |

| Figure 10. Timer 2 Mode Control (T2MOD)                                                                       |  |  |  |  |  |

| Figure 11. Timer 2 in Capture Mode                                                                            |  |  |  |  |  |

| Figure 12. Timer 2 in Auto-Reload Mode (DCEN = 0)                                                             |  |  |  |  |  |

| Figure 13. Timer 2 Auto Reload Mode (DCEN = 1)                                                                |  |  |  |  |  |

| Figure 14. Watchdog Timer in XA-C3                                                                            |  |  |  |  |  |

| Figure 15. Serial Port Extended Status (S0STAT) Register                                                      |  |  |  |  |  |

| Figure 16. Serial Port Control (S0CON) Register                                                               |  |  |  |  |  |

| Figure 17. UART Framing Error Detection                                                                       |  |  |  |  |  |

| Figure 18. UART Multiprocessor Communication, Automatic Address Recognition                                   |  |  |  |  |  |

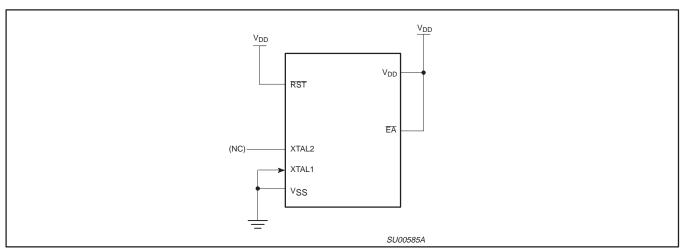

| Figure 19. Recommended Reset Circuit                                                                          |  |  |  |  |  |

| Figure 20. EA/ Timing Diagram                                                                                 |  |  |  |  |  |

| Figure 21. External PROGRAM Memory Read Cycle (ALE Cycle)                                                     |  |  |  |  |  |

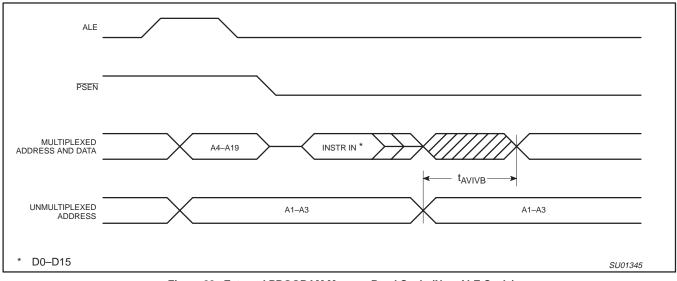

| Figure 22. External PROGRAM Memory Read Cycle (Non-ALE Cycle)                                                 |  |  |  |  |  |

| Figure 23. External DATA Memory Read Cycle (ALE Cycle)                                                        |  |  |  |  |  |

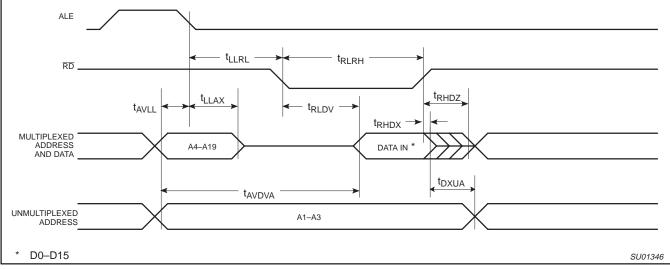

| Figure 24. External DATA Memory Write Cycle                                                                   |  |  |  |  |  |

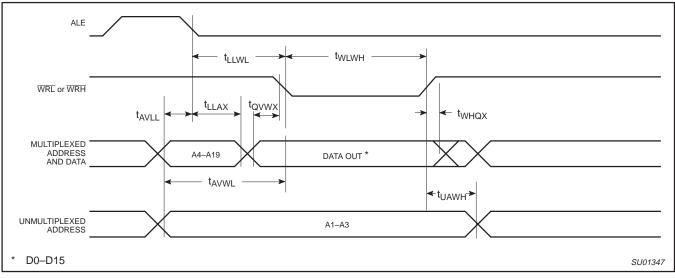

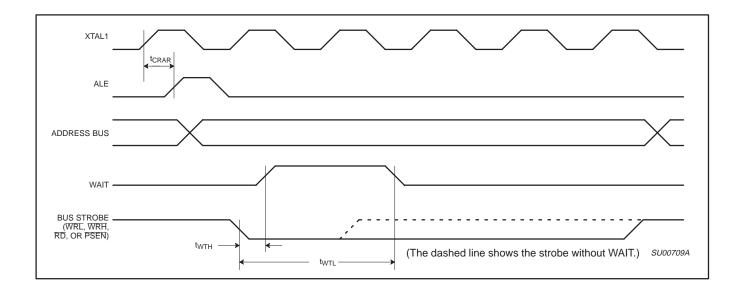

| Figure 25. WAIT Signal Timing                                                                                 |  |  |  |  |  |

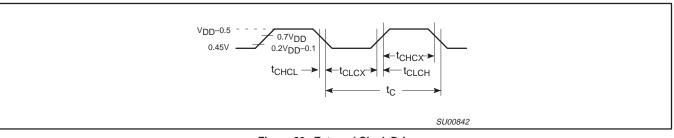

| Figure 26. External Clock Drive                                                                               |  |  |  |  |  |

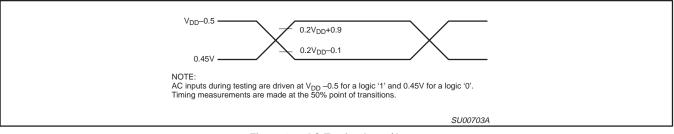

| Figure 27. AC Testing Input/Output                                                                            |  |  |  |  |  |

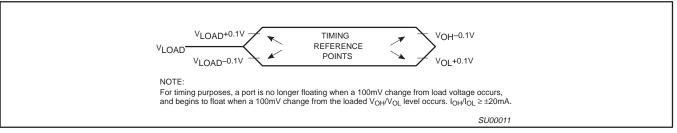

| Figure 28. Float Waveform                                                                                     |  |  |  |  |  |

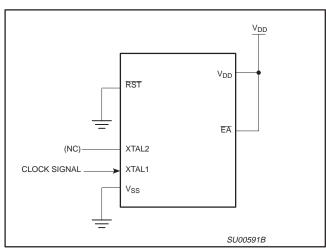

| Figure 29. IDD Test Condition, Active Mode                                                                    |  |  |  |  |  |

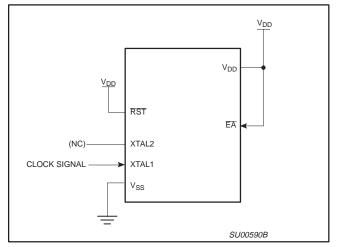

| Figure 30. IDD Test Condition, Idle Mode                                                                      |  |  |  |  |  |

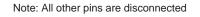

| Figure 31. IDD vs. Frequency at VDD = 5.0V                                                                    |  |  |  |  |  |

| Figure 32. Clock Signal Waveform for IDD Tests in Active and Idle Modes                                       |  |  |  |  |  |

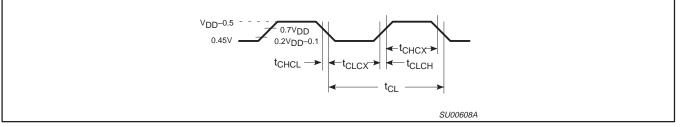

| Figure 33. IDD Test Condition, Power-Down Mode                                                                |  |  |  |  |  |

| Figure 34. Interleaved CAN Data Frames                                                                        |  |  |  |  |  |

| Figure 35. CAN Frame Formats                                                                                  |  |  |  |  |  |

| Figure 36. MMRs and XRAM mapped into Segment 00h                                                              |  |  |  |  |  |

| Figure 37. External Code Memory starts at 008000h                                                             |  |  |  |  |  |

| Figure 38. Memory Image for Non–Fragmented Messages                                                           |  |  |  |  |  |

| Figure 39. Retrieving the Screener ID for an Extended CAN Frame                                               |  |  |  |  |  |

|                                                                                                               |  |  |  |  |  |

|                                                                                                               |  |  |  |  |  |

| Figure 41. Memory Image for CAN Frame Buffering (FRAG = 1 and Prtcl1 Prtcl0 = 00)                             |  |  |  |  |  |

| Figure 42. Format for Storing the Tx Frame Info in MnMSKH                                                     |  |  |  |  |  |

| Figure 43. Formation of the MMR Base Address                                                                  |  |  |  |  |  |

| Figure 44. Detail of MMR space showing block of Message Object Registers                                      |  |  |  |  |  |

| Figure 45. Formation of the XRAM base address, with object n message buffer mapped to off-chip data memory 56 |  |  |  |  |  |

| Figure 46. Object n Message Buffer mapped into the on-chip XRAM                                               |  |  |  |  |  |

# LIST OF TABLES

| Table 1. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2. 44-pin PLCC package pin functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

| Table 3. 44-pin LQFP package pin functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4  |

| Table 4. Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7  |

| Table 5. Special Function Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9  |

| Table 6. Memory-Mapped Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

| Table 7. Timer 2 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15 |

| Table 8. Prescalar Select Values in WDCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

| Table 10. T2CON Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21 |

| Table 11. Prescaler Select for Timer Clock    Image: Clock Clo | 21 |

| Table 12. Vector Locations for UART in XA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21 |

| Table 13. Port Configuration Register Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

| Table 14. Interrupt Priority Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25 |

| Table 15. Exception and Trap Interrupt Vectors    Image: Control of the second s | 25 |

| Table 16. Event Interrupt Vectors    Interrupt Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26 |

| Table 17. Software Interrupt Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26 |

| Table 18. Absolute Maximum Ratings    Image:  | 26 |

| Table 19. DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 |

| Table 20. AC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28 |

| Table 21. PROGRAM Security Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

| Table 22. Message Object Register Functions for Tx and Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

| Table 23. Allowable Message Buffer Sizes    Image: Comparison of the second seco | 42 |

| Table 24. Format for storing the CANopen Acknowledge byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45 |

| Table 25. Error Codes for the Error Code Capture Register (ECCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

| Table 26. Arbitration Lost Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50 |

| Table 27. SFR Interrupt Enable/Priority Bit Positions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53 |

XA-C3

## **GENERAL DESCRIPTION**

The XA–C3 is a member of the Philips XA (eXtended Architecture) family of high–performance 16–bit single–chip microcontrollers. The XA–C3 combines an array of standard peripherals together with a PeliCAN CAN 2.0B engine and unique "Message Management" hardware to provide integrated support for most CAN Transport Layer (CTL) protocols such as DeviceNet, CANopen and OSEK. For additional details, refer to the *XA-C3 Overview* on page 35.

The XA architecture supports:

- Easy 16-bit migration from the 80C51 architecture.

- 16-bit fully static CPU with 24-bit addressed PROGRAM and DATA spaces.

- Twenty-one 16-bit CPU core registers capable of all arithmetic and logic operations while serving as memory pointers.

- An enhanced orthogonal instruction set tailored for high–level support of the C language.

- Multi-tasking and direct real-time executive support.

- Low–power operation intrinsic to the XA architecture includes Power–Down and Idle modes.

## FEATURES IN COMMON WITH XA-G3

- Pin–compatibility (CAN RxD and CAN TxD use the XA-G3 NC pins).

- 32K bytes of on-chip EPROM PROGRAM memory (see Table 1).

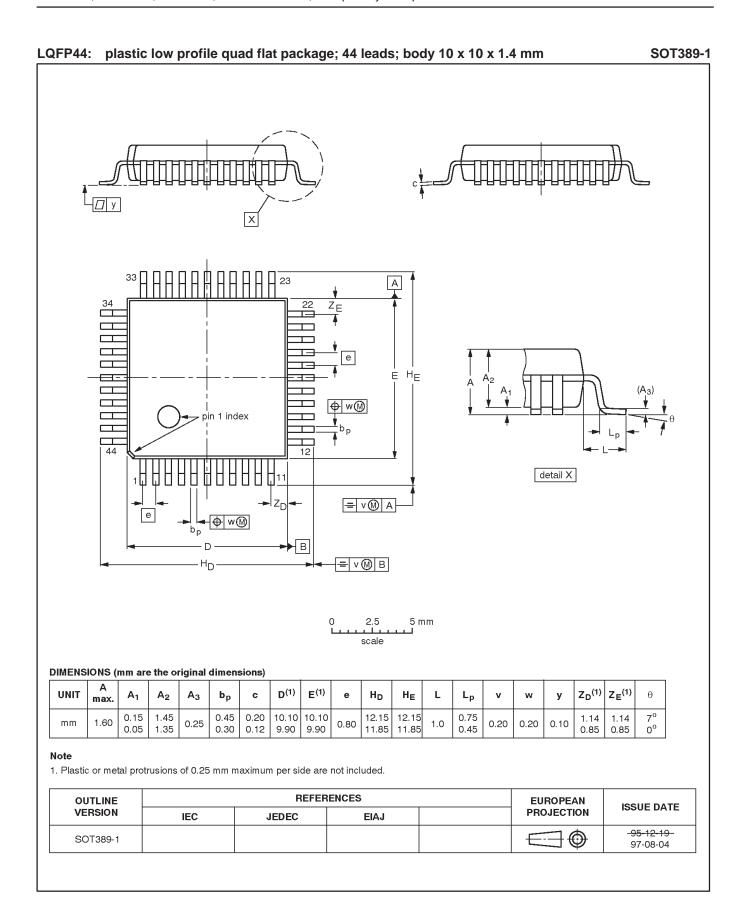

- 44-pin PLCC (Figure 1 and Table 2) and 44-pin LQFP (Figure 2 and Table 3) packages.

- Commercial (0 to 70<sup>o</sup>C) and Industrial (-40 to 85<sup>o</sup>C) ranges.

- Supports off-chip addressing of PROGRAM and DATA memory up to 1 megabyte each (20 address lines).

- Three standard counter/timers (T0, T1, and T2) with enhancements such as Auto Reload for PWM outputs.

- UART–0 with enhancements such as separate Rx and Tx interrupts, Break Detection, and Automatic Address Recognition.

- Watchdog with a secure WFEED1 / WFEED2 sequence.

- Four 8-bit I/O ports with 4 programmable output configurations per pin.

## **XA-C3 SPECIFIC FEATURES**

- 32 MHz operating frequency at 4.5 to 5.5V operation.

- One Serial Port Interface (SPI)

- 1024 bytes of on-chip DATA RAM.

- 42 vectored interrupts. These include 13 maskable Events, 7 Software interrupts, 6 Exceptions, 16 software Traps, segmented DATA memory, multiple User stacks, and banked registers to support rapid context switching.

- External interfacing via a 16-bit DATA bus width.

# **XA-C3 CAN AND CTL FEATURES**

- A PeliCAN CAN 2.0B engine from the SJA1000 Stand–alone CAN controller which supports 11– and 29–bit IDentifiers and the maximum CAN data rate (1 Mbps) and CAN Diagnostics.

- Hardware "Message Management" support for all major CTL protocols: DeviceNet, CANopen, OSEK.

- Automatic (hardware) assembly of Fragmented Messages via a Transport Layer Co-Processor. Concurrent assembly of up to 32 separate interleaved Fragmented Messages

- 32 CAN Transport Layer (CTL) Message Objects are modelled as a FullCAN Object Superset.

- 32 separate filters/screeners (one per Message Object), each allowing a 30-bit ID Match and full 29-bit Mask (i.e., each filter/screener represents a unique Group address).

- Each Message Object can be configured as Receive or Transmit.

- A separate message buffer is associated with each CTL Message Object. 32 message buffers are located in XRAM and managed by 32 DMA channels. Message buffer size for each Message Object is independently configurable in length (from 2 to 256 bytes).

- For single-chip systems there is a 512-byte (on-chip) XRAM message buffer, independent of the 1K on-chip DATA RAM, which is extendable (off-chip) to 8K bytes (i.e., 32 Message Objects that can be up to 256 bytes each).

# LOGIC SYMBOL AND BLOCK DIAGRAM

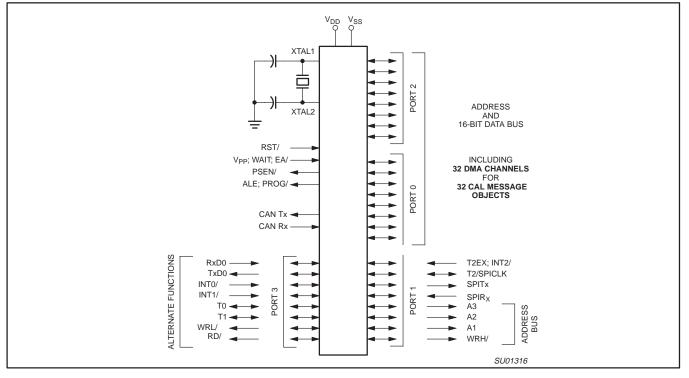

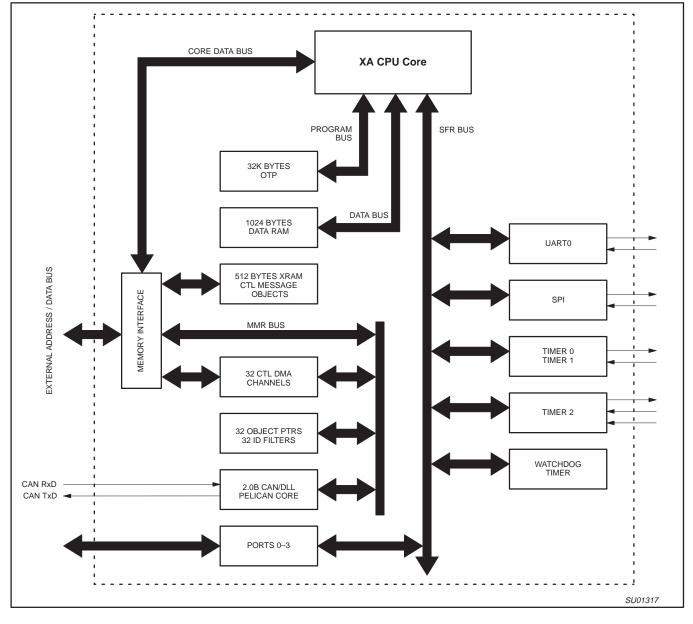

Refer to Figure 3 for the logic symbol for the XA-C3 and to Figure 4 for a simplified block diagram representation.

## **UPGRADING XA-G3 DESIGNS TO CAN**

- XA-G3 NC pins are XA-C3 CAN RxD and CAN TxD pins.

- XA-G3 UART-1 is replaced by a Serial Port Interface (SPI)

- XA-C3 software must never write to the BCR register

- XA-C3 software must initialize BTRH and BTRL with 00h

XA-C3

# **ORDERING INFORMATION**

## Table 1. Ordering Information

| XA–C3 Type &<br>Part Number | Temperature Range<br>(degrees C) | Package Description       | Operating Frequency<br>(MHz) | Drawing Number |

|-----------------------------|----------------------------------|---------------------------|------------------------------|----------------|

| OTP                         |                                  |                           |                              |                |

| PXAC37KBBD                  | 0 to +70                         | Low Profile PQFP [LQFP44] | 32                           | SOT389–1       |

| PXAC37KBA                   | 0 to +70                         | PLCC [PLCC44]             | 32                           | SOT187-2       |

| PXAC37KFBD                  | -40 to +85                       | Low Profile PQFP [LQFP44] | 32                           | SOT389–1       |

| PXAC37KFA                   | -40 to +85                       | PLCC [PLCC44]             | 32                           | SOT187-2       |

XA-C3

# **PIN CONFIGURATIONS**

# 44-Pin PLCC Package

Figure 1. 44-pin PLCC package

| Table 2. | 44-pin | PLCC | package | pin | functions |

|----------|--------|------|---------|-----|-----------|

|----------|--------|------|---------|-----|-----------|

| Pin Function (see Note) |                    | Pin | Function (see Note) |

|-------------------------|--------------------|-----|---------------------|

| 1                       | V <sub>SS</sub>    | 23  | V <sub>DD</sub>     |

| 2                       | P1.0 ; WRH/        | 4   | P2.0 ; A12D8        |

| 3                       | P1.1 ; A1          | 25  | P2.1 ; A13D9        |

| 4                       | P1.2 ; A2          | 26  | P2.2 ; A14D10       |

| 5                       | P1.3 ; A3          | 27  | P2.3 ; A15D11       |

| 6                       | P1.4 ; SPIRx       | 28  | P2.4 ; A16D12       |

| 7                       | P1.5 ; SPITx       | 29  | P2.5 ; A17D13       |

| 8                       | P1.6 ; T2 ; SPICLK | 30  | P2.6 ; A18D14       |

| 9                       | P1.7 ; T2EX        | 31  | P2.7 ; A19D15       |

| 10                      | RST/               | 32  | PSEN/               |

| 11                      | P3.0 ; RxD0        | 33  | ALE ; PROG/         |

| 12                      | CAN RxD            | 34  | CAN TxD             |

| 13                      | P3.1 ; TxD0        | 35  | EAI ; Vpp ; WAIT    |

| 14                      | P3.2 ; INT0/       | 36  | P0.7 ; A11D7        |

| 15                      | P3.3 ; INT1/       | 37  | P0.6 ; A10D6        |

| 16                      | P3.4 ; T0          | 38  | P0.5 ; A9D5         |

| 17                      | P3.5 ; T1          | 39  | P0.4 ; A8D4         |

| 18                      | P3.6 ; WRL/        | 40  | P0.3 ; A7D3         |

| 19                      | P3.7 ; RD/         | 41  | P0.2 ; A6D2         |

| 20                      | XTAL2              | 42  | P0.1 ; A5D1         |

| 21                      | XTAL1              | 43  | P0.0 ; A4D0         |

| 22                      | V <sub>SS</sub>    | 44  | V <sub>DD</sub>     |

NOTE:

1. All active-low signals are indicated by a "I" symbol

XA-C3

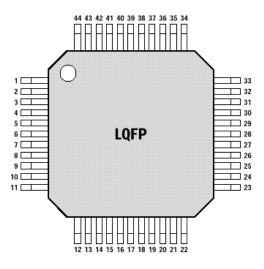

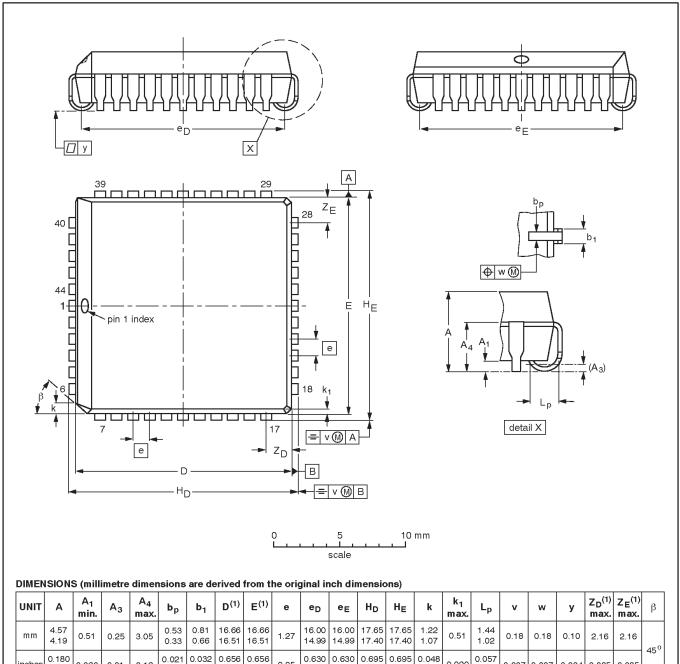

## 44-pin LQFP package

Figure 2. 44-pin PLCC package

# Table 3. 44-pin LQFP package pin functions

| Pin | Function (see Note) | Pin | Function (see Note) |

|-----|---------------------|-----|---------------------|

| 1   | P1.5 ; SPITx        | 23  | P2.5 ; A17D13       |

| 2   | P1.6 ; T2 ; SPICLK  | 4   | P2.6 ; A18D14       |

| 3   | P1.7 ; T2EX         | 25  | P2.7 ; A19D15       |

| 4   | RST/                | 26  | PSEN/               |

| 5   | P3.0 ; RxD0         | 27  | ALE ; PROG/         |

| 6   | CAN RxD             | 28  | CAN TxD             |

| 7   | P3.1 ; TxD0         | 29  | EA/ ; Vpp ; WAIT    |

| 8   | P3.2 ; INT0/        | 30  | P0.7 ; A11D7        |

| 9   | P3.3 ; INT1/        | 31  | P0.6 ; A10D6        |

| 10  | P3.4 ; T0           | 32  | P0.5 ; A9D5         |

| 11  | P3.5 ; T1           | 33  | P0.4 ; A8D4         |

| 12  | P3.6 ; WRL/         | 34  | P0.3 ; A7D3         |

| 13  | P3.7 ; RD/          | 35  | P0.2 ; A6D2         |

| 14  | XTAL2               | 36  | P0.1 ; A5D1         |

| 15  | XTAL1               | 37  | P0.0 ; A4D0         |

| 16  | VSS                 | 38  | VDD                 |

| 17  | VDD                 | 39  | VSS                 |

| 18  | P2.0 ; A12D8        | 40  | P1.0 ; WRH/         |

| 19  | P2.1 ; A13D9        | 41  | P1.1 ; A1           |

| 20  | P2.2 ; A14D10       | 42  | P1.2 ; A2           |

| 21  | P2.3 ; A15D11       | 43  | P1.3 ; A3           |

| 22  | P2.4 ; A16D12       | 44  | P1.4 ; SPIRx        |

NOTE:

1. All active-low signals are indicated by a "I" symbol

## LOGIC SYMBOL

Figure 3. Logic Symbol

## **BLOCK DIAGRAM**

Figure 4. XA-C3 Simplified Block Diagram

XA-C3

# **PIN DESCRIPTIONS**

## Table 4. Pin Descriptions

| MNEMONIC        | PIN NUI        | MBERS            | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|----------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | PLCC           | LQFP             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub> | 1, 22          | 16, 39           | I    | Ground: 0V Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |