**CMOS 8-BIT MICROCONTROLLER**

# LC87BG00 SERIES USER'S MANUAL

REV : 1.00

ON Semiconductor Digital Solution Division Microcontroller & Flash Business Unit

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

| Chapte | er 1 Overview 1-1                                                           |

|--------|-----------------------------------------------------------------------------|

| 1.1    | Overview ······ 1-1                                                         |

| 1.2    | Features ······ 1-1                                                         |

| 1.3    | Pinout 1-7                                                                  |

| 1.4    | System Block Diagram ······ 1-8                                             |

| 1.5    | Pin Functions ······ 1-9                                                    |

| 1.6    | On-chip Debugger Pin Connection Requirements1-10                            |

| 1.7    | Recommended Unused Pin Connections1-10                                      |

| 1.8    | Port Output Types ······1-10                                                |

| 1.9    | User Option Table1-11                                                       |

| 1.10   | Power Pin Treatment Recommendations (VDD1, VSS1)1-11                        |

| Chapte | er 2 Internal Configuration 2-1                                             |

| 2.1    | Memory Space 2-1                                                            |

| 2.2    | Program Counter (PC) 2-1                                                    |

| 2.3    | Program Memory (ROM) 2-2                                                    |

| 2.4    | Internal Data Memory (RAM)                                                  |

| 2.5    | Accumulator/A Register (ACC/A)                                              |

| 2.6    | B Register (B)2-3                                                           |

| 2.7    | C Register (C) 2-4                                                          |

| 2.8    | Program Status Word (PSW) 2-4                                               |

| 2.9    | Stack Pointer (SP)2-5                                                       |

| 2.10   | Indirect Addressing Registers                                               |

| 2.11   | Addressing Modes2-6                                                         |

|        | 2.11.1 Immediate Addressing (#) ······2-6                                   |

|        | 2.11.2 Indirect Register Indirect Addressing ([Rn])2-7                      |

|        | 2.11.3 Indirect Register + C Register Indirect Addressing ([Rn,C])2-7       |

|        | 2.11.4 Indirect Register (R0) + Offset Value Indirect Addressing ([off])2-8 |

|        | 2.11.5 Direct Addressing (dst) ······ 2-8                                   |

|        | 2.11.6 ROM Table Look-up Addressing2-9                                      |

|        | 2.11.7 External Data Memory Addressing                                      |

| 2.12   | Wait Operation2-10                                                          |

| 2.1    | 2.1 Occurrence of Wait Operation 2-10                                       |

| 2.1    | 2.2 What is Wait Operation? 2-10                                            |

| Chapte |                                                                             |

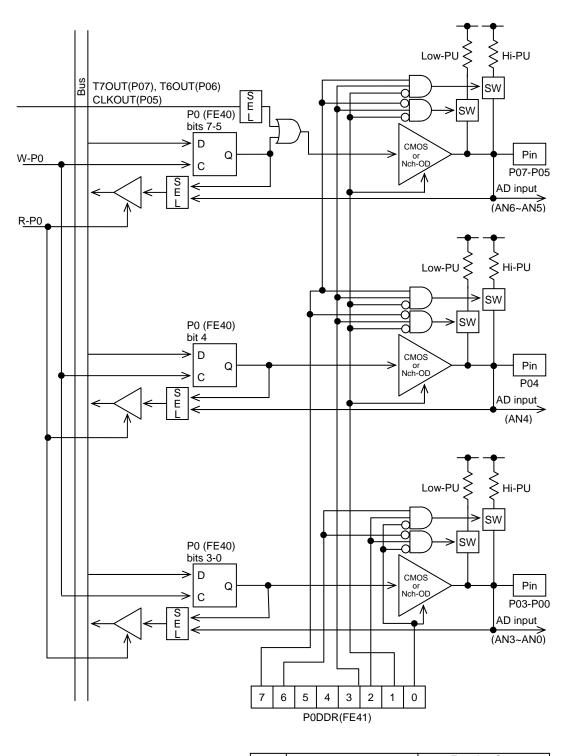

| 3.1    | Port 0 3-1                                                                  |

| 3.1    | .1 Overview                                                                 |

| 3.1.2   | Functions                                     |

|---------|-----------------------------------------------|

| 3.1.3   | Related Registers                             |

| 3.1.4   | Options                                       |

| 3.1.5   | HALT and HOLD Mode Operation                  |

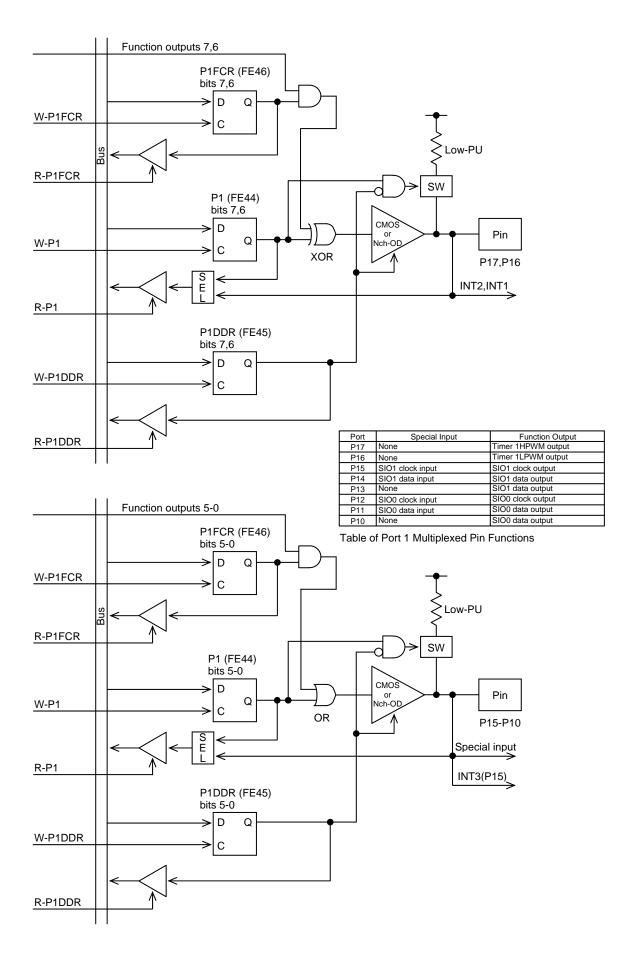

| 3.2 Po  | rt 1 3-5                                      |

| 3.2.1   | Overview ···································· |

| 3.2.2   | Functions                                     |

| 3.2.3   | Related Registers3-6                          |

| 3.2.4   | Options                                       |

| 3.2.5   | HALT and HOLD Mode Operation                  |

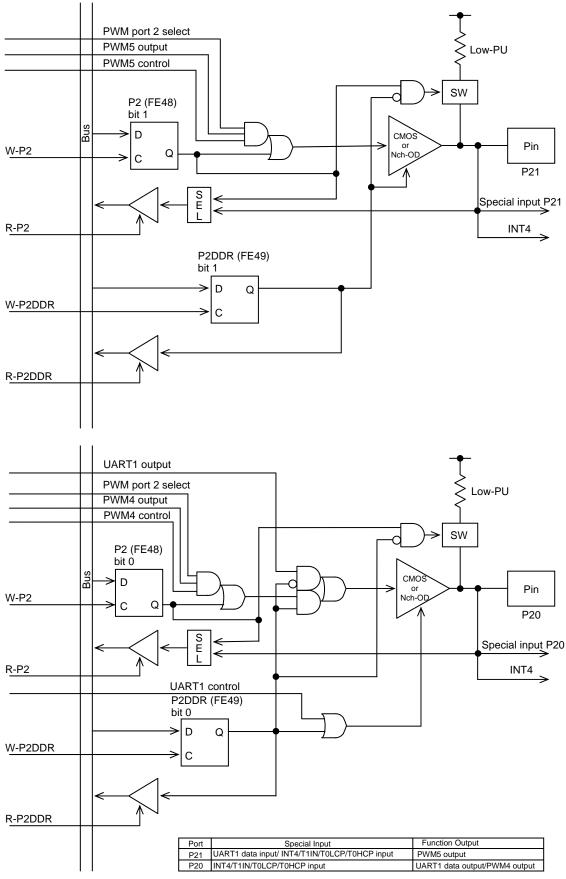

| 3.3 Po  | rt 23-13                                      |

| 3.3.1   | Overview                                      |

| 3.3.2   | Functions ······ 3-13                         |

| 3.3.3   | Related Registers 3-14                        |

| 3.3.4   | Options                                       |

| 3.3.5   | HALT and HOLD Mode Operation                  |

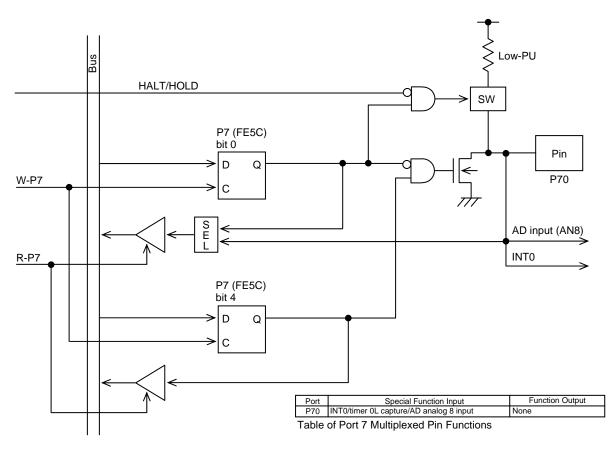

| 3.4 Po  | rt 73-17                                      |

| 3.4.1   | Overview                                      |

| 3.4.2   | Functions ······ 3-17                         |

| 3.4.3   | Related Registers ······ 3-18                 |

| 3.4.4   | Options                                       |

| 3.4.5   | HALT and HOLD Mode Operation                  |

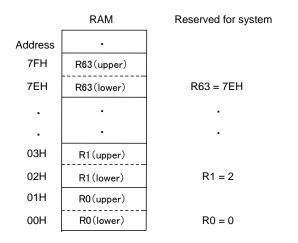

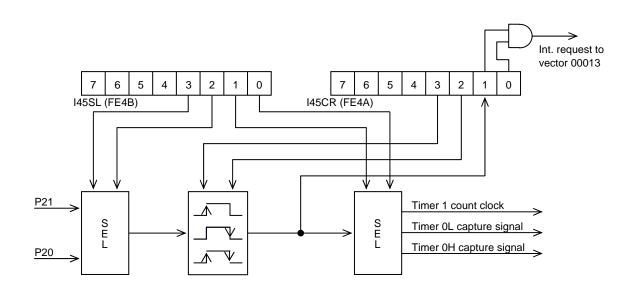

| 3.5 Tir | ner/Counter 0 (T0)3-23                        |

| 3.5.1   | Overview                                      |

| 3.5.2   | Functions ······ 3-23                         |

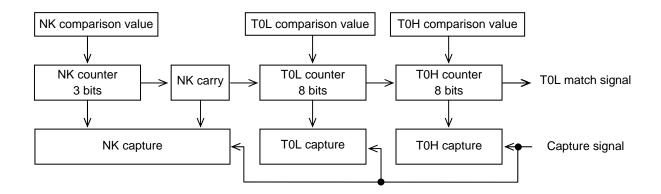

| 3.5.3   | Circuit Configuration                         |

| 3.5.4   | Related Registers ······ 3-29                 |

| 3.6 Hig | gh-speed Clock Counter3-32                    |

| 3.6.1   | Overview                                      |

| 3.6.2   | Functions ······ 3-32                         |

| 3.6.3   | Circuit Configuration                         |

| 3.6.4   | Related Registers 3-34                        |

| 3.7 Tir | ner/Counter 1 (T1)3-36                        |

| 3.7.1   | Overview                                      |

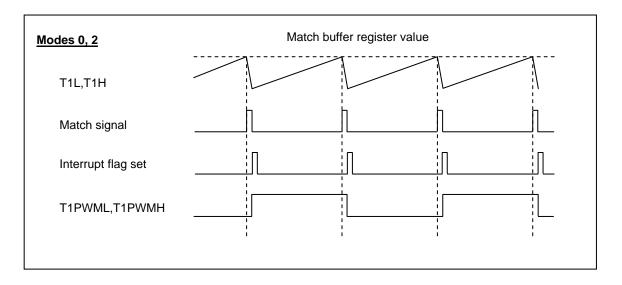

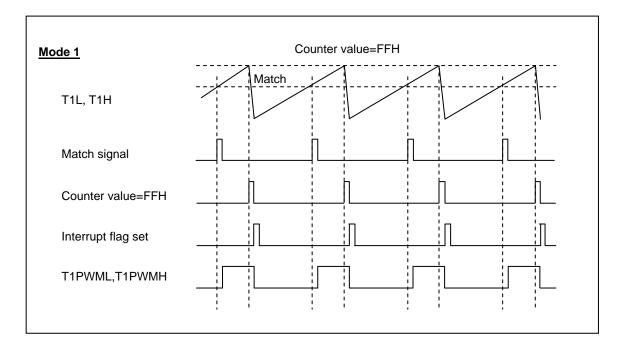

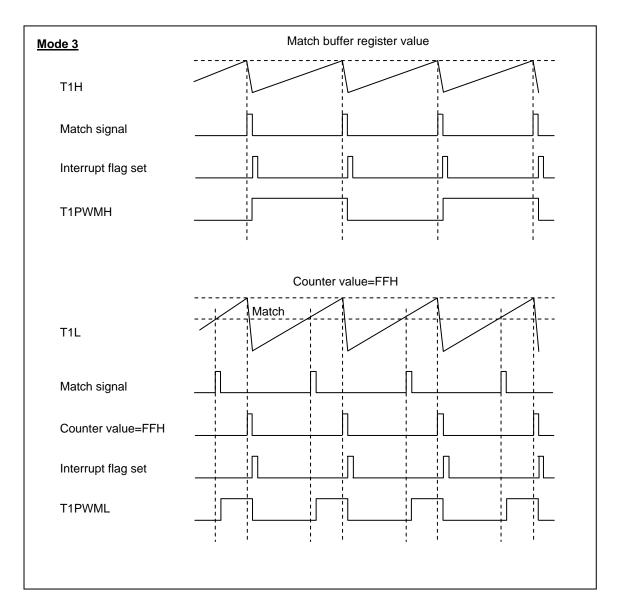

| 3.7.2   | Functions ······ 3-36                         |

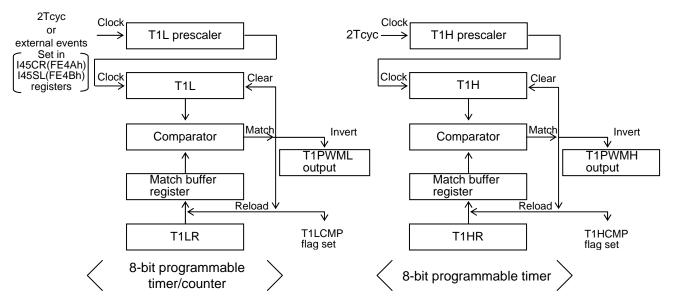

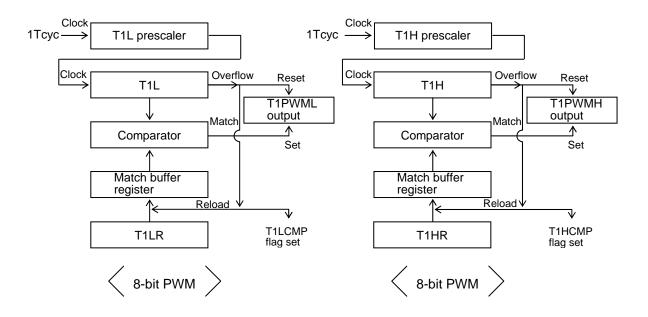

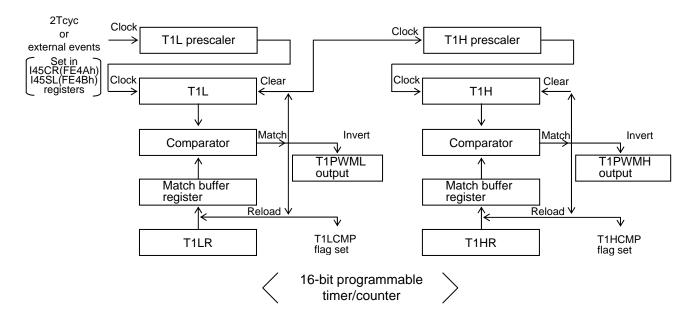

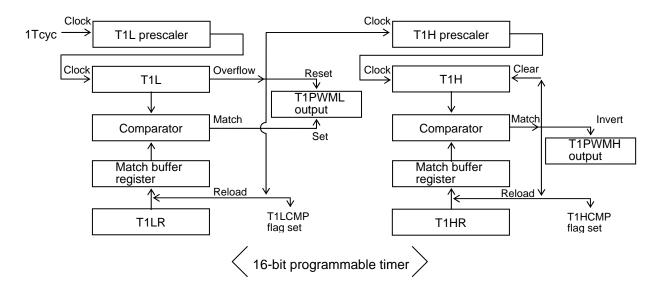

| 3.7.3   | Circuit Configuration                         |

| 3.7.4   | Related Registers 3-43                        |

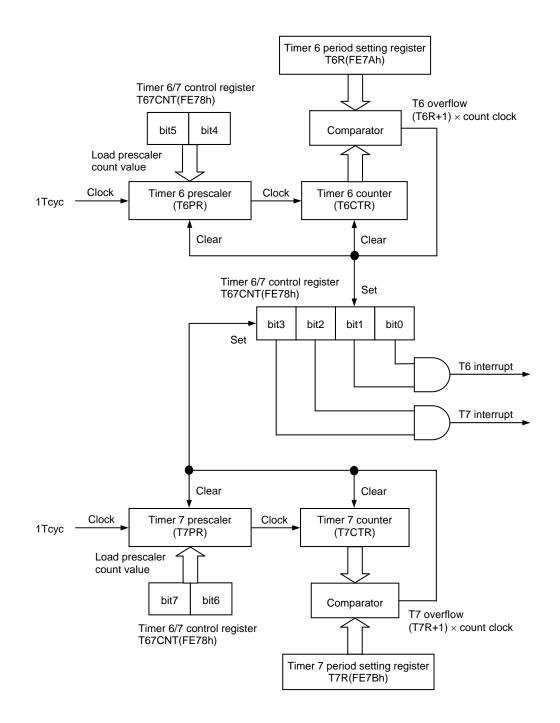

| 3.8 Timers 6 and 7 (T6, T7)                              |

|----------------------------------------------------------|

| 3.8.1 Overview                                           |

| 3.8.2 Functions                                          |

| 3.8.3 Circuit Configuration                              |

| 3.8.4 Related Registers 3-51                             |

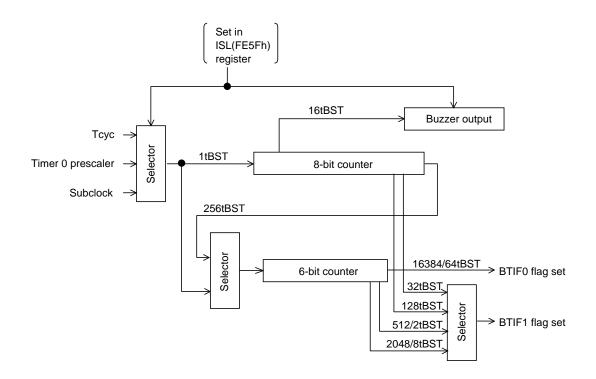

| 3.9 Base Timer (BT)                                      |

| 3.9.1 Overview                                           |

| 3.9.2 Functions                                          |

| 3.9.3 Circuit Configuration 3-54                         |

| 3.9.4 Related Registers 3-55                             |

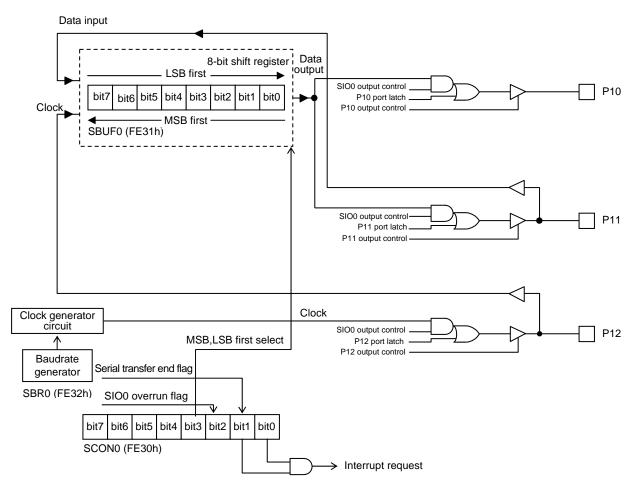

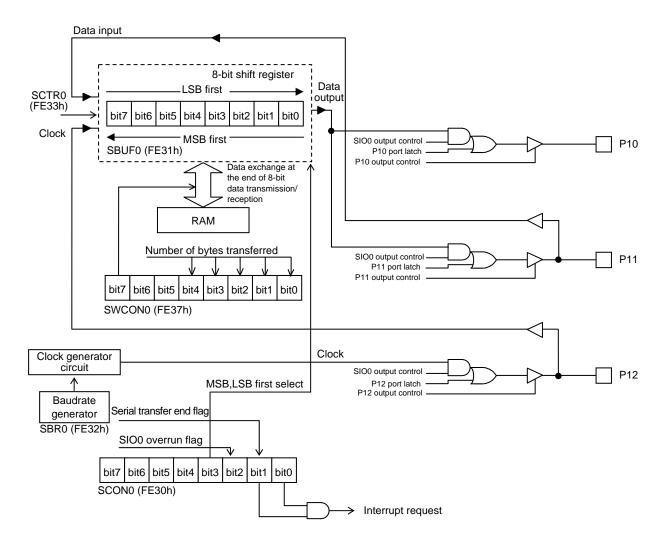

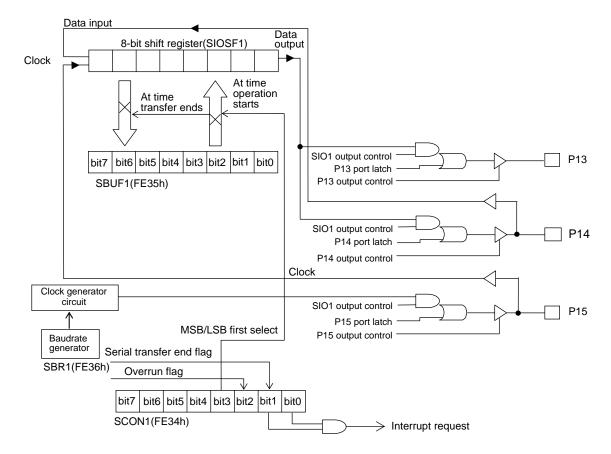

| 3.10 Serial Interface 0 (SIO0)                           |

| 3.10.1 Overview                                          |

| 3.10.2 Functions                                         |

| 3.10.3 Circuit Configuration 3-58                        |

| 3.10.4 Related Registers                                 |

| 3.10.5 SIO0 Communication Examples 3-62                  |

| 3.10.6 SIO0 HALT Mode Operation 3-64                     |

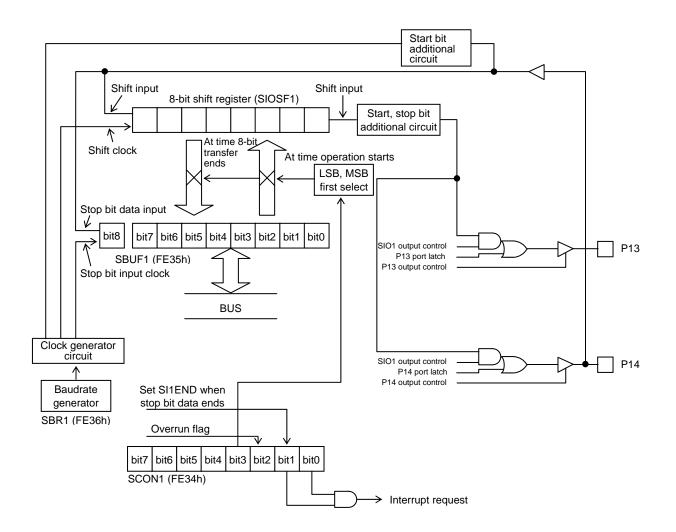

| 3.11 Serial Interface 1 (SIO1)                           |

| 3.11.1 Overview                                          |

| 3.11.2 Functions                                         |

| 3.11.3 Circuit Configuration                             |

| 3.11.4 SIO1 Communication Examples                       |

| 3.11.5 Related Registers                                 |

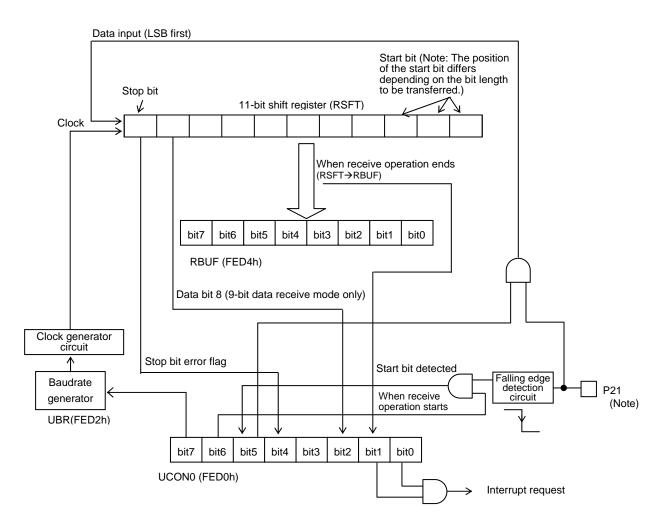

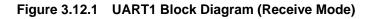

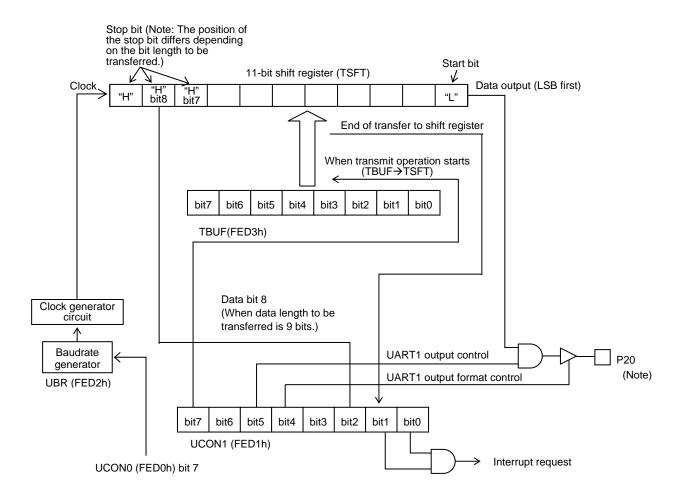

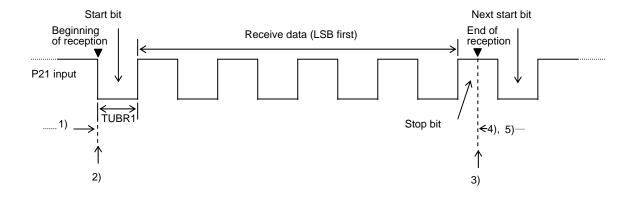

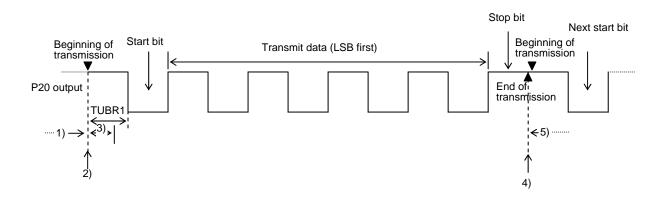

| 3.12 Asynchronous Serial Interface 1 (UART1)             |

| 3.12.1 Overview                                          |

| 3.12.2 Functions                                         |

| 3.12.3 Circuit Configuration 3-78                        |

| 3.12.4 Related Registers                                 |

| 3.12.5 UART1 Continuous Communication Operation Examples |

| 3.12.6 UART1 HALT Mode Operation                         |

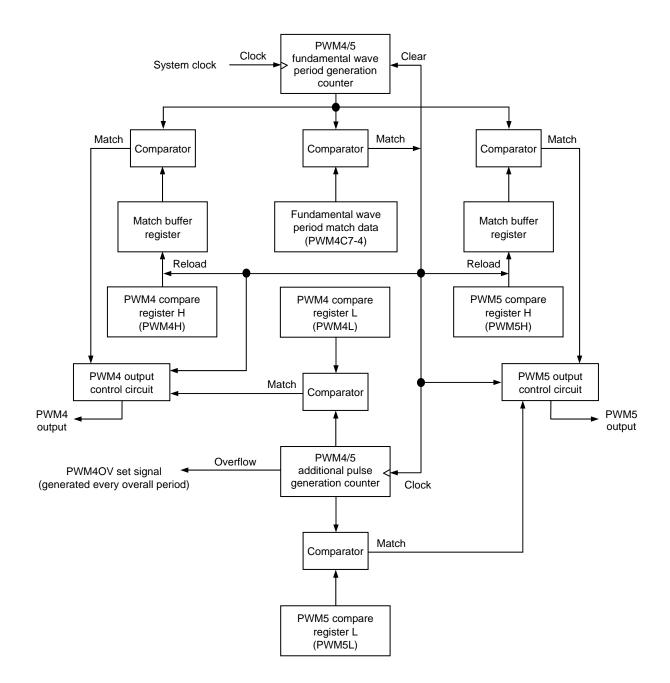

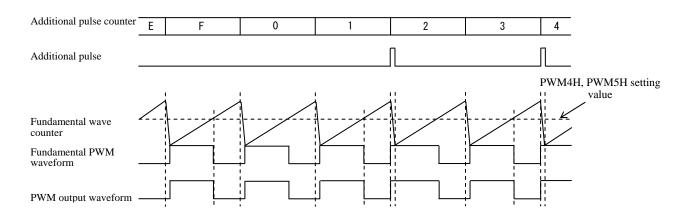

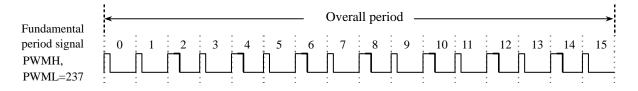

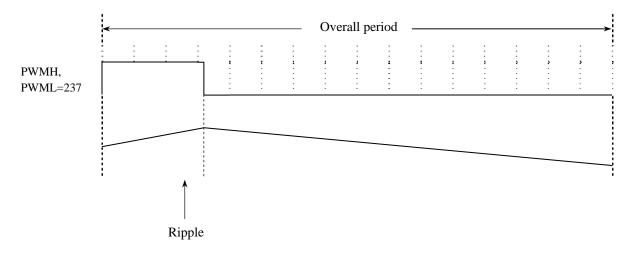

| 3.13 PWM4/PWM5                                           |

| 3.13.1 Overview                                          |

| 3.13.2 Functions                                         |

| 3.13.3 Circuit Configuration 3-89                        |

| 3.13.4 Related Registers                                 |

| 3.13.5 Setting Up the PWM4 and PWM5 Output Ports         |

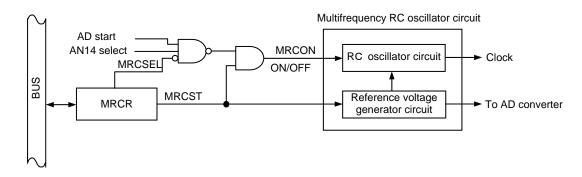

| 3.14 AD Converter (ADC12)                                |

| 3.14.1    | Overview                                                   |

|-----------|------------------------------------------------------------|

| 3.14.2    | Functions3-97                                              |

| 3.14.3    | Circuit Configuration 3-98                                 |

| 3.14.4    | Related Registers 3-98                                     |

| 3.14.5    | AD Conversion Example                                      |

| 3.14.6    | Hints on the Use of the ADC······3-103                     |

| 3.15 Re   | eference Voltage Generator Circuit (VREF17)······ 3-105    |

| 3.15.1    | Overview                                                   |

| 3.15.2    | Functions3-105                                             |

| 3.15.3    | 5                                                          |

| 3.15.4    | Related Registers3-106                                     |

| 3.15.5    | Using the Reference Voltage                                |

|           |                                                            |

| Chapter 4 |                                                            |

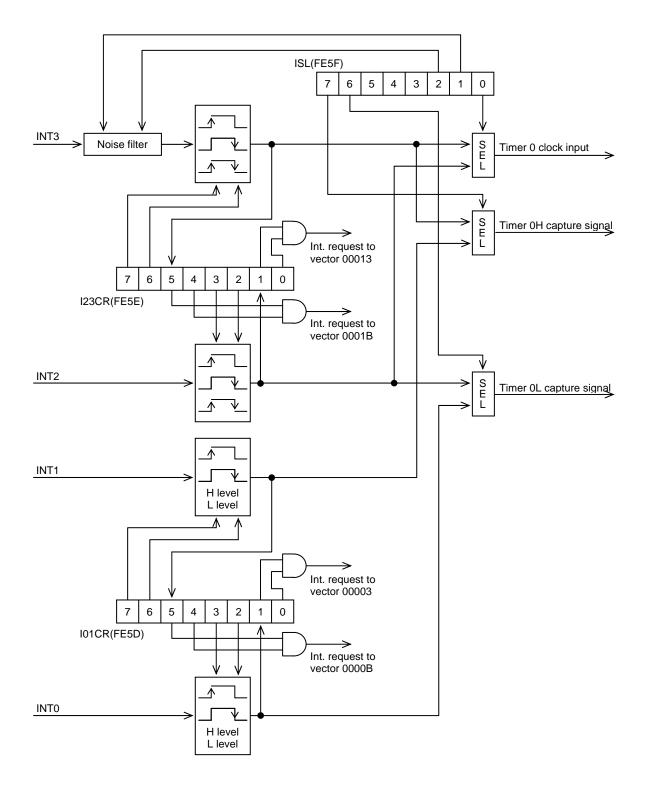

| 4.1 Inte  | errupt Function 4-1                                        |

| 4.1.1     | Overview4-1                                                |

| 4.1.2     | Functions4-1                                               |

| 4.1.3     | Circuit Configuration                                      |

| 4.1.4     | Related Registers4-3                                       |

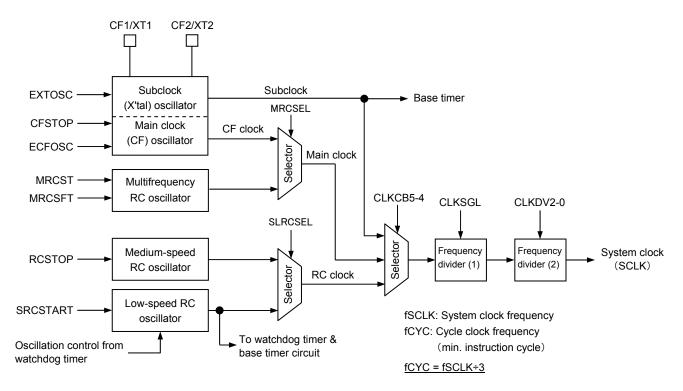

| 4.2 Sys   | stem Clock Generator Function 4-5                          |

| 4.2.1     | Overview4-5                                                |

| 4.2.2     | Functions4-5                                               |

| 4.2.3     | Circuit Configuration                                      |

| 4.2.4     | Related Registers 4-8                                      |

| 4.2.5     | Example of Switching the CF Oscillator Amplifier Size 4-13 |

| 4.3 CF    | Oscillation (Main Clock) Monitoring Function4-14           |

| 4.3.1     | Overview                                                   |

| 4.3.2     | Functions 4-14                                             |

| 4.3.3     | Circuit Configuration 4-14                                 |

| 4.3.4     | Related Register 4-14                                      |

| 4.3.5     | CF Oscillation Monitoring Example 4-15                     |

| 4.4 Sta   | ndby Function ······4-16                                   |

| 4.4.1     | Overview 4-16                                              |

| 4.4.2     | Functions 4-16                                             |

| 4.4.3     | Related Registers 4-17                                     |

|           | set Function4-21                                           |

| 4.5.1     | Overview                                                   |

| 4.5.2   | Functions 4-21                                                   |

|---------|------------------------------------------------------------------|

| 4.5.3   | Reset State 4-22                                                 |

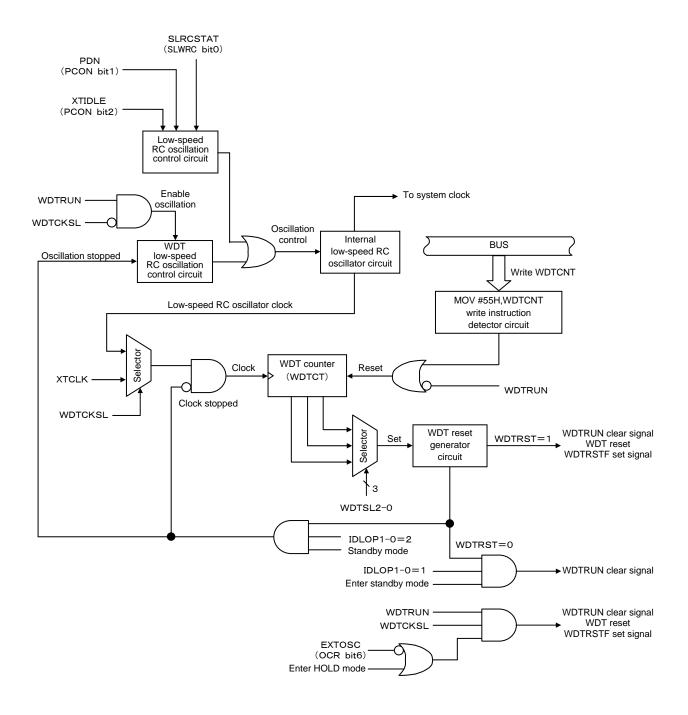

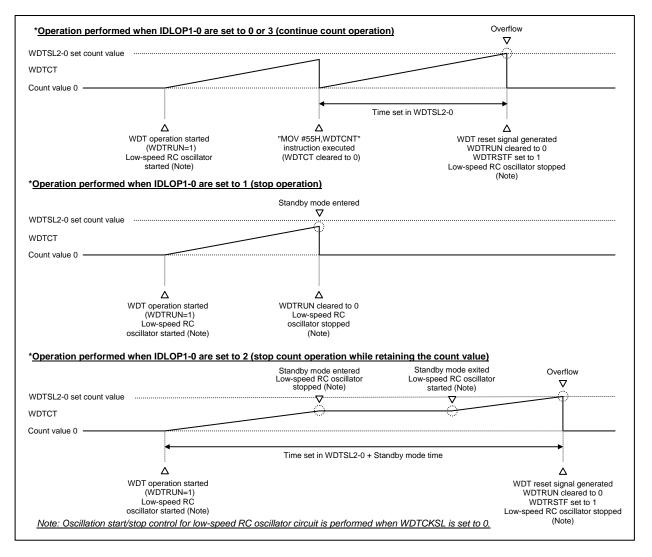

| 4.6 Wa  | atchdog Timer (WDT) ······4-23                                   |

| 4.6.1   | Overview 4-23                                                    |

| 4.6.2   | Functions 4-23                                                   |

| 4.6.3   | Circuit Configuration 4-24                                       |

| 4.6.4   | Related Registers 4-26                                           |

| 4.6.5   | Using the Watchdog Timer 4-28                                    |

| 4.6.6   | Notes on the Use of the Watchdog Timer 4-29                      |

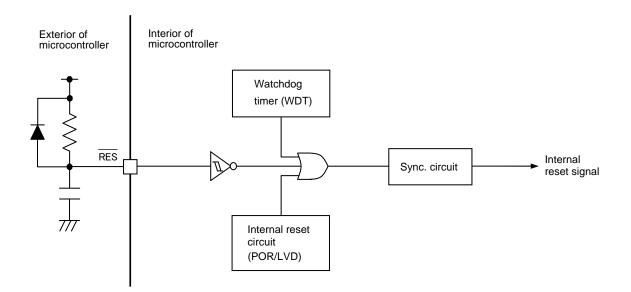

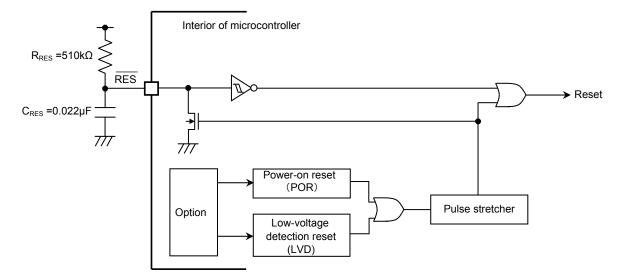

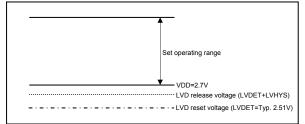

| 4.7 Int | ernal Reset Function ······4-30                                  |

| 4.7.1   | Overview 4-30                                                    |

| 4.7.2   | Functions 4-30                                                   |

| 4.7.3   | Circuit Configuration 4-30                                       |

| 4.7.4   | Options4-31                                                      |

| 4.7.5   | Sample Operating Waveforms of the Internal Reset Circuit         |

| 4.7.6   | Notes on the Use of the Internal Reset Circuit 4-34              |

| 4.7.7   | Notes to be Taken When Not Using the Internal Reset Circuit 4-36 |

|         |                                                                  |

# Appendixes

| Appendix-I   | Special Function Register (SFR) Map Al-(1-7)                  |

|--------------|---------------------------------------------------------------|

| Appendix-II  | Port Block Diagrams ······All-(1-7)                           |

| Appendix-III | LC872000/LC87B000 Series On-chip Debugger Pin Treatment Guide |

|              | AIII-(1-2)                                                    |

-6-

# 1. Overview

### 1.1 Overview

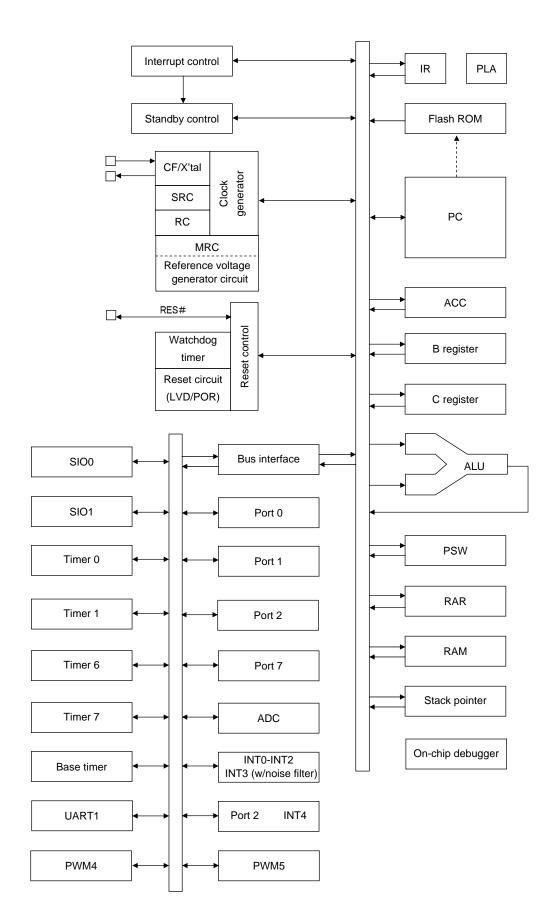

The LC87BG00 series is an 8-bit microcontroller that, centered around a CPU running at a minimum bus cycle time of 83.3 ns, integrates on a single chip a number of hardware features such as 8K-byte flash ROM (onboard programmable), 256-byte RAM, an on-chip debugger (flash ROM version only), two sophisticated 16-bit timers/counters (may be divided into 8-bit timers), two 8-bit timers with a prescaler, a base timer serving as a time-of-day clock, a synchronous SIO interface, an asynchronous/synchronous SIO interface, a UART interface (full duplex), two channels of multifrequency 12-bit PWM, a 12-bit 9-channel AD converter with 12-/8-bit resolution selector, a high-speed clock counter, a system clock frequency divider, internal high-accuracy oscillator circuits, a reference voltage generator circuit, an internal reset circuit, and 19-source 10-vector interrupt function.

### 1.2 Features

Flash ROM version

LC87FBG08A: 8192 × 8 bits

- Capable of onboard programming with a wide supply voltage range of 2.2 to 5.5V

- 128-byte block erase possible

Can be written in 2-byte units

- RAM

LC87FBG08A: 256 × 9 bits

- Minimum bus cycle time

- 83.3 ns (12 MHz, VDD=2.7 to 5.5 V)

- 100 ns (10 MHz, VDD=2.2 to 5.5 V)

- 250 ns ( 4 MHz, VDD=1.8 to 5.5 V)

Note: The bus cycle time here refers to the ROM read speed.

- Minimum instruction cycle time (Tcyc)

- 250 ns (12 MHz, VDD=2.7 to 5.5 V)

- 300 ns (10 MHz, VDD=2.2 to 5.5 V)

- 750 ns ( 4 MHz, VDD=1.8 to 5.5 V)

- Ports

- Normal withstand voltage I/O ports

Ports whose input/output can be specified in 1-bit units: Ports whose input/output can be specified in 4-bit units:

- Normal withstand voltage input port:

- Reset pin:

- · Power pins:

12 (P1n, P20, P21, P70, CF2/XT2) 8 (P0n) 1 (CF1/XT1)  $1 (\overline{\text{RES}})$ 2 (VSS1, VDD1)

- Timers

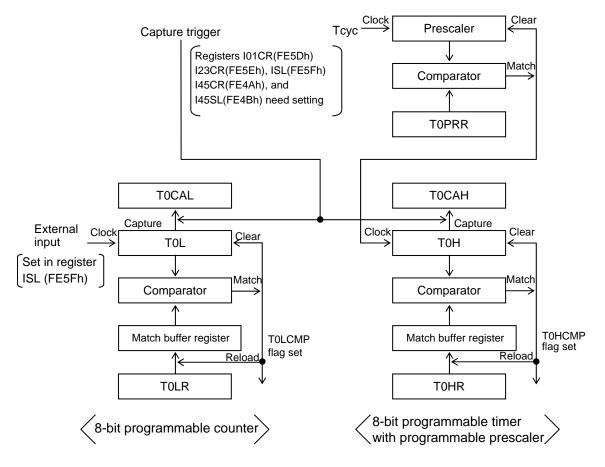

- Timer 0: 16-bit timer/counter with a capture register

- Mode 0: 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register) × 2 channels

- Mode 1: 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register) + 8-bit counter (with an 8-bit capture register)

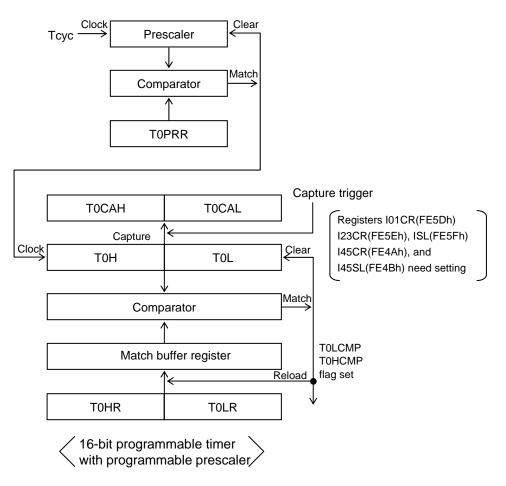

- Mode 2: 16-bit timer with an 8-bit programmable prescaler (with a 16-bit capture register)

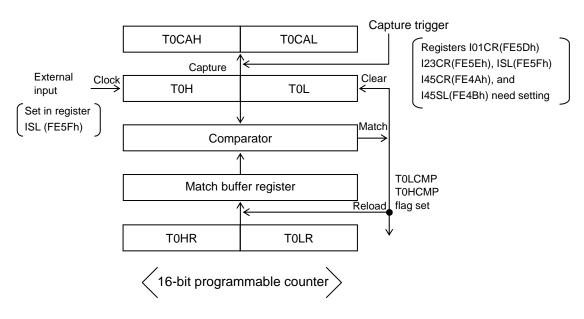

Mode 3: 16-bit counter (with a 16-bit capture register)

- Timer 1: 16-bit timer/counter that supports PWM/toggle output

- Mode 0: 8-bit timer with an 8-bit prescaler (with toggle output) + 8-bit timer/counter with an 8-bit prescaler (with toggle output)

- Mode 1: 8-bit PWM with an 8-bit prescaler  $\times$  2 channels

- Mode 2: 16-bit timer/counter with an 8-bit prescaler (with toggle output) (Toggle output also possible from the low-order 8 bits)

- Mode 3: 16-bit timer with an 8-bit prescaler (with toggle output) (The low-order 8 bits can be used as a PWM.)

- Timer 6: 8-bit timer with a 6-bit prescaler (with toggle output)

- Timer 7: 8-bit timer with a 6-bit prescaler (with toggle output)

- Base timer

- 1) The clock can be selected from among the subclock (32.768 kHz crystal oscillation), system clock, and timer 0 prescaler output.

- 2) Interrupts can be generated at five specified time intervals.

- 3) The base timer cannot be used when the CF oscillator circuit is selected.

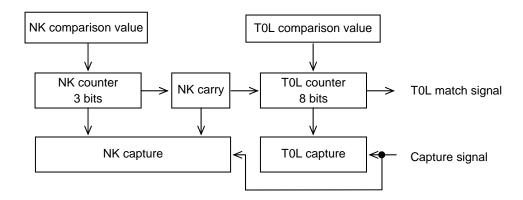

- High-speed clock counter

- 1) Capable of counting clocks with a maximum clock rate of 20 MHz (at a main clock of 10 MHz).

- 2) Real-time output

- Serial interface

- SIO0: 8-bit synchronous serial interface

- 1) LSB first/MSB first selectable

- 2) Built-in 8-bit baudrate generator (maximum transfer clock cycle = 4/3 Tcyc)

- Automatic continuous data communication (1 to 256 bits can be specified in 1-bit units) (Suspension and resumption of data transfer possible in 1-byte units)

- SIO1: 8-bit asynchronous/synchronous serial interface

- Mode 0: Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 Tcyc transfer clock) Mode 1: Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 Tcyc baudrate)

- Mode 2: Bus mode 1 (start bit, 8 data bits, 2 to 512 Tcyc transfer clock)

Mode 3: Bus mode 2 (start detection, 8 data bits, stop detection)

- UART1

- Full duplex

- 7/8/9 data bits selectable

- 1 stop bit (2 bits in continuous transmission mode)

- · Built-in baudrate generator

Note: UART1 and PWM use the same pins (P20 and P21), so they cannot be used at the same time.

- AD converter: 12 bits  $\times$  9 channels

- Successive approximation type

- 12-/8-bit resolution selectable

- Port input: 8 channels, dedicated reference voltage input: 1 channel

- PWM: Multifrequency 12-bit PWM × 2 channels

Note: UART1 and PWM use the same pins (P20 and P21), so they cannot be used at the same time.

- Reference voltage generator circuit (VREF17)

- The supply voltage can be monitored by performing AD conversion of the reference voltage from the multifrequency RC oscillator circuit.

- Remote control receiver circuit (multiplexed with P15/SCK1/INT3/T0IN pin)

- Noise rejection function (noise filter time constant selectable from 1 Tcyc/32 Tcyc/128 Tcyc)

- Clock output function

- 1) Capable of generating a clock output with a frequency of  $\frac{1}{1}$ ,  $\frac{1}{2}$ ,  $\frac{1}{4}$ ,  $\frac{1}{8}$ ,  $\frac{1}{16}$ ,  $\frac{1}{32}$ , or  $\frac{1}{64}$  of the source oscillator clock selected as the system clock.

- 2) Capable of generating the source oscillator clock for the subclock.

- Watchdog timer

- Capable of generating an internal reset on an overflow of a timer that runs on either the low-speed RC oscillator clock or subclock.

- Operation on entry into standby mode can be selected from three modes (continue count operation, stop operation, and stop count operation while retaining the count value).

- Interrupts

- 19 sources, 10 vector addresses

- 1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt request of the level equal to or lower than the current interrupt is not accepted.

- 2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt with the lowest vector address has priority.

| No. | Vector | Level  | Interrupt Source     |  |  |

|-----|--------|--------|----------------------|--|--|

| 1   | 00003H | X or L | INT0                 |  |  |

| 2   | 0000BH | X or L | INT1                 |  |  |

| 3   | 00013H | H or L | INT2/T0L/INT4        |  |  |

| 4   | 0001BH | H or L | INT3/ base timer     |  |  |

| 5   | 00023H | H or L | ТОН                  |  |  |

| 6   | 0002BH | H or L | T1L/T1H              |  |  |

| 7   | 00033H | H or L | SIO0/ UART1 receive  |  |  |

| 8   | 0003BH | H or L | SIO1/ UART1 transmit |  |  |

| 9   | 00043H | H or L | ADC/T6/T7/PWM4, PWM5 |  |  |

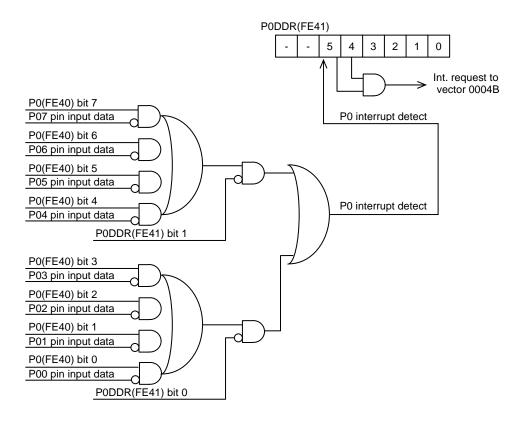

| 10  | 0004BH | H or L | Port 0               |  |  |

• Priority level: X > H > L

- When interrupts of the same level occur at the same time, the interrupt with the lowest vector address is processed first.

- Subroutine stack levels: Up to 128 levels (The stack is allocated in RAM.)

- High-speed multiplication/division instructions

- 16 bits  $\times$  8 bits (5 Tcyc execution time)

- 24 bits  $\times$  16 bits (12 Tcyc execution time)

- 16 bits ÷ 8 bits (8 Tcyc execution time)

- 24 bits ÷ 16 bits (12 Tcyc execution time)

- Oscillator circuits

- Internal oscillator circuits

- 1) Low-speed RC oscillator circuit (SRC): For system clock/watchdog timer (100 kHz)

- 2) Medium-speed RC oscillator circuit (RC): For system clock (1 MHz)

- 3) Multifrequency RC oscillator circuit (MRC): For system clock (8 MHz)

- External oscillator circuits

- 1) High-speed CF oscillator circuit (CF): For system clock, with internal Rf

- 2) Low-speed crystal oscillator circuit (X'tal): For low-speed system clock/watchdog timer, with internal Rf

- <1> The CF and the crystal oscillator circuits use the same pin, the selection of which is programmable.

- Solution <2> Both the CF and crystal oscillator circuits are stopped while the system reset sequence is in progress. Since they remain suspended after reset is released, they must be started under program control.

- System clock frequency divider function

- Can run on low current.

- The minimum instruction cycle can be selected from among 300 ns, 600 ns, 1.2µs, 2.4 µs, 4.8 µs, 9.6 µs, 19.2 µs, 38.4 µs, and 76.8 µs (at a main clock of 10 MHz).

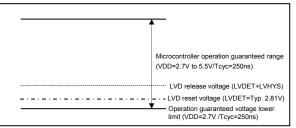

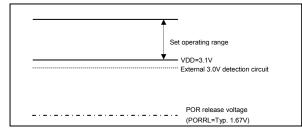

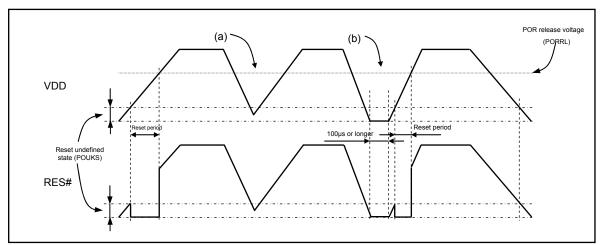

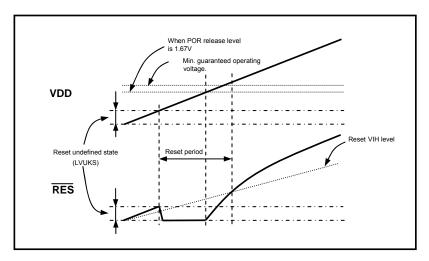

- Internal reset circuit

- Power-on reset (POR) function

- 1) POR is generated only when power is turned on.

- 2) The POR release level can be selected from 8 levels (1,67V, 1.97V, 2.07V, 2.37V, 2.57V, 2.87V, 3.86V, and 4.35V) by setting options.

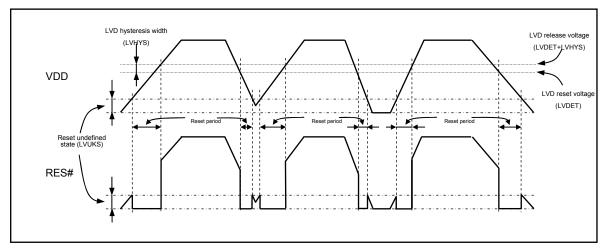

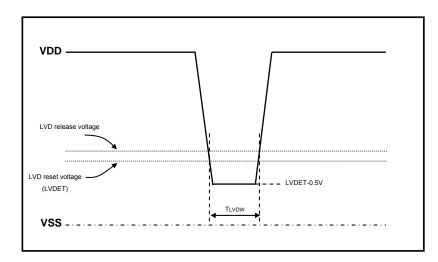

- Low-voltage detection reset (LVD) function

- 1) LVD and POR functions are combined to generate resets when power is turned on and when the power voltage falls below a certain level.

- 2) The use/non-use of the LVD function and the low-voltage detection level (7 levels: 1.91V, 2.01V, 2.31V, 2.51V, 2.81V, 3.79V, and 4.28V) can be selected by setting options.

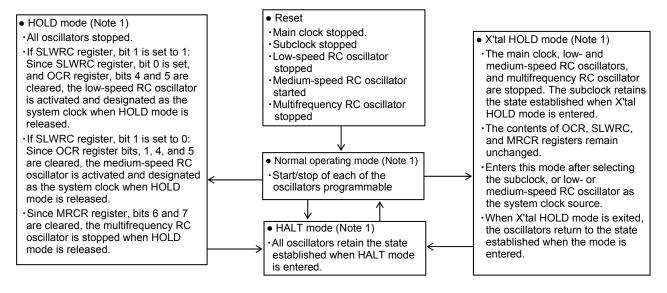

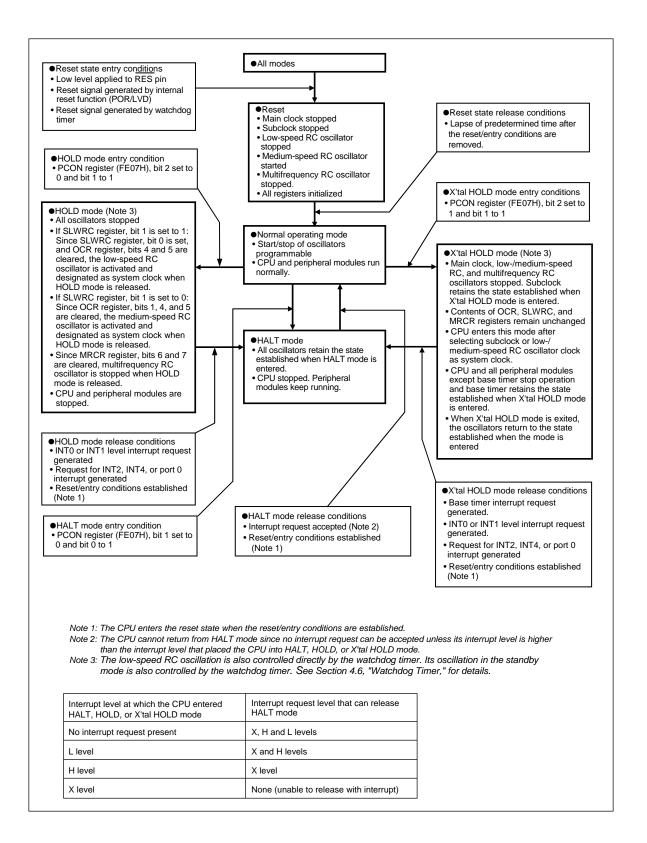

- Standby function

- HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation.

- 1) Oscillators do not stop automatically.

- 2) There are four ways of releasing HALT mode.

- <1> Low level input to the reset pin

- <2> Generating a reset by low-voltage detection

- <3> Generating a reset by the watchdog timer

- <4> Generating an interrupt

- HOLD mode: Suspends instruction execution and the operation of the peripheral circuits.

- 1) The CF oscillator, low-speed/medium-speed/multifrequency RC oscillators, and crystal oscillator automatically stop operation.

- *Note: The low-speed RC oscillation is also controlled directly by the watchdog timer. Its oscillation in the standby mode is also controlled by the watchdog timer.*

- 2) There are five ways of releasing HOLD mode.

- <1> Low level input to the reset pin

- <2> Generating a reset by low-voltage detection

- <3> Generating a reset by the watchdog timer

- <4> Establishing an interrupt source at least at one of INT0, INT1, INT2, and INT4 pins.

- \* INT0 and INT1 HOLD mode release is available only when level detection is set.

- <5> Establishing an interrupt source at port 0.

- X'tal HOLD mode: Suspends instruction execution and the operation of the peripheral circuits except the base timer. (When X'tal oscillator is selected.)

- 1) The CF, low-speed/medium-speed/multifrequency RC oscillators automatically stop operation.

- *Note: The low-speed RC oscillation is also controlled directly by the watchdog timer. Its oscillation in the standby mode is also controlled by the watchdog timer.*

- 2) The state of crystal oscillation established when X'tal HOLD mode is entered is retained.

- 3) There are six ways of releasing X'tal HOLD mode.

- <1> Low level input to the reset pin

- <2> Generating a reset by low-voltage detection

- <3> Generating a reset by the watchdog timer

- <4> Establishing an interrupt source at least at one of INT0, INT1, INT2, and INT4 pins

- \* INT0 and INT1 X'tal HOLD mode release is available only when level detection is set.

- <5> Establishing an interrupt source at port 0

- <6> Establishing an interrupt source in the base timer circuit

Note: Available only when X'tal oscillator is selected.

- On-chip debugger function (flash ROM version only)

- Supports software debugging with the microcontroller mounted on the target board.

- Software break setting

- Stepwise execution of each instruction

- Real time RAM data monitoring function

- All the memory contents can be monitored and rewritten when the program is running. (Part of the special function register (SFR) data cannot be rewritten.)

- Two channels of on-chip debugger pins are available for compatibility with small pin count devices. DBGP0(P0), DBGP1(P1)

- Data security function (flash ROM version only)

- Protects the program data stored in flash memory from unauthorized read or copy. *Note: This data security function does not necessarily provide absolute data security.*

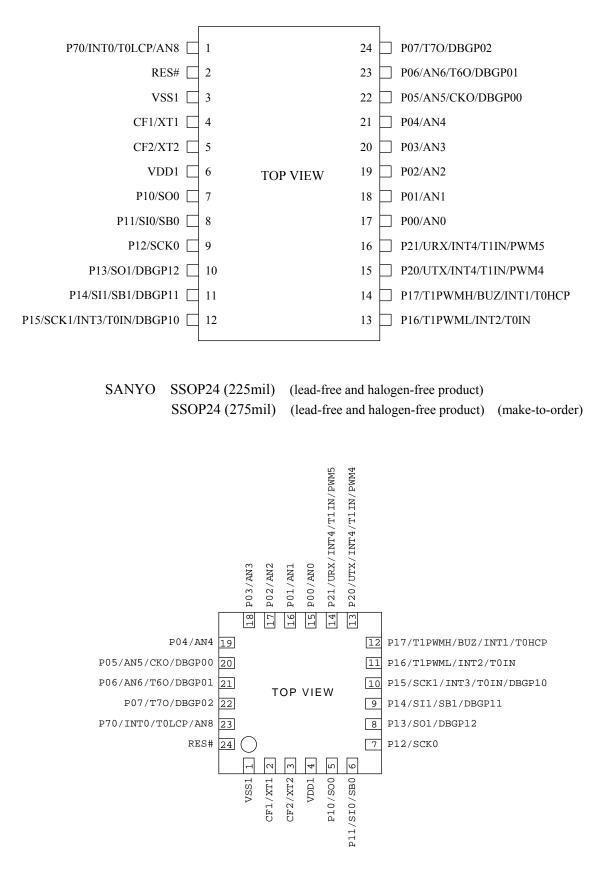

- Package form

- SSOP24 (225mil) (lead-free and halogen-free product)

- SSOP24 (275mil) (lead-free and halogen-free product) (make-to-order)

- VCT24  $(3mm \times 3mm)$  (lead-free and halogen-free product)

- Development tools

- On-chip debugger: (1) TCB87 Type B + LC87FBG08A

- (2) TCB87 Type C (3-wire communication cable) + LC87FBG08A

- Programming board

| Package         | Programming board  |  |  |

|-----------------|--------------------|--|--|

| SSOP24 (225mil) | W87F2GS            |  |  |

| SSOP24 (275mil) | Make-to-order item |  |  |

| VCT24 (3mm×3mm) | W87FBGV            |  |  |

### 1.3 Pinout

SANYO VCT24 (3mm×3mm) (lead-free and halogen-free product)

# 1.4 System Block Diagram

# 1.5 Pin Functions

| Name       | I/O | Description                                                                                      |                           |                         |                         |                | Option       |     |

|------------|-----|--------------------------------------------------------------------------------------------------|---------------------------|-------------------------|-------------------------|----------------|--------------|-----|

| VSS1       | _   | Power supply pin (–)                                                                             |                           |                         |                         |                | No           |     |

| VDD1       | _   | Power supply                                                                                     |                           |                         |                         |                |              | No  |

| Port 0     | I/O |                                                                                                  |                           |                         |                         |                | Yes          |     |

| P00 to P07 | _   | • I/O can be specified in 4-bit units.                                                           |                           |                         |                         |                | 103          |     |

| 10010107   |     | • Pull-up resistors can be turned on and off in 4-bit units.                                     |                           |                         |                         |                |              |     |

|            |     | HOLD release input                                                                               |                           |                         |                         |                |              |     |

|            |     | • Port 0 interrupt input                                                                         |                           |                         |                         |                |              |     |

|            |     | Pin functions     P05: System clock output                                                       |                           |                         |                         |                |              |     |

|            |     | -                                                                                                | r 6 toggle c              | 1                       |                         |                |              |     |

|            |     |                                                                                                  | r 7 toggle c              |                         |                         |                |              |     |

|            |     |                                                                                                  |                           |                         | nverter input p         | oort           |              |     |

|            |     |                                                                                                  |                           |                         | ): On-chip deb          |                | 5            |     |

| Port 1     | I/O | • 8-bit I/O po                                                                                   |                           |                         |                         |                |              | Yes |

| P10 to P17 | -   | • I/O can be s                                                                                   |                           |                         |                         |                |              |     |

|            |     | 1                                                                                                |                           | e turned on a           | and off in 1-bit        | units.         |              |     |

|            |     | • Pin function                                                                                   |                           |                         |                         |                |              |     |

|            |     |                                                                                                  | data outpu<br>data input/ |                         |                         |                |              |     |

|            |     | P11: SIO0<br>P12: SIO0                                                                           |                           | bus I/O                 |                         |                |              |     |

|            |     |                                                                                                  | data outpu                | t                       |                         |                |              |     |

|            |     |                                                                                                  | data input/               |                         |                         |                |              |     |

|            |     |                                                                                                  |                           |                         | (input with no          | ise filter)/ti | mer 0 event  |     |

|            |     |                                                                                                  |                           | capture inpu            | ıt<br>2 input/HOLE      | ralaaca inn    | ut/time or 0 |     |

|            |     | even                                                                                             | t input/time              | er 0L captur            | 2 input/HOLL<br>e input | release inp    | ut/timer 0   |     |

|            |     | P17: Time                                                                                        | r 1 PWMH                  | output/buzz             | zer output/INT          | 1 input/HO     | LD release   |     |

|            |     |                                                                                                  |                           | capture inpu            |                         |                |              |     |

|            |     |                                                                                                  |                           |                         | ): On-chip deb          | ugger I pin    | S            |     |

|            |     | Interrupt                                                                                        | acknowled                 |                         | Rising &                |                |              |     |

|            |     |                                                                                                  | Rising                    | Falling                 | Falling                 | H level        | L level      |     |

|            |     | INT1                                                                                             | 0                         | 0                       | ×                       | 0              | 0            |     |

|            |     | INT2                                                                                             | 0                         | 0                       | 0                       | ×              | ×            |     |

|            |     | INT3                                                                                             | 0                         | 0                       | 0                       | ×              | ×            |     |

| Port 2     | I/O | • 2-bit I/O po                                                                                   | rt                        |                         |                         |                |              | Yes |

| P20, P21   | _   | • I/O can be s                                                                                   | 1                         |                         |                         |                |              |     |

| - )        |     | 1                                                                                                |                           | e turned on a           | and off in 1-bit        | units.         |              |     |

|            |     | • Pin function                                                                                   | -                         |                         |                         |                |              |     |

|            |     |                                                                                                  |                           | PWM4 outp<br>PWM5 outpu |                         |                |              |     |

|            |     |                                                                                                  |                           | 1                       | ase input/time          | r 1 event in   | nut/timer    |     |

|            |     |                                                                                                  | 0L capture                | input/timer             | 0H capture in           | put            |              |     |

|            |     | Interrupt a                                                                                      | cknowledge                | e type                  |                         | -              |              |     |

|            |     |                                                                                                  | Rising                    | Falling                 | Rising &                | H level        | L level      |     |

|            |     | INIT4                                                                                            | 0                         | 0                       | Falling                 |                | X            |     |

|            | 1/0 | INT4                                                                                             |                           |                         | 0                       | ×              | ×            |     |

| Port 7     | I/O | • 1-bit I/O po                                                                                   |                           |                         |                         |                |              | No  |

| P70        |     | <ul> <li>I/O can be s</li> <li>Pull-up resi</li> </ul>                                           |                           | turned on a             | and off                 |                |              |     |

|            |     | • Pin function                                                                                   |                           |                         | ui <b>u</b> 011.        |                |              |     |

|            |     |                                                                                                  |                           | D release in            | nput/timer 0L           | capture inpu   | ıt           |     |

|            |     | P70: INT0 input/HOLD release input/timer 0L capture input<br>P70 (AN8)): AD converter input port |                           |                         |                         |                |              |     |

|            |     | Interrupt                                                                                        | acknowled                 | ge type                 | <b>B</b>                | 1              | ·i           |     |

|            |     |                                                                                                  | Rising                    | Falling                 | Rising &<br>Falling     | H level        | L level      |     |

|            |     | INT0                                                                                             | 0                         | 0                       | ×                       | 0              | 0            |     |

|            |     | 11110                                                                                            | ~                         |                         | ~                       | Ŭ              | Ŭ            |     |

Continued on next page

Continued from preceding page

| Name    | Option |                                                                                                                                |    |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------|----|

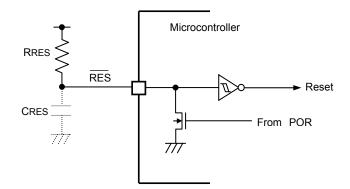

| RES     | I/O    | External reset input/internal reset output pin                                                                                 | No |

| CF1/XT1 | Ι      | <ul> <li>Ceramic resonator/32.768 kHz crystal resonator input</li> <li>Pin functions<br/>General-purpose input port</li> </ul> | No |

| CF2/XT2 | I/O    | <ul> <li>Ceramic resonator/32.768 kHz crystal resonator output</li> <li>Pin functions<br/>General-purpose I/O port</li> </ul>  | No |

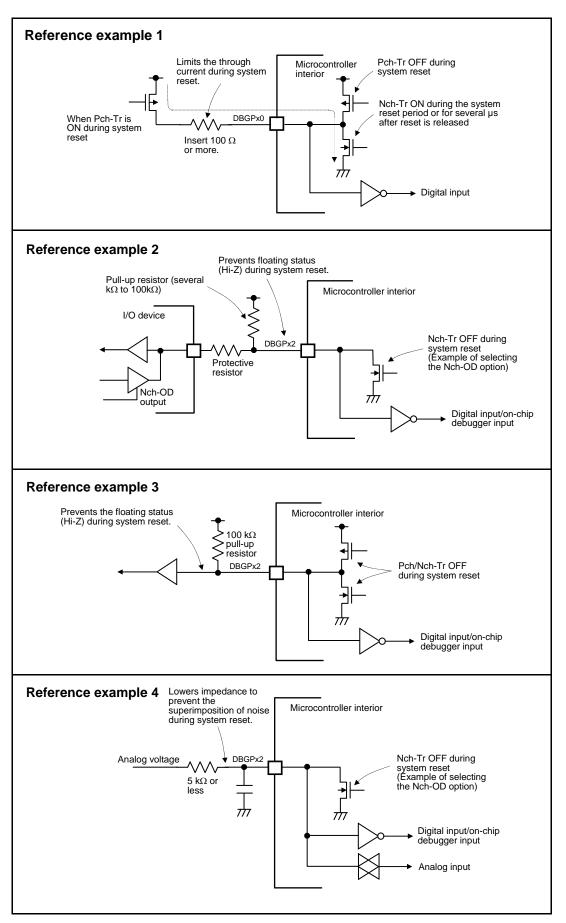

### **1.6 On-chip Debugger Pin Connection Requirements**

For the treatment of the on-chip debugger pins, refer to the separately available document entitled "Onchip Debugger Installation Manual" and APPENDIX-III "LC872000/LC87B000 Series On-chip Debugger Pin Treatment Guide."

### **1.7 Recommended Unused Pin Connections**

| Pin        | Recommended Unused Pin Connections                  |                            |  |  |  |

|------------|-----------------------------------------------------|----------------------------|--|--|--|

| Pin        | Board                                               | Software                   |  |  |  |

| P00 to P07 | Open                                                | Output low                 |  |  |  |

| P10 to P17 | Open                                                | Output low                 |  |  |  |

| P20 to P21 | Open                                                | Output low                 |  |  |  |

| P70        | Open                                                | Output low                 |  |  |  |

| CF1/XT1    | Pulled down with a resistor of $100k\Omega$ or less | General-purpose input port |  |  |  |

| CF2/XT2    | Pulled down with a resistor of $100k\Omega$ or less | General-purpose input port |  |  |  |

### 1.8 Port Output Types

The table below lists the types of port outputs and the presence/absence of a pull-up resistor. Data can be read into any input port even if it is in output mode.

| Port       | Option<br>Selected in<br>Units of | Option Type | Output Type                                                              | Pull-up Resistor      |

|------------|-----------------------------------|-------------|--------------------------------------------------------------------------|-----------------------|

| P00 to P07 | 1 bit                             | 1           | CMOS                                                                     | Programmable (Note 1) |

|            |                                   | 2           | N-channel open drain                                                     | No                    |

| P10 to P17 | 1 bit                             | 1           | CMOS                                                                     | Programmable          |

| P20, P21   |                                   | 2           | N-channel open drain                                                     | Programmable          |

| P70        | _                                 | No          | N-channel open drain                                                     | Programmable          |

| CF2/XT2    | _                                 | No          | Ceramic resonator/32.768 kHz crystal resonator output                    | No                    |

|            |                                   |             | N-channel open drain                                                     |                       |

|            |                                   |             | (N-channel open drain when<br>selected as a general-purpose<br>I/O port) |                       |

Note 1: The control of the presence or absence of the programmable pull-up resistors for port 0 and switching between low- and high-impedance pull-up connections is exercised in nibble (4-bit) units (P00 to P03 or P04 to P07).

### 1.9 User Option Table

| Option                     | Option to be<br>Applied on | Mask<br>Version *1 | Flash ROM<br>Version | Option Selected<br>in Units of | Option Selection     |

|----------------------------|----------------------------|--------------------|----------------------|--------------------------------|----------------------|

|                            | D00 to D07                 | 0                  | 0                    | 1 1.4                          | CMOS                 |

|                            | P00 to P07                 | -                  | _                    | 1 bit                          | N-channel open drain |

|                            | D10 4- D17                 | 0                  | 0                    | 1.1.4                          | CMOS                 |

| Port output type           | P10 to P17                 | 0                  | U                    | 1 bit                          | N-channel open drain |

|                            | D20 / D21                  | 0                  | 0                    |                                | CMOS                 |

|                            | P20 to P21                 | 0                  | 0                    | 1 bit                          | N-channel open drain |

| Program start              |                            | ×                  | 0                    |                                | 00000h               |

| address                    | -                          | *2                 | 0                    | -                              | 01E00h               |

| Low-voltage                | Detection                  | 0                  | 0                    |                                | Enable: Use          |

| detection reset            | function                   | 0                  | 0                    | -                              | Disable: Non-use     |

| function                   | Detection                  | 0                  | 0                    | -                              | 7 levels             |

| Power-on reset<br>function | Power-on<br>reset level    | 0                  | 0                    | _                              | 8 levels             |

\*1: Mask option selection: No change is possible after the mask is completed.

\*2: Program start address of the mask version is 00000h.

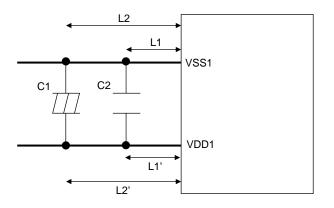

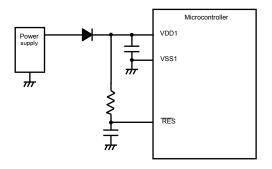

### **1.10** Power Pin Treatment Recommendations (VDD1, VSS1)

Connect bypass capacitors between VDD1 and VSS1 pins so that the following conditions are satisfied:

- Connect the VDD1 and VSS1 pins and bypass capacitors C1 and C2 using the shortest possible heavy lead wires, making sure that the impedances between both pins and bypass capacitors are as equal as possible (L1=L1', L2=L2').

- Insert a large-capacitance capacitor C1 and a small-capacitance capacitor C2 in parallel. The capacitance of C2 should be approximately 0.1  $\mu$ F.

# 2. Internal Configuration

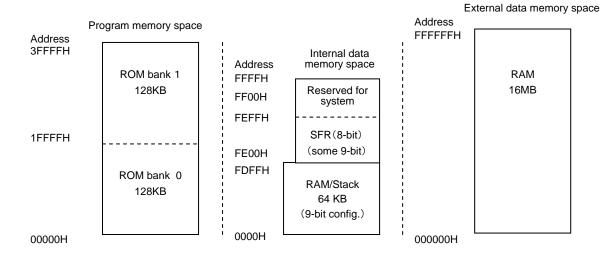

### 2.1 Memory Space

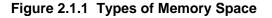

LC870000 series microcontrollers have the following three types of memory space:

- 1) Program memory space: 256K bytes (128K bytes × 2 banks)

- 2) Internal data memory space: 64K byt

64K bytes (0000H to FDFFH out of 0000H to FFFFH is shared with the stack area.)

3) External data memory space: 16M bytes

Note: SFR is the area in which special function registers such as the accumulator are allocated (see Appendix A-I).

### 2.2 Program Counter (PC)

The program counter (PC) is made up of 17 bits and a bank flag BNK. The value of BNK determines the bank. The low-order 17 bits of the PC allows linear access to the 128K ROM space in the current bank.

Normally, the PC advances automatically in the current bank on each execution of an instruction. Bank switching is accomplished by executing a return instruction after pushing necessary addresses onto the stack. When executing a branch or subroutine instruction, when accepting an interrupt, or when a reset is generated, the value corresponding to each operation is loaded into the PC.

Table 2.2.1 lists the values that are loaded into the PC when the respective operations are performed.

|         |                  | Operation                    | PC Value                        | <b>BNK Value</b> |

|---------|------------------|------------------------------|---------------------------------|------------------|

| Inter-  | Reset (Note)     |                              | 00000Н                          | 0                |

| rupt    |                  |                              | 01E00H                          | 0                |

|         | INT0             |                              | 00003H                          | 0                |

|         | INT1             |                              | 0000BH                          | 0                |

|         | INT2/T0L/INT4    |                              | 00013H                          | 0                |

|         | INT3 /base timer |                              | 0001BH                          | 0                |

|         | ТОН              |                              | 00023H                          | 0                |

|         | T1L/T1H          |                              | 0002BH                          | 0                |

|         | SIO0/UART1 red   | ceive                        | 00033H                          | 0                |

|         | SIO1/UART1 tra   | nsmit                        | 0003BH                          | 0                |

|         | ADC/T6/T7/PW     | M4, PWM5                     | 00043H                          | 0                |

|         | Port 0           |                              | 0004BH                          | 0                |

| Uncor   | ditional branch  | JUMP a17                     | PC=a17                          | Unchanged        |

| instrue | ctions           | BR r12                       | PC=PC+2+r12[-2048 to +2047]     | Unchanged        |

| Condi   | tional branch    | BE, BNE, DBNZ, DBZ, BZ, BNZ, | PC=PC+nb+r8[-128 to +127]       | Unchanged        |

| instruc | ctions           | BZW, BNZW, BP, BN, BPC       | nb: Number of instruction bytes |                  |

| Call ir | nstructions      | CALL a17                     | PC=a17                          | Unchanged        |

|         |                  | RCALL r12                    | PC=PC+2+r12[-2048 to +2047]     | Unchanged        |

|         |                  | RCALLA                       | PC=PC+1+Areg[0 to +255]         | Unchanged        |

| Return  | n instructions   | RET, RETI                    | PC16 to 08=(SP)                 | BNK is set       |

|         |                  |                              | PC07 to 00=(SP-1)               | to bit 8 of      |

|         |                  |                              | (SP) denotes the contents of    | (SP-1).          |

|         |                  |                              | RAM address designated by the   |                  |

|         |                  |                              | value of the stack pointer SP.  |                  |

| Standa  | ard instructions | NOP, MOV, ADD,               | PC=PC+nb                        | Unchanged        |

|         |                  |                              | nb: Number of instruction bytes |                  |

Table 2.2.1 Values Loaded in the PC

Note: The reset-time program start address can be selected through a user option in the flash version product. In the mask version, the program start address is fixed at address 00000H.

### 2.3 Program Memory (ROM)

This series of microcontrollers has a program memory space of 256K bytes but the size of the ROM that is actually incorporated in the microcontroller varies with the type of the microcontroller. The ROM table look-up instruction (LDC) can be used to refer all ROM data within the bank. Of the ROM space, the 256 bytes in ROM bank 0 (01F00H to 01FFFH for this series of microcontrollers) are reserved as the option area. Consequently, this area is not available as a program area.

### 2.4 Internal Data Memory (RAM)

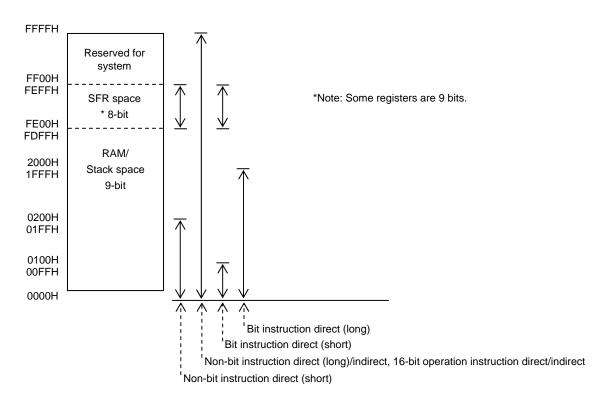

This series of microcontrollers has an internal data memory space of 64K bytes but the size of the RAM that is actually incorporated in the microcontroller varies with the type of the microcontroller. Nine bits are used to access addresses 0000H to FDFFH of the 128K ROM space and 8 or 9 bits are used to access addresses FE00H to FFFFH. The 9th bit of RAM is implemented by bit 1 of the PSW and can be read and written.

The 128 bytes of RAM from 0000H to 007FH are paired to form 64 2-byte indirect address registers. The bit length of these indirect registers is normally 16 bits (8 bits  $\times$  2). When they are used by the ROM table look-up instruction (LDC), however, their bit length is set to 17 bits (9 high-order bits + 8 low-order bits).

As shown in Figure 2.4.1, the available instructions vary depending on the RAM address. The efficiency of the ROM used and a higher execution speed can be attempted using these instructions properly.

When the value of the PC is stored in RAM during the execution of a subroutine call instruction or interrupt, assuming that SP represents the current value of the stack pointer, the value of BNK and the low-order 8 bits of the (17-bit) PC are stored in RAM address SP+1 and the high-order 9 bits in SP + 2, after which SP is set to SP + 2.

### 2.5 Accumulator/A Register (ACC/A)

The accumulator (ACC), also called the A register, is an 8-bit register that is used for data computation, transfer, and I/O processing. It is allocated to address FE00H in the internal data memory space and initialized to 00H on a reset.

| Address | Initial Value | R/W | Name | BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|---------|---------------|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

| FE00    | 0000 0000     | R/W | AREG | AREG7 | AREG6 | AREG5 | AREG4 | AREG3 | AREG2 | AREG1 | AREG0 |

### 2.6 B Register (B)

The B register is combined with the ACC to form a 16-bit arithmetic register during the execution of a 16bit arithmetic instruction. During a multiplication or division instruction, the B register is used with the ACC and C register to store the results of computation. In addition, during an external memory access instruction (LDX or STX), the B register designates the high-order 8 bits of the 24-bit address.

The B register is allocated to address FE01H of the internal data memory space and initialized to 00H on a reset.

| Address | Initial Value | R/W | Name | BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|---------|---------------|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

| FE01    | 0000 0000     | R/W | BREG | BREG7 | BREG6 | BREG5 | BREG4 | BREG3 | BREG2 | BREG1 | BREG0 |

### 2.7 C Register (C)

The C register is used with the ACC and B register to store the results of computation during the execution of a multiplication or division instruction. In addition, during a C register offset indirect instruction, the C register stores the offset data (-128 to + 127) to the contents of an indirect register.

The C register is allocated to address FE02H of the internal data memory space and initialized to 00H on a reset.

| l | Address | Initial Value | R/W | Name | BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|---|---------|---------------|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | FE02    | 0000 0000     | R/W | CREG | CREG7 | CREG6 | CREG5 | CREG4 | CREG3 | CREG2 | CREG1 | CREG0 |

### 2.8 Program Status Word (PSW)

The program status word (PSW) is made up of flags that indicate the status of computation results, a flag to access the 9th bit of RAM, and a flag to designate the bank during the LDCW instruction. The PSW is allocated to address FE06H of the internal data memory space and initialized to 00H on a reset.

| Address | Initial Value | R/W | Name | BIT7 | BIT6 | BIT5  | BIT4  | BIT3   | BIT2 | BIT1 | BIT0   |

|---------|---------------|-----|------|------|------|-------|-------|--------|------|------|--------|

| FE06    | 0000 0000     | R/W | PSW  | CY   | AC   | PSWB5 | PSWB4 | LDCBNK | OV   | P1   | PARITY |

#### CY (bit 7): Carry flag

CY is set (to 1) when a carry occurs as the result of a computation and cleared (to 0) when no carry occurs. There are following four types of carries:

- <1> Carry resulting from an addition

- <2> Borrow resulting from a subtraction

- <3> Borrow resulting from a comparison

- <4> Carry resulting from a rotation

There are some instructions that do not affect this flag at all.

#### AC (bit 6): Auxiliary carry flag

AC is set (to 1) when a carry or borrow occurs in bit 3 (bit 3 of the high-order byte during a 16-bit computation) as the result of an addition or subtraction and cleared (to 0) otherwise.

There are some instructions that do not affect this flag at all.

#### PSWB5, PSWB4 (bits 5 and 4): User bits

These bits can be read and written through instructions. They can be used by the user freely.

#### LDCBNK (bit 3): Bank flag for the table look-up instruction (LDCW)

This bit designates the ROM bank to be specified when reading the program ROM with a table look-up instruction.

(0: ROM-ADR = 0 to 1FFFF, 1: ROM-ADR = 20000 to 3FFFF)

#### OV (bit 2): Overflow flag

OV is set (to 1) when an overflow occurs as the result of an arithmetic operation and cleared (to 0) otherwise. An overflow occurs in the following cases:

- <1> When MSB is used as the sign bit and when the result of negative number + negative number or negative number positive number is a positive.

- <2> When MSB is used as the sign bit and when the result of positive number + positive number or positive number negative number is a negative number.

- <3> When the high-order 8 bits of a 16 bits  $\times$  8 bits multiplication is nonzero.

- <4> When the high-order 16 bits of a 24 bits  $\times$  16 bits multiplication is nonzero.

- <5> When the divisor of a division is 0.

There are some instructions that do not affect this flag at all.

#### P1 (bit 1): RAM bit 8 data flag

P1 is used to manipulate bit 8 of 9-bit internal data RAM (0000H to FDFFH). Its behavior varies depending on the instruction executed. See Table 2.4.1 for details.

#### PARITY (bit 0): Parity flag

This bit shows the parity of the accumulator (A register). The parity flag is set (to 1) when there is an odd number of 1's in the A register. It is cleared (to 0) when there is an even number of 1's in the A register.

#### 2.9 Stack Pointer (SP)

LC870000 series microcontrollers can use RAM addresses 0000H to FDFFH as a stack area. The size of RAM, however, varies depending on the microcontroller type. The SP is 16 bits long and made up of two registers: SPL (at address FE0A) and SPH (at address FE0B). It is initialized to 0000H on a reset.

The SP is incremented by 1 before data is saved in stack memory and decremented by 1 after the data is restored from stack memory.

| Address | Initial Value | R/W | Name | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------|---------------|-----|------|------|------|------|------|------|------|------|------|

| FE0A    | 0000 0000     | R/W | SPL  | SP7  | SP6  | SP5  | SP4  | SP3  | SP2  | SP1  | SP0  |

| FE0B    | 0000 0000     | R/W | SPH  | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9  | SP8  |

The value of the SP changes as follows:

<1> When the PUSH instruction is executed:

<2> When the CALL instruction is executed:

<3> When the POP instruction is executed:

<4> When the RET instruction is executed:

SP = SP + 1, RAM (SP) = DATA SP = SP + 1, RAM (SP) = ROMBANK + ADL SP = SP + 1, RAM (SP) = ADH DATA = RAM (SP), SP = SP - 1ADH = RAM (SP), SP = SP - 1ROM BANK + ADL = RAM(SP), SP = SP - 1

### 2.10 Indirect Addressing Registers

LC870000 series microcontrollers are provided with three addressing schemes ([Rn], [Rn + C], [off]), which use the contents of indirect registers (indirect addressing modes). (See Section 2.11 for the addressing modes.) These addressing modes use 64 2-byte indirect registers (R0 to R63) allocated to RAM addresses 0 to 7EH. The indirect registers can also be used as general-purpose registers (e.g., for saving 2-byte data). Naturally, these addresses can be used as ordinary RAM (in 1- byte (9 bits) units) if they are not used as indirect registers. R0 to R63 are "system reserved words" to the assembler and need not be defined by the user.

Figure 2.10.1 Allocation of Indirect Registers

### 2.11 Addressing Modes

LC870000 series microcontrollers support the following seven addressing modes:

- <1> Immediate (immediate data refers to data whose value has been established at program preparation (assembly) time.)

- <2> Indirect register (Rn) indirect ( $0 \le n \le 63$ )

- <3> Indirect register (Rn) + C register indirect ( $0 \le n \le 63$ )

- <4> Indirect register (R0) + Offset value indirect

- <5> Direct

- <6> ROM table look-up

- <7> External data memory access

The rest of this section describes these addressing modes.

#### 2.11.1 Immediate Addressing (#)

The immediate addressing mode allows 8-bit (1-byte) or 16-bit (1-word) immediate data to be handled. Examples are given below.

#### **Examples:**

|     | LD   | #12H;     | Loads the accumulator with byte data (12H).                 |

|-----|------|-----------|-------------------------------------------------------------|

| L1: | LDW  | #1234H;   | Loads the BA register pair with word data (1234H).          |

|     | PUSH | #34H;     | Loads the stack with byte data (34H).                       |

|     | ADD  | #56H;     | Adds byte data (56H) to the accumulator.                    |

|     | BE   | #78H, L1; | Compares byte data (78H) with the accumulator for a branch. |

#### 2.11.2 Indirect Register Indirect Addressing ([Rn])

In indirect register indirect addressing mode, it is possible to select one of the indirect registers (R0 to R63) and use its contents to designate an address in RAM or SFR. When the selected register contains, for example, "FE02H," it designates the C register.

#### Example: When R3 contains "123H" (RAM address 6: 23H, RAM address 7: 01H)

|     | LD   | [R3];     | Transfers the contents of RAM address 123H to the accumulator.          |

|-----|------|-----------|-------------------------------------------------------------------------|

| L1: | STW  | [R3];     | Transfers the contents of BA register pair to RAM address 123H.         |

|     | PUSH | [R3];     | Saves the contents of RAM address123H in the stack.                     |

|     | SUB  | [R3];     | Subtracts the contents of RAM address 123H from the accumulator.        |

|     | DBZ  | [R3], L1; | Decrements the contents of RAM address 123H by 1 and causes a branch if |

|     |      |           | zero.                                                                   |

#### 2.11.3 Indirect Register + C Register Indirect Addressing ([Rn, C])

In the indirect register + C register indirect addressing mode, the result of adding the contents of one of the indirect registers (R0 to R63) to the contents of the C register (-128 to + 127 with MSB being the sign bit) designates an address in RAM or SFR. For example, if the selected indirect register contains "FE02H" and the C register contains "FFH (-1)," the address "B register (FE02H + (-1) = FE01H" is designated.

#### Examples: When R3 contains "123H" and the C register contains "02H"

|     | LD   | [R3, C];     | Transfers the contents of RAM address 125H to the accumulator.          |

|-----|------|--------------|-------------------------------------------------------------------------|

| L1: | STW  | [R3, C];     | Transfers the contents of the BA register pair to RAM address 125H.     |

|     | PUSH | [R3, C];     | Saves the contents of RAM address 125H in the stack.                    |

|     | SUB  | [R3, C];     | Subtracts the contents of RAM address 125H from the accumulator.        |

|     | DBZ  | [R3, C], L1; | Decrements the contents of RAM address 125H by 1 and causes a branch if |

|     |      |              | zero.                                                                   |

#### <Notes on this addressing mode >

The internal data memory space is divided into three closed functional areas as explained in Section 2.1, namely, 1) system reserved area (FF00H to FFFFH), 2) SFR area (FE00H to FEFFH), and 3) RAM/stack area (0000H to FDFFH). Consequently, it is not possible to point to a different area using the value of the C register from the basic area designated by the contents of Rn. For example, if the instruction "LD [R5,C]" is executed when R5 contains "0FDFFH" and the C register contains "1," since the basic area is 3) RAM/stack area (0000H to FDFFH), the intended address "0FDFFH + 1 = 0FE00H" lies outside the basic area and "0FFH" is consequently placed in the ACC as the results of LD. If the instruction "LD [R5,C]" is executed when R5 contains "0FEFFH" and the C register contains "2," since the basic area is 2) SFR area (FE00H to FEFFH), the intended address "0FEF01H" lies outside the basic area is 2) SFR area (FE00H to FEFFH), the intended address space, the part of the address data addressing outside the 8-bit address space is ignored and the contents of 0FE01H (B register) are placed in the ACC as the result of the computation "0FF01H&0FFH + 0FE00H = 0FE01H."

#### 2.11.4 Indirect Register (R0) + Offset Value Indirect Addressing ([off])

In this addressing mode, the results of adding the 7-bit signed offset data off (-64 to + 63) to the contents of the indirect register R0 designate an address in RAM or SFR. If R0 contains "FE02H" and off has a value of "7EH(-2)," for example, the A register (FE02H + (-2) = FE00H) is designated.

#### Examples: When R0 contains "123H" (RAM address 0: 23H, RAM address 1: 01H)

|     | LD   | [10H];     | Transfers the contents of RAM address 133H to the accumulator.          |

|-----|------|------------|-------------------------------------------------------------------------|

| L1: | STW  | [10H];     | Transfers the contents of the BA register pair to RAM address 133H.     |

|     | PUSH | [10H];     | Saves the contents of RAM address 133H in the stack.                    |

|     | SUB  | [10H];     | Subtracts the contents of RAM address 133H from the accumulator.        |

|     | DBZ  | [10H], L1; | Decrements the contents of RAM address 133H by 1 and causes a branch if |

|     |      |            | zero.                                                                   |

|     |      |            |                                                                         |

#### <Notes on this addressing mode>

The internal data memory space is divided into three closed functional areas as explained in Section 2.1, namely, 1) system reserved area (FF00H to FFFFH), 2) SFR area (FE00H to FEFFH), and 3) RAM/stack area (0000H to FDFFH). Consequently, it is not possible to point to a different area using an offset value from the basic area designated by the contents of R0. For example, if the instruction "LD [1]" is executed when R0 contains "0FDFFH," since the basic area is 3) RAM/stack area (0000H to FDFFH), the intended address "0FDFFH+1 = 0FE00H" lies outside the basic area and "0FFH" is placed in the ACC as the results of LD. If the instruction "LD [2]" is executed when R0 contains "0FEFFH," since the basic area is 2) SFR (FE00H to FEFFH), the intended address "0FEFFH + 2 = 0FF01H" lies outside the basic area. In this case, since SFR is confined in an 8-bit address space, the part of the address data addressing outside the 8-bit address space is ignored and the contents of "0FE01H (B register) are placed in the ACC as the result of computation "0FF01H&0FFH + 0FE00H = 0FE01H."

#### 2.11.5 Direct Addressing (dst)

Direct addressing mode allows a RAM or SFR address to be specified directly in an operand. In this addressing mode, the assembler automatically generates the optimum instruction code from the address specified in the operand (the number of instruction bytes varies according to the address specified in the operand). Long (middle) range instructions (identified by an "L (M)" at the end of the mnemonic) are available to make the byte count of instructions constant (align instructions with the longest one).

#### **Examples:**

|     | LD   | 123H;     | Transfers the contents of RAM address 123H to the accumulator           |

|-----|------|-----------|-------------------------------------------------------------------------|

|     |      |           | (2-byte instruction).                                                   |

|     | LDL  | 123H;     | Transfers the contents of RAM address 123H to the accumulator           |

|     |      |           | (3-byte instruction).                                                   |

| L1: | STW  | 123H;     | Transfers the contents of the BA register pair to RAM address 123H.     |

|     | PUSH | 123H;     | Saves the contents of RAM address 123H in the stack.                    |

|     | SUB  | 123H;     | Subtracts the contents of RAM address 123H from the accumulator.        |

|     | DBZ  | 123H, L1; | Decrements the contents of RAM address 123H by 1 and causes a branch if |

|     |      |           | zero.                                                                   |

#### 2.11.6 ROM Table Look-up Addressing

The LC870000 series microcontrollers can read 2-byte data into the BA register pair at once using the LDCW instruction. Three addressing modes [Rn], [Rn, C], and [off] are available for this purpose. (In this case only, Rn is configured as 17-bit registers (128K-byte space)).

For models with banked ROM, it is possible to reference the ROM data in the ROM bank (128K bytes) identified by the LDCBNK flag (bit 3) in the PSW. Consequently, when looking into the ROM table on a series model with banked ROM, execute the LDCW instruction after switching the bank using the SET1 or CLR1 instruction so that the LDCBNK flag designates the ROM bank where the ROM table resides.

#### **Examples:**

| TBL: | DB    | 34H              |                                                                |

|------|-------|------------------|----------------------------------------------------------------|

|      | DB    | 12H              |                                                                |

|      | DW    | 5678H            |                                                                |

|      | •     | •                |                                                                |

|      | •     | •                |                                                                |

|      | LDW   | #TBL;            | Loads the BA register pair with the TBL address.               |

|      | CHGP3 | (TBL >> 17) & 1; | Loads LDCBNK in PSW with bit 17 of the TBL address. (Note 1)   |

|      | CHGP1 | (TBL >> 16) & 1; | Loads P1 in PSW with bit 16 of the TBL address.                |

|      | STW   | R0;              | Load indirect register R0 with the TBL address (bits 16 to 0). |

|      | LDCW  | [1];             | Reads the ROM table ( $B = 78H$ , ACC = 12H).                  |

|      | MOV   | #1, C;           | Loads the C register with "01H."                               |

|      | LDCW  | [R0, C];         | Reads the ROM table ( $B = 78H$ , ACC = 12H).                  |

|      | INC   | С;               | Increments the C register by 1.                                |

|      | LDCW  | [R0, C]:         | Reads the ROM table ( $B = 56H$ , ACC = 78H).                  |

|      |       |                  |                                                                |

Note 1: LDCBNK (bit 3) of PSW needs to be set up only for models with banked ROM.

#### 2.11.7 External Data Memory Addressing

LC870000 series microcontrollers can access external data memory spaces of up to 16M bytes (24 bits) using the LDX and STX instructions. To designate a 24-bit space, specify the contents of the B register (8 bits) as the highest-order byte of the address, and the contents (16 bits) of (Rn), (Rn) + (C), or (R0) + off (either one) as the low-order bytes of the address.

#### **Examples:**

| LDW | #3456H;  | Sets up the low-order 16 bits.                                            |

|-----|----------|---------------------------------------------------------------------------|

| STW | R5;      | Loads the indirect register R5 with the low-order 16 bits of the address. |

| MOV | #12H, B; | Sets up the high-order 8 bits of the address.                             |

| LDX | [1];     | Transfers the contents of external data memory (address 123456H) to the   |

|     |          | accumulator.                                                              |

### 2.12 Wait Operation

#### 2.12.1 Occurrence of Wait Operation

In this series, wait operation that automatically suspends instruction execution occurs in the following cases.

1) When continuous data transfer with SIOCTR (SCON0, bit 4) set is performed using SIO0, a wait request is generated and wait operation (RAM data transfer) is performed for one cycle before each 8-bit data transfer.

#### 2.12.2 What is Wait Operation?

- 1) When a wait request is generated by a factor such as described in 2.12.1, the CPU suspends instruction execution for one cycle and performs the specified data transfer during this period. This is wait operation.

- 2) The timer, PWM and other peripheral circuits continue to operate unchanged even during wait operation.

- 3) Wait operation is not performed continuously for 2 cycles or more.

- 4) Wait operation is not performed in HALT mode and HOLD mode

- 5) Note that when wait operation occurs one time, a difference of one cycle occurs between the program counter progress and the real-time progress.

| Instruction     | Bit 8 (RAM/SFR)                            | P1 (PSW Bit 1)                | Remarks                                                                 |

|-----------------|--------------------------------------------|-------------------------------|-------------------------------------------------------------------------|

| LD#/LDW#        | _                                          | -                             |                                                                         |

| LD              | _                                          | P1←REG8                       |                                                                         |

| LDW             | _                                          | P1←REGH8                      |                                                                         |

| ST              | REG8←P1                                    | _                             |                                                                         |

| STW             | REGL8, REGH8←P1                            | _                             |                                                                         |

| MOV             | REG8←P1                                    | _                             |                                                                         |

| PUSH#           | RAM8←P1                                    | _                             |                                                                         |

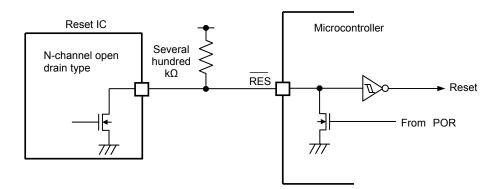

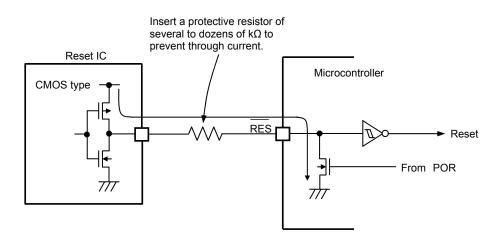

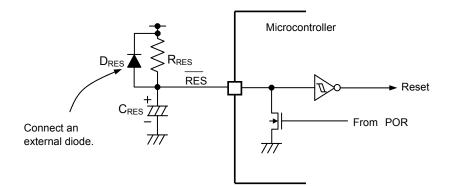

| PUSH            | RAM8←REG8                                  | P1←REG8                       |                                                                         |