## UC1707-SP

ZHCS145-MARCH 2011

查询样品: UC1707-SP

说明

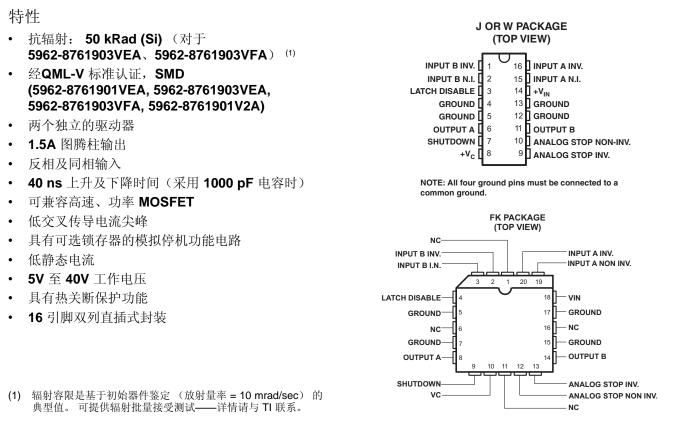

UC1707 功率驱动器采用高速肖特基工艺制造,可实现低电平控制功能部件与高功率开关器件(特别是功率 MOSFET)之间的连接。UC1707 包含两个独立的通道,每个通道可由一个高或低输入逻辑电平信号来启动。只要不超过功耗限值,每个输出能供应或吸收高达 1.5 A 的电流。

尽管每个输出都能利用其自己的输入来单独启动,但它可通过停机端子上的一个数字高电平信号或一个差分低电平 模拟信号的作用共同强制为低电平。来自任一电源的停机命令可以是闭锁,也可以不是,这取决于闭锁停用引脚的 状态。

V<sub>IN</sub> 和 V<sub>C</sub> 的电源电压可在5 V 至40 V 的范围内单独调节。

| 具值衣<br>(每个通道) <sup>(1)</sup> |      |                |  |  |  |  |  |  |  |

|------------------------------|------|----------------|--|--|--|--|--|--|--|

| INV.                         | N.I. | <b>OUT</b> 之间) |  |  |  |  |  |  |  |

| Н                            | Н    | L              |  |  |  |  |  |  |  |

| L                            | Н    | Н              |  |  |  |  |  |  |  |

| Н                            | L    | L              |  |  |  |  |  |  |  |

| L                            | L    | L              |  |  |  |  |  |  |  |

古仕士

(1) <u>OUT = INV</u> and N.I. OUT 之间) = INV or N.I.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

www.ti.com.cn

ZHCS145-MARCH 2011

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## BLOCK DIAGRAM

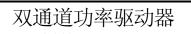

### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|-----------------------|------------------|

| –55°C to 125°C |                        | 5962-8761901VEA       | 5962-8761901VEA  |

|                | (J) CDIP               | 5962-8761903VEA       | 5962-8761903VEA  |

|                | (W) CFP                | 5962-8761903VFA       | 5962-8761903VFA  |

|                | (FK) LCCC              | 5962-8761901V2A       | 5962-8761901V2A  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

#### ZHCS145-MARCH 2011

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                      |                                                           |                                                                                    | MIN | MAX             | UNIT |  |  |

|----------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------|--|--|

| V <sub>IN</sub>      | Supply voltage                                            |                                                                                    |     | 40              | V    |  |  |

| V <sub>C</sub>       | Collector supply voltage                                  | Collector supply voltage Output current (each output, source or sink) steady-state |     |                 |      |  |  |

|                      | Output current (each output, source or sink) steady-state |                                                                                    |     |                 |      |  |  |

|                      | Peak transient                                            |                                                                                    | ±1  | А               |      |  |  |

|                      | Capacitive discharge energy                               |                                                                                    |     | 15              | mJ   |  |  |

|                      | Digital inputs <sup>(1)</sup>                             |                                                                                    |     | 5.5             | V    |  |  |

|                      | Analog stop inputs                                        |                                                                                    |     | $V_{\text{IN}}$ |      |  |  |

| TJ                   | Operating virtual-junction temperature                    |                                                                                    |     | 150             | °C   |  |  |

|                      |                                                           | J package                                                                          |     | 9.6<br>8.3 °C/W |      |  |  |

| $\theta_{\text{JC}}$ | Package thermal impedance, junction to $case^{(2)(3)}$    | W package                                                                          |     |                 | °C/W |  |  |

|                      |                                                           | FK package                                                                         |     | 9.5             |      |  |  |

|                      |                                                           | J package                                                                          |     | 13              |      |  |  |

|                      | Power dissipation at $T_{case} = 25^{\circ}C^{(1)}$       | W package                                                                          |     | 15              |      |  |  |

|                      |                                                           |                                                                                    | 13  |                 |      |  |  |

|                      | Operating temperature range                               |                                                                                    | -55 | 125             | °C   |  |  |

|                      | Storage temperature range                                 |                                                                                    | -65 | 150             | °C   |  |  |

|                      | Lead temperature (soldering, 10 seconds)                  |                                                                                    |     | 300             | °C   |  |  |

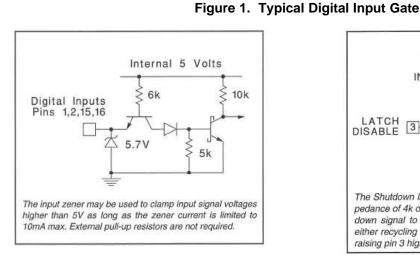

(1) All voltages are with respect to the four ground pins which must be connected together. All currents are positive into, negative out of the specified terminal. Digital drive can exceed 5.5 V if input current is limited to 10 mA. Consult packaging section of databook for thermal limitations and considerations of package.

(2) Maximum power dissipation is a function of  $T_J$  (max),  $\theta_{JC}$ , and  $T_C$ . The maximum allowable power dissipation at any allowable case temperature is  $P_D = (T_J (max) - T_C)/\theta_{JC}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability.

(3) The package thermal impedance is calculated in accordance with MIL-STD-883.

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to  $125^{\circ}C$ ;  $V_{IN} = V_C = 20$  V.  $T_A = T_J$ .

|                                 | PARAMETER                                      | TEST                                           | TEST CONDITIONS            |     |       |      |    |

|---------------------------------|------------------------------------------------|------------------------------------------------|----------------------------|-----|-------|------|----|

| V <sub>IN</sub>                 | Supply current                                 | V <sub>IN</sub> = 40 V                         |                            | 12  | 15    | mA   |    |

| V <sub>C</sub>                  | Supply current                                 | $V_{\rm C} = 40$ V, outputs low                | N                          |     | 5.2   | 7.5  | mA |

| V <sub>C</sub>                  | Leakage current                                | V <sub>IN</sub> = 0, V <sub>C</sub> - 30 V, no | load                       |     | 0.05  | 0.1  | mA |

|                                 | Digital input low level                        |                                                |                            |     |       | 0.8  | V  |

|                                 | Digital input high level                       |                                                |                            | 2.2 |       |      | V  |

|                                 | Input current                                  | V <sub>1</sub> = 0                             |                            |     | -0.06 | -1.0 | mA |

|                                 | Input leakage                                  | V <sub>1</sub> = 5 V                           |                            |     | 0.05  | 0.1  | mA |

| ., .,                           | Output high act                                | I <sub>O</sub> = -50 mA                        |                            |     | 2.0   | V    |    |

| v <sub>C</sub> – v <sub>O</sub> | <sub>C</sub> – V <sub>O</sub> Output high sat. | I <sub>O</sub> = -500 mA                       |                            |     | 2.5   | v    |    |

| V                               | Output low sat.                                | I <sub>O</sub> = -50 mA                        |                            |     | 0.4   | v    |    |

| Vo                              | Output low sat.                                | I <sub>O</sub> = -500 mA                       | I <sub>O</sub> = -500 mA   |     |       | 2.5  |    |

|                                 | Appleg threshold                               |                                                | 8761901                    | 100 | 130   | 150  |    |

|                                 | Analog threshold                               | $V_{CM} = 0$ to 15 V                           | 8761903                    | 90  | 130   | 150  | mV |

|                                 | Input bias current                             | $V_{CM} = 0$                                   | $V_{CM} = 0$               |     | -10   | -20  | μA |

|                                 | Thermal shutdown                               |                                                |                            | 155 |       | °C   |    |

|                                 | Shutdown threshold                             | Pin 7 input                                    | Pin 7 input<br>Pin 3 input |     |       | 2.2  | V  |

|                                 | Latch disable threshold                        | Pin 3 input                                    |                            |     |       | 2.2  | V  |

## TYPICAL SWITCHING CHARACTERISTICS

$V_{IN} = V_C = 20$  V,  $T_A = 25^{\circ}$ C. Delays measured to 10% output change.

| PARAMETER                                              | TEST CONDITIONS        | OUT  | OUTPUT CL = |     |    |

|--------------------------------------------------------|------------------------|------|-------------|-----|----|

| From Inv. Input to Output                              |                        | open | 1.0         | 2.2 | nF |

| Rise time delay                                        |                        | 40   | 50          | 60  | ns |

| 10% to 90% rise                                        |                        | 25   | 40          | 50  | ns |

| Fall time delay                                        |                        | 30   | 40          | 50  | ns |

| 90% to 10% fall                                        |                        | 25   | 40          | 50  | ns |

| From N.I. Input to Output                              |                        |      |             |     |    |

| Rise time delay                                        |                        | 30   | 40          | 50  | ns |

| 10% to 90% rise                                        |                        | 25   | 40          | 50  | ns |

| Fall time delay                                        |                        | 45   | 55          | 65  | ns |

| 90% to 10% fall                                        |                        | 25   | 40          | 50  | ns |

| V <sub>C</sub> cross-conduction current spike duration | Output rise            | 25   |             |     | ns |

|                                                        | Output fall            | 0    |             |     | ns |

| Analog shutdown delay                                  | Stop non-Inv. = 0 V    | 180  |             |     | ns |

|                                                        | Stop Inv. = 0 to 0.5 V | 180  |             |     | ns |

| Digital shutdown delay                                 | 2 V input on Pin 7     | 50   |             |     | ns |

www.ti.com.cn

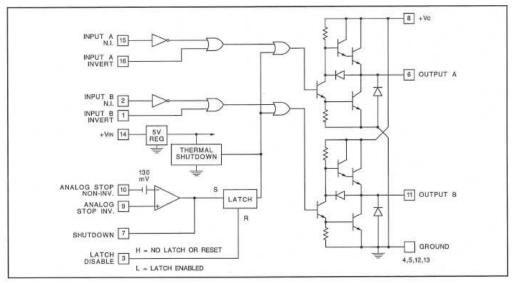

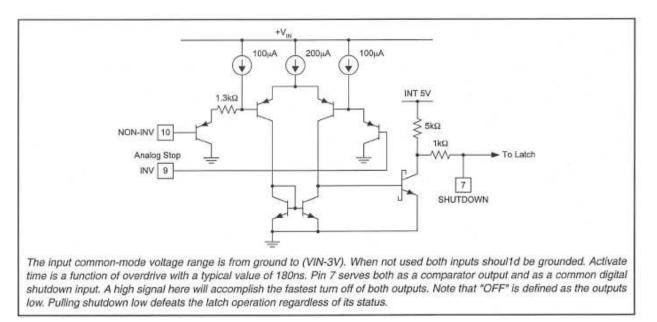

### SIMPLIFIED INTERNAL CIRCUITRY

Figure 2. Typical Digital Input Gate

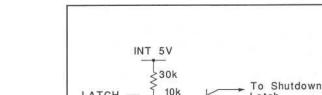

Figure 3. Latch Disable

www.ti.com.cn

### SIMPLIFIED INTERNAL CIRCUITRY (continued)

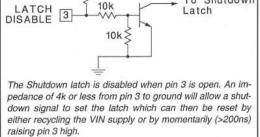

Figure 4. Use of the Shutdown Pin

### SHUTDOWN CIRCUIT DESCRIPTION

The function of the circuitry is to be able to provide a shutdown of the device. This is defined as functionality that will drive both outputs to the low state. There are three different inputs that govern this shutdown capability.

- Analog Stop Pins The differential inputs to this comparator provide a way to execute a shutdown.

- Latch Disable Pin Assuming that the Shutdown pin is left open, a high on this pin disables the latching functionality of the Analog Stop shutdown. A low on this pin enables the latching functionality of the Analog Stop shutdown occurs through the Analog Stop circuit while Latch Disable is high, then the outputs will go low, but will return to normal operation as soon as the Analog Stop circuit allows it. If a shutdown occurs through the Analog Stop circuit while Latch Disable is low, then the outputs will go low and remain low even if the Analog Stop circuit no longer drives the shutdown. The outputs will remain "latched" low (in shutdown) until the Latch Disable goes high and the Analog Stop circuit allows it to return from shutdown or the VIN voltage is cycled to 0V and then returned above 5V.

- Shutdown Pin This pin serves two purposes.

- 1. It can be used as an output of the Analog Stop circuit.

- 2. It can be used as an input to force a shutdown or to force the device out of shutdown. This pin can override both the Analog Stop circuit as well as the Latch Disable Pin. When driving hard logic levels into the Shutdown pin, the Latch Disable functionality will be overridden and the Latch Disable will not function as it does when used in conjunction with the Analog Stop circuit. When the Shutdown pin is high, the outputs will be in the low state (shutdown). When the Shutdown pin is low (hard logic low) the outputs will operate normally, regardless of the state of the Latch Disable pin or the Analog Stop pins.

In order to use the Shutdown Pin with the Latch Disable functional it is necessary to use either a diode in series with the Shutdown signal or to use an open collector pull-up so that the Shutdown pin is not pulled low. This configuration will allow the Latch Disable function to work with the Shutdown pin.

#### ZHCS145-MARCH 2011

## SIMPLIFIED INTERNAL CIRCUITRY (continued) Table 1. UG1707 SHUTDOWN TRUTH TABLE

| ANALOG STOP<br>LOGIC | SHUTDOWN | LATCH DISABLE | PREVIOUS STATE OF<br>OUTPUT | Ουτρυτ                          |

|----------------------|----------|---------------|-----------------------------|---------------------------------|

| Х                    | 0        | Х             | Х                           | Follows Input Logic             |

| Х                    | 1        | Х             | Х                           | Low (Shutdown)                  |

| 1                    | Open     | Х             | Х                           | Low (Shutdown)                  |

| 0                    | Open     | 0             | Shutdown                    | <sup>(1)</sup> Latched Shutdown |

| 0                    | Open     | 0             | Normal                      | Follows Input Logic             |

| 0                    | Open     | 1             | Х                           | Follows Input Logic             |

(1) If the output was previously in Shutdown and Latch Disable was low and stays low, then even if the Analog Stop Logic is changed or the Shutdown pin is open, the outputs will remain in Shutdown.

Figure 5. Transformer Coupled Push-Pull MOSFET Drive Circuit

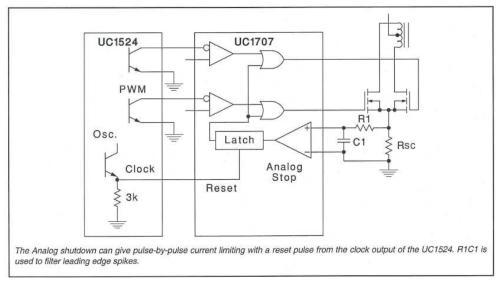

Figure 6. Current Limiting

ZHCS145-MARCH 2011

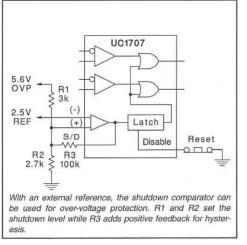

Figure 7. Over-Voltage Protection

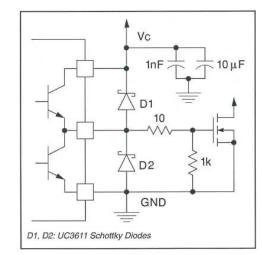

Figure 8. Power MOSFET Drive Circuit

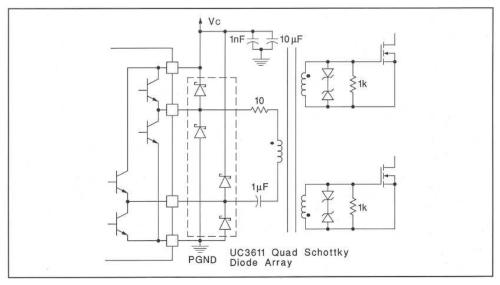

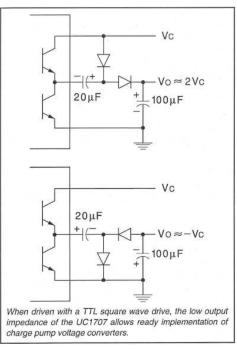

Figure 9. Charge Pump Circuits

www.ti.com.cn

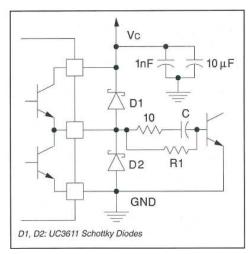

Figure 10. Power Bipolar Drive Circuit

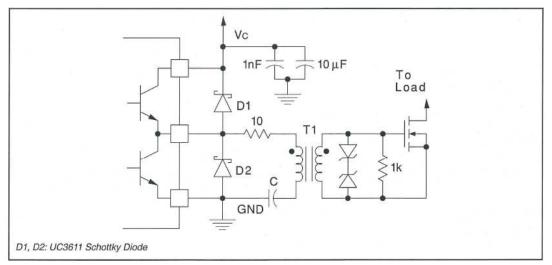

Figure 11. Transformer Coupled MOSFET Drive Circuit

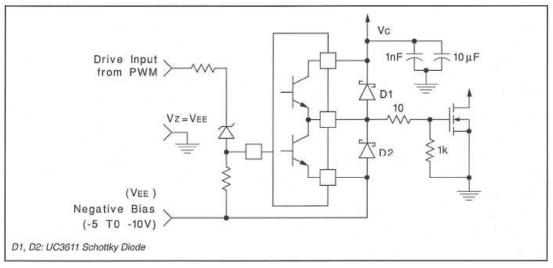

Figure 12. Power MOSFET Drive Circuit Using Negative Bias Voltage and Level Shifting to Ground Reference PWM

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)     | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5)                | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|---------------------|--------------------------------------|----------------------|--------------|----------------------------------------|---------|

| 5962-8761901V2A  | ACTIVE        | LCCC         | FK                 | 20   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-<br>8761901V2A<br>UC1707L<br>QMLV | Samples |

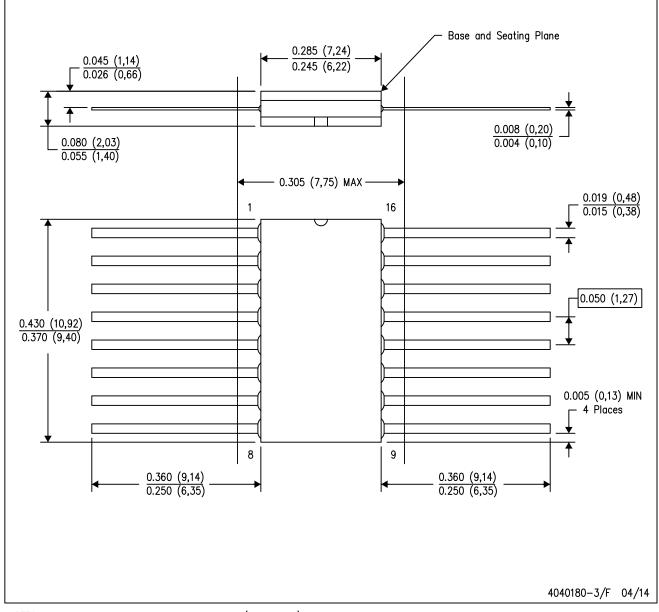

| 5962-8761901VEA  | ACTIVE        | CDIP         | J                  | 16   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-8761901VE<br>A<br>UC1707JQMLV     | Samples |

| 5962-8761903V2A  | ACTIVE        | LCCC         | FK                 | 20   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-<br>8761903V2A<br>UC1707L-SP      | Samples |

| 5962-8761903VEA  | ACTIVE        | CDIP         | J                  | 16   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-8761903VE<br>A<br>UC1707J-SP      | Samples |

| 5962-8761903VFA  | ACTIVE        | CFP          | W                  | 16   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-8761903VF<br>A<br>UC1707W-SP      | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

#### www.ti.com

# PACKAGE OPTION ADDENDUM

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC1707-SP :

• Catalog : UC1707

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

W (R-GDFP-F16)

CERAMIC DUAL FLATPACK

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL STD 1835 GDFP2-F16

# FK 20

## 8.89 x 8.89, 1.27 mm pitch

# **GENERIC PACKAGE VIEW**

## LCCC - 2.03 mm max height

LEADLESS CERAMIC CHIP CARRIER

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

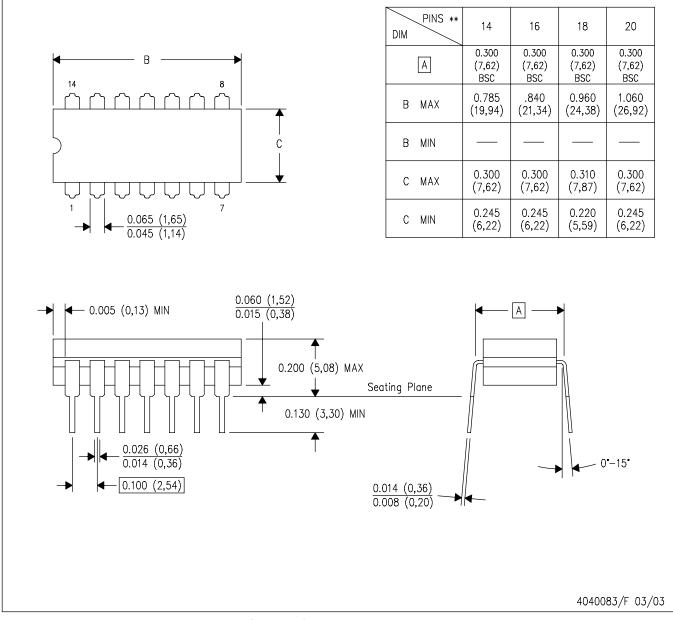

J (R-GDIP-T\*\*) 14 LEADS SHOWN

CERAMIC DUAL IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司