## ADS9224R ADS9234R

ZHCSIJ5C - AUGUST 2018 - REVISED JUNE 2019

# ADS92x4R 双通道低延迟同步采样 SAR ADC

# 1 特性

• 高分辨率、高吞吐量:

INSTRUMENTS

Texas

- ADS9224R: 16 位、3MSPS、低延迟: 333ns

- ADS9234R: 14 位、3.5MSPS、低延 迟: 285ns

- 两个单极、完全差分同步采样通道

- 出色的直流和交流性能:

- ADS9224R:

- 16 位 NMC DNL,±2LSB 最大 INL

- 94dB SNR、 –109dB THD

- 1MHz 时为 88dB SINAD

- ADS9234R:

- 14 位 NMC DNL,±1LSB 最大 INL

- 85.6dB SNR、-106dB THD

- 1MHz 时为 84dB SINAD

- 特性集成:

- 内部基准和基准缓冲器

- 用于设置共模的内部 REFby2 缓冲器

- 数据平均

- 适用于 MCU 和 FPGA 的增强型 SPI 接口:

- 宽读取周期,可借助 MCU 读取数据

- 用于通过数字隔离器进行数据传输的时钟重计时器

- 适用于 FPGA 的 DDR 模式

- 并行字节模式,方便对接

- 扩展温度范围: -40℃ 至 +125℃

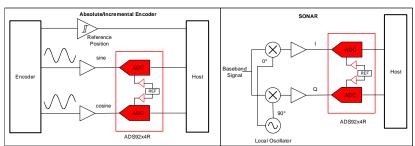

# 2 应用

- 光学编码器: 增量和绝对编码器

- 声纳接收器

- 光纤网络: EDFA 增益控制环路

- 电源质量测量

- 数字电源

- I/Q 解调器

- 医疗成像: CT 扫描仪、MRI 扫描仪

- 阻抗分析仪

# 3 说明

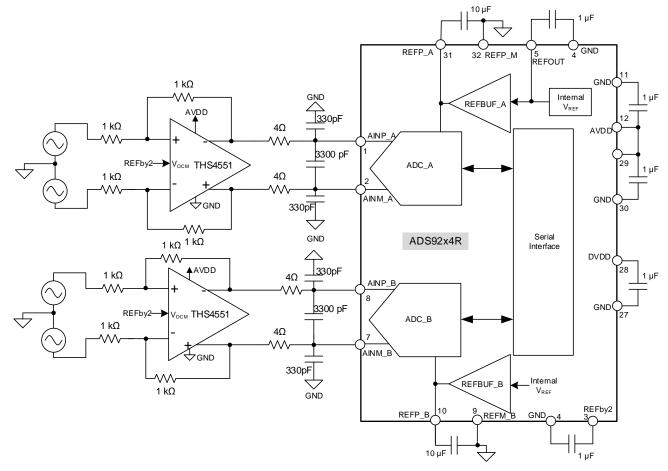

ADS92x4R 是一款引脚兼容型高速双通道同步采样模数转换器 (ADC),具有集成基准电压和基准电压缓冲器。该器件可由 5V 单电源供电运行,支持单极和全差分模拟输入信号,具有出色的直流和交流规格。该器件具有高达 1.5MHz 的模拟输入频率,交流性能出色,因此适合高带宽数据采集 (DAQ)系统。

该器件支持 SPI 兼容串行(增强型 SPI)和字节宽并 行接口,因此易于与多种微控制器、数字信号处理器 (DSP)和现场可编程门阵列 (FPGA) 搭配使用。此器 件还支持数据平均功能,该功能可提升高噪声环境中的 交流性能。

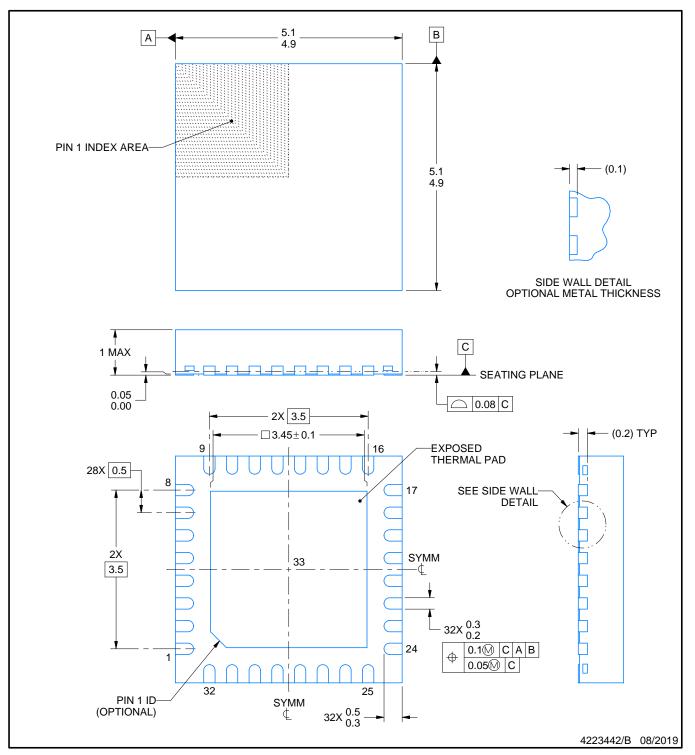

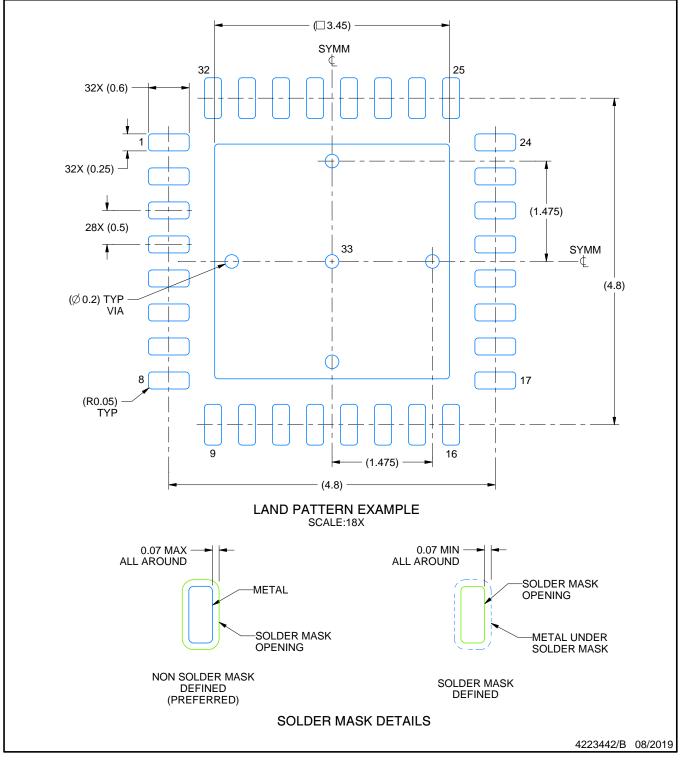

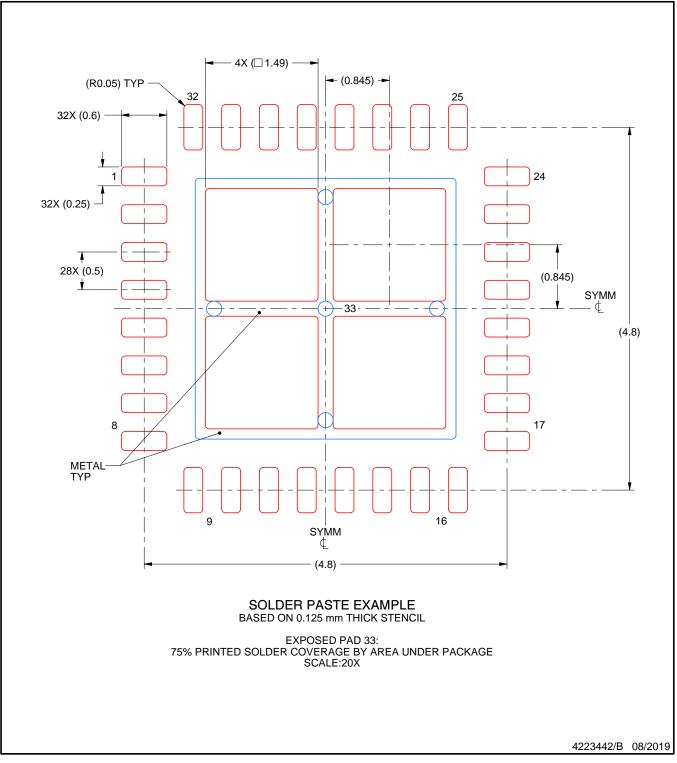

该器件采用节省空间的 5mm × 5mm VQFN 封装。 ADS92x4R 的额定扩展温度范围为 –40°C 至 +125° C。

|          | 器件信息 <sup>(1)</sup> |                 |

|----------|---------------------|-----------------|

| 器件型号     | 封装                  | 封装尺寸(标称值)       |

| ADS92x4R | VQFN (32)           | 5.00mm x 5.00mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

# 典型应用图

# 目录

| 1 | 特性   |                                      | 1  |

|---|------|--------------------------------------|----|

| 2 | 应用   |                                      | 1  |

| 3 | 说明   |                                      | 1  |

| 4 | 修订   | 历史记录                                 | 2  |

| 5 | Pin  | Configuration and Functions          | 3  |

| 6 | Spe  | cifications                          | 5  |

|   | 6.1  | Absolute Maximum Ratings             | 5  |

|   | 6.2  | ESD Ratings                          | 5  |

|   | 6.3  | Recommended Operating Conditions     | 5  |

|   | 6.4  | Thermal Information                  | 5  |

|   | 6.5  | Electrical Characteristics: ADS92x4R | 6  |

|   | 6.6  | Electrical Characteristics: ADS9224R | 7  |

|   | 6.7  | Electrical Characteristics: ADS9234R |    |

|   | 6.8  | Timing Requirements                  | 9  |

|   | 6.9  | Switching Characteristics            | 10 |

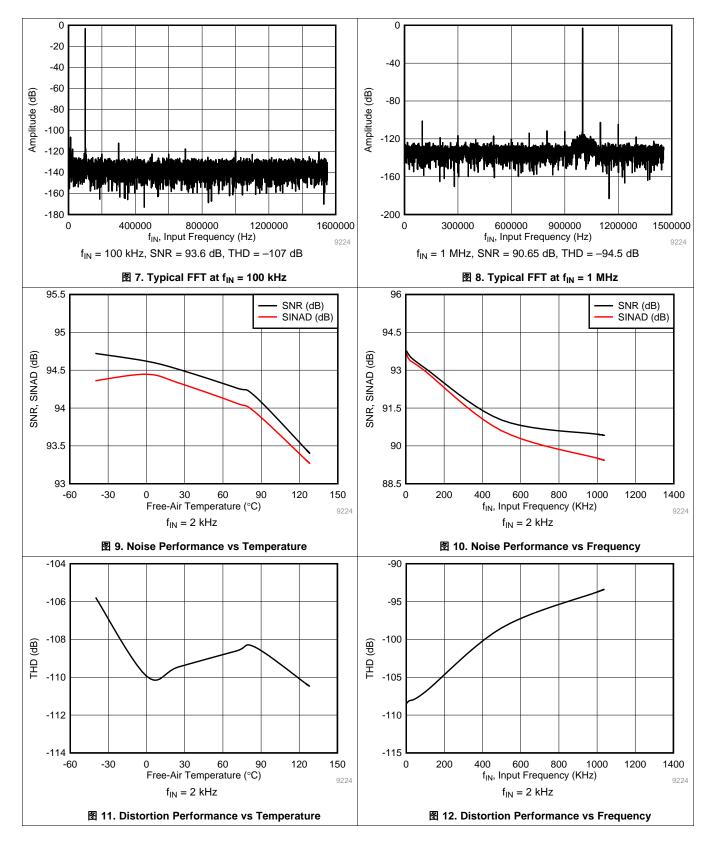

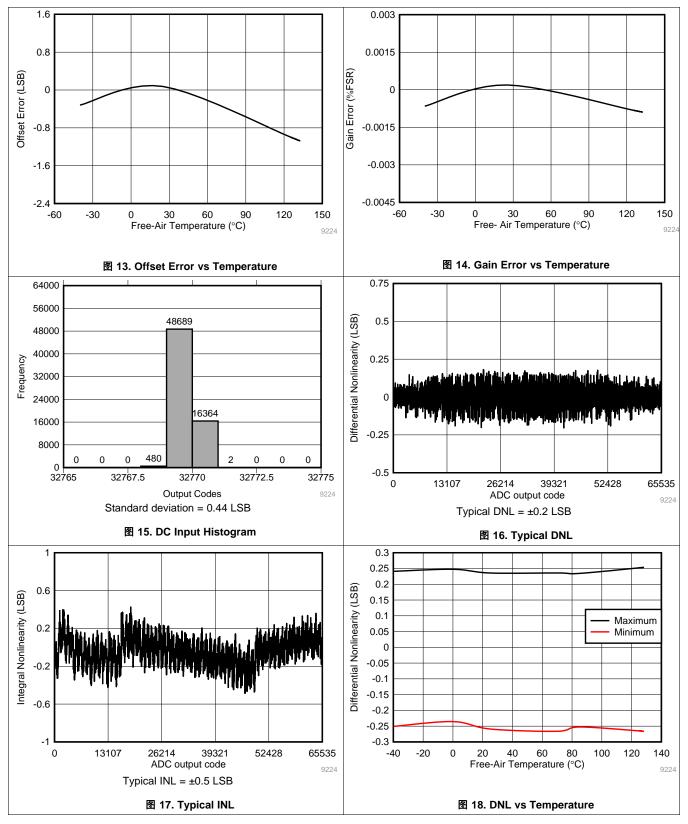

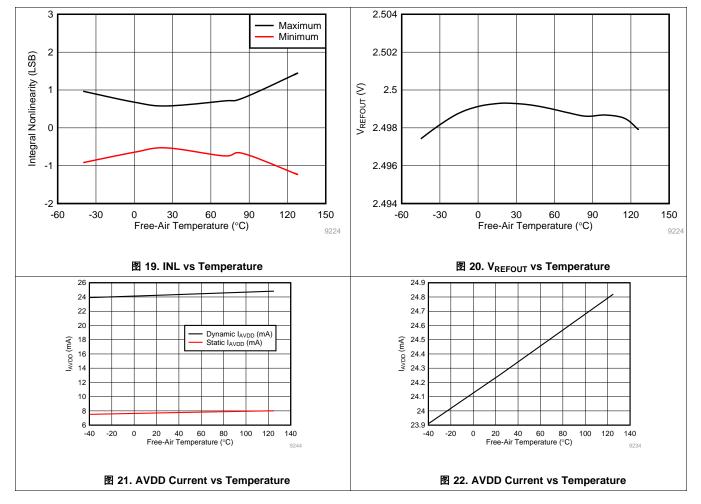

|   | 6.10 | Typical Characteristics: ADS9224R    | 15 |

|   | 6.11 | Typical Characteristics: ADS9234R    | 18 |

| 7 | Deta | iled Description 2                   | 21 |

|   | 7.1  | Overview                             | 21 |

|   | 7.2  | Functional Block Diagram             | 21 |

|   | 7.3  | Feature Description                  | 22 |

|    | 7.4   | Device Functional Modes    | 26 |

|----|-------|----------------------------|----|

|    | 7.5   | READY/STROBE Output        | 30 |

|    | 7.6   | Programming                | 30 |

|    | 7.7   | Register Maps              | 43 |

| 8  | Appli | ication and Implementation | 49 |

|    | 8.1   | Application Information    | 49 |

|    | 8.2   | Typical Application        | 51 |

| 9  | Powe  | er Supply Recommendations  | 53 |

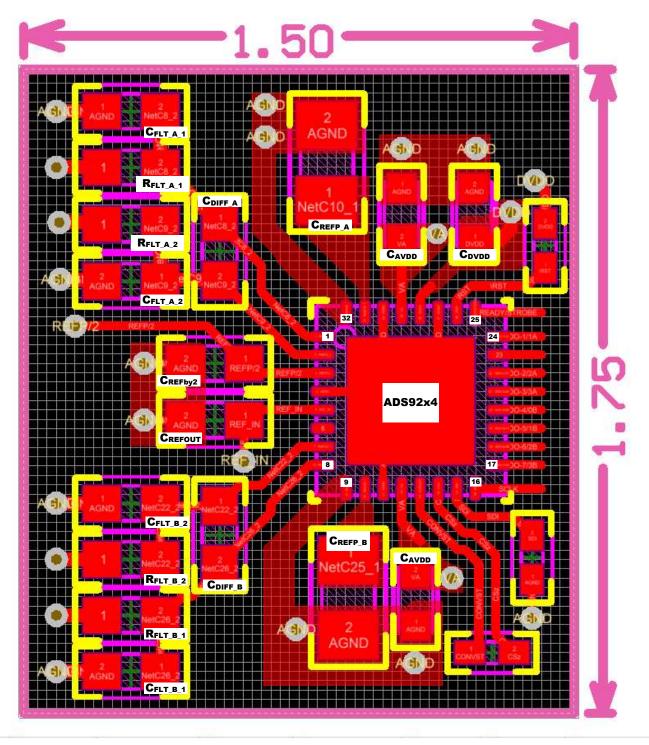

| 10 | Layo  | out                        | 54 |

|    | 10.1  | Layout Guidelines          | 54 |

|    | 10.2  | Layout Example             | 55 |

| 11 | 器件    | 和文档支持                      | 56 |

|    | 11.1  | 器件支持                       | 56 |

|    | 11.2  | 相关文档                       | 56 |

|    | 11.3  | 相关链接                       | 56 |

|    | 11.4  | 接收文档更新通知                   | 56 |

|    | 11.5  | 社区资源                       | 56 |

|    | 11.6  | 商标                         | 56 |

|    | 11.7  | 静电放电警告                     | 56 |

|    | 11.8  | Glossary                   | 56 |

| 12 | 机械    | 、封装和可订购信息                  | 57 |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#### Changes from Revision B (May 2019) to Revision C

| Page |

|------|

|------|

已更改 将文档状态从"预告信息"更改为"生产数据"......1

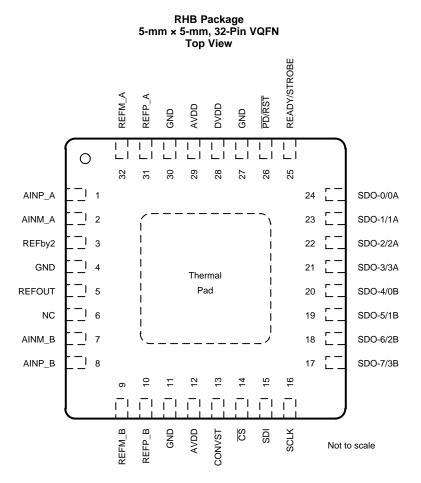

# 5 Pin Configuration and Functions

**Pin Functions**

| PIN           |               |                |                                                                                                                                                                          |

|---------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.           | FUNCTION       | DESCRIPTION                                                                                                                                                              |

| AINM_A        | 2             | Analog input   | Negative analog input for channel A.                                                                                                                                     |

| AINM_B        | 7             | Analog input   | Negative analog input for channel B.                                                                                                                                     |

| AINP_A        | 1             | Analog input   | Positive analog input for channel A.                                                                                                                                     |

| AINP_B        | 8             | Analog input   | Positive analog input for channel B.                                                                                                                                     |

| AVDD          | 12, 29        | Power supply   | Analog power-supply pin.<br>Connect a 1- $\mu$ F decoupling capacitor between pin 12 and pin 11.<br>Connect a 1- $\mu$ F decoupling capacitor between pin 29 and pin 30. |

| CONVST        | 13            | Digital input  | Conversion start input pin.<br>A CONVST rising edge starts the conversion for ADC_A and ADC_B.                                                                           |

| <del>cs</del> | 14            | Digital input  | Chip-select input pin; active low.<br>The host and device can communicate when $\overline{CS}$ is low.<br>The SDO-x pins go to Hi-Z when $\overline{CS}$ is high.        |

| DVDD          | 28            | Power supply   | Interface power-supply pin. Connect a $1-\mu$ F decoupling capacitor between pin 27 and pin 28.                                                                          |

| GND           | 4, 11, 27, 30 | Power supply   | Ground                                                                                                                                                                   |

| NC            | 6             | —              | No external connection                                                                                                                                                   |

| PD/RST        | 26            | Digital input  | Asynchronous reset or power-down input pin.<br>See the <i>Reset or Power-Down</i> section.                                                                               |

| READY/STROBE  | 25            | Digital output | Indicates data ready or strobe output for data capture.                                                                                                                  |

ADS9224R ADS9234R ZHCSIJ5C – AUGUST 2018–REVISED JUNE 2019

www.ti.com.cn

# Pin Functions (continued)

| PIN         |     |                |                                                                                                                                               |

|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | FUNCTION       | DESCRIPTION                                                                                                                                   |

| REFby2      | 3   | Analog output  | REFby2 buffer output. Connect a $1-\mu$ F decoupling capacitor between pin 3 and pin 4.                                                       |

| REFOUT      | 5   | Analog output  | Internal reference output. Connect a $1-\mu$ F decoupling capacitor between pin 5 and pin 4.                                                  |

| REFM_A      | 32  | Analog output  | Negative output of reference buffer A. Negative reference input for ADC_A.<br>Externally connect to the device GND.                           |

| REFM_B      | 9   | Analog output  | Negative output of reference buffer B. Negative reference input for ADC_B.<br>Externally connect to the device GND.                           |

| REFP_A      | 31  | Analog output  | Positive output of reference buffer A. Positive reference input for ADC_A.<br>Connect a 10-µF decoupling capacitor between pin 31 and pin 32. |

| REFP_B      | 10  | Analog output  | Positive output of reference buffer B. Positive reference input for ADC_B.<br>Connect a 10-µF decoupling capacitor between pin 9 and pin 10.  |

| SCLK        | 16  | Digital input  | Clock input pin for the serial interface.                                                                                                     |

| SDI         | 15  | Digital input  | Serial data input pin.<br>This pin is used to program the device registers.                                                                   |

| SDO-0/0A    | 24  | Digital output | SPI mode: data output 0 for channel A.<br>Parallel byte mode: least significant bit (LSB) from the data byte.                                 |

| SDO-1/1A    | 23  | Digital output | SPI mode: data output 1 for channel A.<br>Parallel byte mode: LSB+1 from the data byte.                                                       |

| SDO-2/2A    | 22  | Digital output | SPI mode: data output 2 for channel A.<br>Parallel byte mode: LSB+2 from the data byte.                                                       |

| SDO-3/3A    | 21  | Digital output | SPI mode: data output 3 for channel A.<br>Parallel byte mode: LSB+3 from the data byte.                                                       |

| SDO-4/0B    | 20  | Digital output | SPI mode: data output 0 for channel B.<br>Parallel byte mode: LSB+4 from the data byte.                                                       |

| SDO-5/1B    | 19  | Digital output | SPI mode: data output 1 for channel B.<br>Parallel byte mode: LSB+5 from the data byte.                                                       |

| SDO-6/2B    | 18  | Digital output | SPI mode: data output 2 for channel B.<br>Parallel byte mode: LSB+6 from the data byte.                                                       |

| SDO-7/3B    | 17  | Digital output | SPI mode: data output 3 for channel B.<br>Parallel byte mode: most significant bit (MSB) from the data byte.                                  |

| Thermal pad |     | Power supply   | Exposed thermal pad. TI recommends connecting this pin to the printed circuit board (PCB) ground.                                             |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                            | MIN       | MAX        | UNIT |

|------------------------------------------------------------|-----------|------------|------|

| AVDD to GND                                                | -0.3      | 6          | V    |

| DVDD to GND                                                | -0.3      | 6          | V    |

| Digital input pins                                         | GND – 0.3 | DVDD + 0.3 | V    |

| Digital output pins                                        | GND – 0.3 | DVDD + 0.3 | V    |

| AINP_A, AINP_B to GND, AINM_A, AINM_B to GND               | -0.3      | AVDD + 0.3 | V    |

| REFM_A, REFM_B                                             | GND – 0.1 | GND + 0.1  | V    |

| REFP_A, REFP_B, REFOUT, REFby2 to GND                      | GND – 0.3 | AVDD + 0.3 | V    |

| Input or output current to any pin except power-supply pin | -10       | 10         | mA   |

| Junction temperature, T <sub>J</sub>                       |           | 150        | °C   |

| Storage temperature, T <sub>stg</sub>                      | -65       | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>           | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                          | MIN  | NOM | MAX | UNIT |

|----------------|------------------------------------------|------|-----|-----|------|

| AVDD           | Analog supply voltage                    | 4.5  | 5   | 5.5 | V    |

|                | Digital supply voltage operating range   | 1.65 | 3.3 | 5.5 | V    |

| DVDD           | Digital supply voltage for SCLK > 20 MHz | 2.35 | 3.3 | 5.5 | V    |

| T <sub>A</sub> | Ambient temperature                      | -40  |     | 125 | °C   |

#### 6.4 Thermal Information

|                       |                                              | ADS92x4R   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | UNIT |

|                       |                                              | 32 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 29         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17.1       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.4        | °C/W |

| $\Psi_{\text{JT}}$    | Junction-to-top characterization parameter   | 0.2        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 9.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.8        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics: ADS92x4R

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REFP_X/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

|                                                | PARAMETER                                        | TEST CONDITIONS                                                            | MIN        | TYP    | MAX      | UNIT              |

|------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|------------|--------|----------|-------------------|

| ANALOG INPUT                                   |                                                  |                                                                            |            |        |          |                   |

| FSR <sup>(1)</sup>                             | Full-scale input voltage (AINP_x - AINM_x)       |                                                                            | -4.096     |        | 4.096    | V                 |

| V <sub>IN</sub>                                | Absolute input voltage (AINP_x or AINM_x to GND) |                                                                            | 0          |        | 4.096    | V                 |

| / <sub>CM</sub>                                | Common-mode input range                          |                                                                            | 1.848      |        | 2.248    | V                 |

| IN                                             | Analog input leakage current                     |                                                                            |            | ±1     |          | μA                |

|                                                |                                                  | Sample mode                                                                |            | 16     |          | - 5               |

| C <sub>i</sub>                                 | Input capacitance                                | Hold mode                                                                  |            | 1      |          | pF                |

| BW                                             | Analog input handwidth                           | -3-dB input signal                                                         |            | 52     |          | MHz               |

| 200                                            | Analog input bandwidth                           | -0.1-dB input signal                                                       |            | 4.2    |          | MHz               |

| OLTAGE REFE                                    | RENCE OUTPUT                                     |                                                                            |            |        |          |                   |

| REFOUT <sup>(2)</sup>                          | REFOUT voltage                                   |                                                                            | 2.496      | 2.5    | 2.504    | V                 |

| ΔV <sub>REF</sub> /ΔT                          | V <sub>REFOUT</sub> drift                        |                                                                            |            | 5.5    | 15       | ppm/°C            |

| ∆V <sub>REFOUT</sub> /∆AVD<br>D                | V <sub>REFOUT</sub> line regulation              | AVDD variation 4.5 V to 5.5 V                                              |            | 200    |          | μV/V              |

| REFOUT                                         | REFOUT output current capability                 | $ \Delta V_{REF}  < 2 \text{ mV}$                                          |            | 1.5    |          | μA                |

| CREFOUT                                        | REFOUT capacitor                                 | For specified performance                                                  |            | 1      |          | μF                |

| NTERNAL REFE                                   | RENCE BUFFER                                     |                                                                            |            |        |          |                   |

| GREFBUF                                        | Reference buffer Gain                            |                                                                            |            | 1.6388 |          | V/V               |

| O-REFBUF                                       | Reference buffer output offset                   |                                                                            | -1         | ±0.2   | 1        | mV                |

| ΔE <sub>O-REFBUF</sub> /ΔT                     | Reference buffer output offset temperature drift |                                                                            |            | 10     |          | µV/⁰C             |

| V <sub>refp_a</sub> -<br>V <sub>refp_b</sub> ) | Reference buffer output mismatch                 |                                                                            | -500       | ±50    | 500      | μV                |

| REFP_X                                         | Reference buffer output capacitor                | For specified<br>performance, between<br>each pair of REFP_x<br>and REFM_x | 7          | 10     | 27       | μF                |

| REFby2 OUTPU1                                  | r                                                |                                                                            |            |        |          |                   |

|                                                |                                                  | EN_REFBY2_OFFSET<br>= 0                                                    | 2.043      | 2.048  | 2.053    | V                 |

| V <sub>REFby2</sub>                            | REFby2 output voltage                            | EN_REFBY2_OFFSET<br>= 1                                                    | 2.133      | 2.148  | 2.163    | V                 |

| REFby2                                         | REFby2 output current capability                 |                                                                            |            | ±3     |          | mA                |

|                                                | REFby2 output capacitor                          |                                                                            | 1          |        |          | μF                |

|                                                | REFby2 output noise                              | With specified output capacitor                                            |            | 10     |          | μV <sub>RMS</sub> |

| Digital Outputs                                |                                                  |                                                                            |            |        |          |                   |

| / <sub>он</sub>                                | High level output voltage                        | I <sub>OH</sub> = 500-µA source                                            | 0.8 × DVDD |        | DVDD     | V                 |

| / <sub>OL</sub>                                | Low level output voltage                         | I <sub>OL</sub> = 500-µA sink                                              | 0          | 0.     | 2 × DVDD | V                 |

| Digital Inputs                                 |                                                  |                                                                            |            |        | ·        |                   |

| / <sub>IH</sub>                                | High level input voltage                         |                                                                            | 0.7 × DVDD | D      | VDD +0.3 | V                 |

| / <sub>IL</sub>                                | Low level intput voltage                         | DVDD > 2.3 V                                                               | -0.3       | 0.     | 3 × DVDD | V                 |

| √ <sub>IH</sub>                                | High level input voltage                         |                                                                            | 0.8 × DVDD | D      | VDD +0.3 | V                 |

| VIL                                            | Low level intput voltage                         | — DVDD ≤ 2.3 V                                                             | -0.3       | 0.     | 2 × DVDD | V                 |

(1) Ideal input span; does not include gain or offset error.

(2) Does not include the variation in voltage resulting from solder shift effects.

### Electrical Characteristics: ADS92x4R (continued)

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REFP_X/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

|                     | PARAMETER                    | TEST CONDITIONS                                                 | MIN  | TYP  | MAX  | UNIT |

|---------------------|------------------------------|-----------------------------------------------------------------|------|------|------|------|

| Power Supply        |                              |                                                                 |      |      |      |      |

| AVDD                | Analog supply voltage        |                                                                 | 4.5  | 5    | 5.5  | V    |

| DVDD                | Digital supply voltage       |                                                                 | 1.65 | 3.3  | 5.5  | V    |

|                     |                              | f <sub>SAMPLE</sub> = 3 MSPS                                    |      | 24.3 | 30.4 | mA   |

| I <sub>AVDD</sub>   | Analog supply current        | AVDD = 5 V, no conversion                                       |      | 7.8  |      | mA   |

|                     |                              | Power down (PD/RST<br>Low)                                      |      | 1    |      | μA   |

| I <sub>DVDD</sub>   | Digital supply current       | $f_{SAMPLE} = 3 MSPS,$<br>$C_{SDO-x/y} = 10 pF$                 |      | 2.8  |      | mA   |

| PSRR <sup>(3)</sup> | Power-supply rejection ratio | 100-mV <sub>PP</sub> Ripple on<br>AVDD of frequency <<br>100kHz |      | 70   |      | dB   |

(3) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.5 dB below fullscale, unless otherwise specified.

### 6.6 Electrical Characteristics: ADS9224R

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REFP_X/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

| PARAMETER               |                                               | TEST CONDITIONS                                                     | MIN   | TYP   | MAX  | UNIT   |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------|-------|-------|------|--------|

| DC ACCURAC              | Y                                             |                                                                     |       |       |      |        |

|                         | Resolution, no missing codes                  |                                                                     | 16    |       |      | Bits   |

| DNL                     | Differential nonlinearity                     |                                                                     | -0.5  | ±0.2  | 0.5  | LSB    |

| INL                     | Integral nonlinearity                         |                                                                     | -2    | ±1    | 2    | LSB    |

| Eo                      | Offset error                                  |                                                                     | -9    | ±1    | 9    | LSB    |

| G <sub>E</sub>          | Cummulative gain error for ADC_x and REFBUF_x |                                                                     | -0.02 | ±0.01 | 0.02 | %FSR   |

| $\Delta G_E / \Delta T$ | Gain drift                                    |                                                                     |       | 5     |      | ppm/°C |

|                         | Transition noise                              | Mid-code, PFS-1000, NFS+1000                                        |       | 0.4   |      | LSB    |

| AC ACCURAC              | Y                                             |                                                                     |       |       |      |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                             | 91.3  | 94.5  |      |        |

| SNR <sup>(1)</sup>      | Signal-to-noise ratio                         | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                            |       | 93    |      | dB     |

| ONIX                    |                                               | $f_{IN}$ = 1 MHz, FSR = -3 dBFS, $f_{SAMPLE}$ = 2.9 MSPS            |       | 89.5  |      | άĐ     |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                             |       | 94.3  |      |        |

| SINAD <sup>(1)(2)</sup> | Signal-to-noise plus distortion               | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                            |       | 92.7  |      | dB     |

|                         |                                               | f <sub>IN</sub> = 1 MHz, FSR = -3 dBFS                              |       | 87.9  |      |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                             |       | -109  |      |        |

| THD <sup>(1)(2)</sup>   | Total harmonic distortion                     | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                            |       | -106  |      | dB     |

|                         |                                               | f <sub>IN</sub> = 1 MHz, FSR = -3 dBFS                              |       | -93   |      |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                             |       | 112   |      |        |

| SFDR <sup>(1)</sup>     | Spurious-free dynamic range                   | $f_{IN}$ = 100 kHz, FSR = -3 dBFS                                   |       | 112   |      | dB     |

|                         |                                               | $f_{IN} = 1 \text{ MHz}, \text{ FSR} = -3 \text{ dBFS}$             |       | 100   |      |        |

| CMRR <sup>(1)</sup>     | Common-mode rejection ratio                   | $f_{IN} = dc \text{ to } 1\text{-}MHz, V_{IN} = 100\text{-}mV_{PP}$ |       | 80    |      | dB     |

(1) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.5 dB below fullscale, unless otherwise specified.

(2) Calculated on the first nine harmonics of the input frequency.

# Electrical Characteristics: ADS9224R (continued)

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REFP_x/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

|                      | PARAMETER | TEST CONDITIONS                                                            | MIN | TYP  | MAX | UNIT |

|----------------------|-----------|----------------------------------------------------------------------------|-----|------|-----|------|

| ISOXT <sup>(1)</sup> |           | $f_{IN\_ADCA}$ = 15 kHz at 10% FSR,<br>$f_{IN\_ADCB}$ = 25 kHz at 100% FSR |     | -120 |     | dB   |

## 6.7 Electrical Characteristics: ADS9234R

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REFP_x/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

| PARAMETER               |                                               | TEST CONDITIONS                                                            | MIN    | TYP   | MAX   | UNIT   |

|-------------------------|-----------------------------------------------|----------------------------------------------------------------------------|--------|-------|-------|--------|

| DC ACCURAC              | Y                                             |                                                                            |        |       |       |        |

|                         | Resolution, no missing codes                  |                                                                            | 14     |       |       | Bits   |

| DNL                     | Differential nonlinearity                     |                                                                            | -0.5   | ±0.15 | 0.5   | LSB    |

| INL                     | Integral nonlinearity                         |                                                                            | -1     | ±0.3  | 1     | LSB    |

| Eo                      | Offset error                                  |                                                                            | -3.5   | ±0.8  | 3.5   | LSB    |

| G <sub>E</sub>          | Cummulative gain error for ADC_x and REFBUF_x |                                                                            | -0.025 | ±0.01 | 0.025 | %FSR   |

| $\Delta G_E / \Delta T$ | Gain drift                                    |                                                                            |        | 5     |       | ppm/°C |

|                         | Transition noise                              | Mid-code, PFS-1000, NFS+1000                                               |        | 0.3   |       | LSB    |

| AC ACCURAC              | Y                                             | ·                                                                          |        |       |       |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                                    | 84.1   | 85.6  |       |        |

| SNR <sup>(1)</sup>      | Signal-to-noise ratio                         | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                                   |        | 85.5  |       | dB     |

|                         |                                               | f <sub>IN</sub> = 1 MHz, FSR = -3 dBFS                                     |        | 85    |       |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                                    |        | 85.5  |       |        |

| SINAD <sup>(1)(2)</sup> | Signal-to-noise plus distortion               | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                                   |        | 85.4  |       | dB     |

|                         |                                               | $f_{IN} = 1 \text{ MHz}, \text{ FSR} = -3 \text{ dBFS}$                    |        | 84.4  |       |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                                    |        | -106  |       |        |

| THD <sup>(1)(2)</sup>   | Total harmonic distortion                     | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                                   |        | -106  |       | dB     |

|                         |                                               | f <sub>IN</sub> = 1 MHz, FSR = -3 dBFS                                     |        | -94   |       |        |

|                         |                                               | f <sub>IN</sub> = 2 kHz                                                    |        | 109   |       |        |

| SFDR <sup>(1)</sup>     | Spurious-free dynamic range                   | f <sub>IN</sub> = 100 kHz, FSR = -3 dBFS                                   |        | 107   |       | dB     |

|                         |                                               | f <sub>IN</sub> = 1 MHz, FSR = -3 dBFS                                     |        | 101   |       |        |

| CMRR <sup>(1)</sup>     | Common-mode rejection ratio                   | $f_{IN} = dc \text{ to } 1\text{-}MHz, V_{IN} = 100\text{-}mV_{PP}$        |        | 75    |       | dB     |

| ISOXT <sup>(1)</sup>    | Channel-to-channel isolation                  | $f_{IN\_ADCA}$ = 15 kHz at 10% FSR,<br>$f_{IN\_ADCB}$ = 25 kHz at 100% FSR |        | -115  |       | dB     |

(1) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.5 dB below fullscale, unless otherwise specified.

(2) Calculated on the first nine harmonics of the input frequency.

#### 6.8 Timing Requirements

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REFP_x/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 5V, D 3.3 V

|                          |                                                                                                    | MIN                              | NOM                         | MAX                   | UNIT   |

|--------------------------|----------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------|-----------------------|--------|

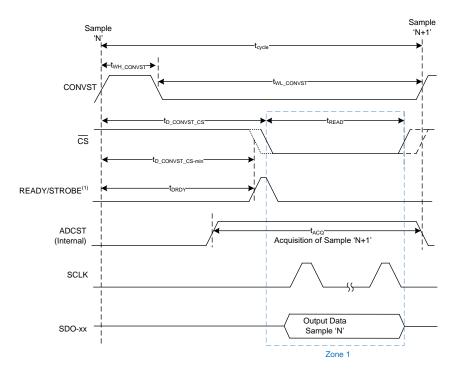

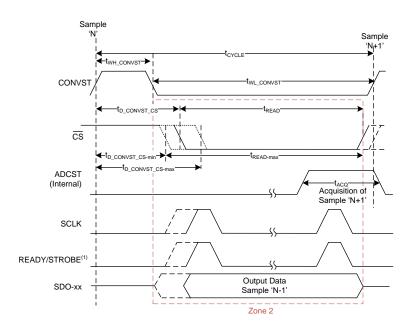

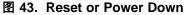

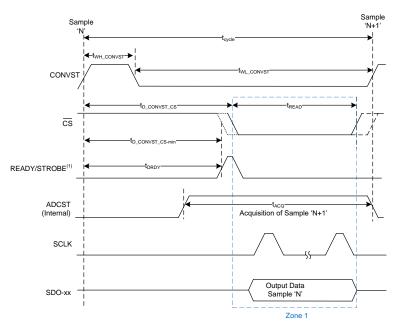

| CONVERSION               | N CONTROL AND DATA TRANSFER (See 图 1 and 图 2)                                                      |                                  |                             |                       |        |

| t <sub>D_CONVST_CS</sub> | Delay time: CONVST high to $\overline{\text{CS}}$ Falling for zero cycle latency (zone 1 transfer) | t <sub>DRDY</sub> <sup>(1)</sup> |                             |                       | ns     |

|                          | Time between two adjacent CONVST rising edges for zero cycle latency (zone 1 transfer)             |                                  | $t_{DRDY} + t_{READ}^{(2)}$ |                       | ns     |

| t <sub>CYCLE</sub>       | Time between two adjacent CONVST rising edges for zone 2 transfer, ADS9224R                        | 333                              |                             |                       | -      |

|                          | Time between two adjacent CONVST rising edges for zone 2 transfer, ADS9234R                        | 285                              |                             |                       | ns     |

| f                        | Sampling rate, ADS9224R                                                                            |                                  |                             | 3                     | MSPS   |

| f <sub>SAMPLE</sub>      | Sampling rate, ADS9234R                                                                            |                                  |                             | 3.5                   | NISE S |

| t <sub>ACQ</sub>         | Acquisition time                                                                                   | 140                              |                             |                       | ns     |

| t <sub>D_CONVST_CS</sub> | Delay time: CONVST high to $\overline{CS}$ falling for zone 2 transfer                             | 15                               |                             | 180                   | ns     |

| t <sub>WL_CONVST</sub>   | Pulse duration : CONVST low                                                                        | 15                               |                             |                       | ns     |

| t <sub>WH_CONVST</sub>   | Pulse duration : CONVST high                                                                       | 15                               |                             |                       | ns     |

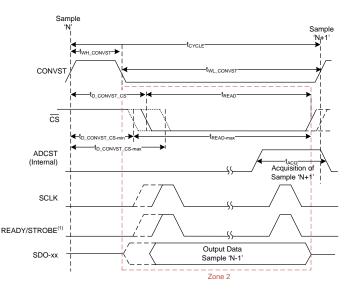

| SPI-COMPAT               | IBLE AND PARALLEL BYTE PROTOCOL (See 图 3)                                                          |                                  |                             |                       |        |

| t <sub>CLK</sub>         | Serial clock time period                                                                           | 1/ f <sub>CLK</sub>              |                             |                       |        |

| t <sub>PH_CLK</sub>      | SCLK high time                                                                                     | 0.45 × t <sub>CLK</sub>          |                             | $0.55 \times t_{CLK}$ | ns     |

| t <sub>PL_CLK</sub>      | SCLK low time                                                                                      | 0.45 × t <sub>CLK</sub>          |                             | $0.55 \times t_{CLK}$ | ns     |

| t <sub>su_cscк</sub>     | Setup time: CS faling to first SCLK capture edge                                                   | 12                               |                             |                       | ns     |

| t <sub>SU_CKDI</sub>     | Setup Time: SDI data valid to SCLK capture edge                                                    | 2.5                              |                             |                       | ns     |

| t <sub>HT_CKDI</sub>     | Hold Time: SCLK capture edge to previous data valid on SDI                                         | 1.5                              |                             |                       | ns     |

| t <sub>HT_CKCS</sub>     | Delay Time: last SCLK capture edge to $\overline{CS}$ rising                                       | 14                               |                             |                       | ns     |

|                          | Serial clock frequency for SPI protocols with single data rate                                     |                                  |                             | 60                    | MHz    |

| f <sub>CLK</sub>         | Serial clock frequency for SPI protocols with double data rate                                     |                                  |                             | 22                    | MHz    |

|                          | Serial clock frequency for parallel byte protocol                                                  |                                  |                             | 45                    | MHz    |

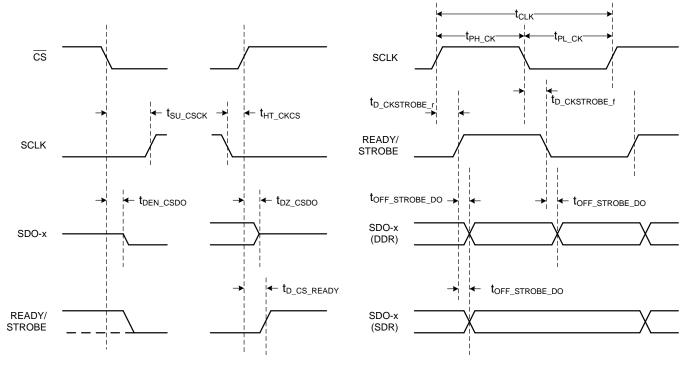

| CLOCK RE-T               | IMER PROTOCOL WITH STROBE = SCLK (EXTERNAL CLOCK) <sup>(3)</sup> (S                                | iee 图 4)                         |                             |                       |        |

| 4                        | Serial clock frequency with single data rate                                                       |                                  |                             | 60                    | MHz    |

| f <sub>CLK</sub>         | Serial clock frequency with double data rate                                                       |                                  |                             | 22                    | MHz    |

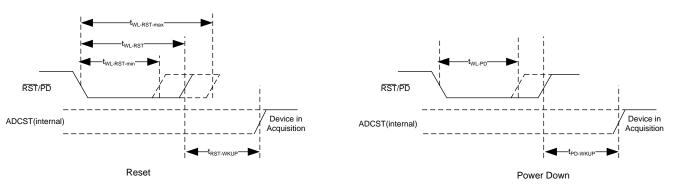

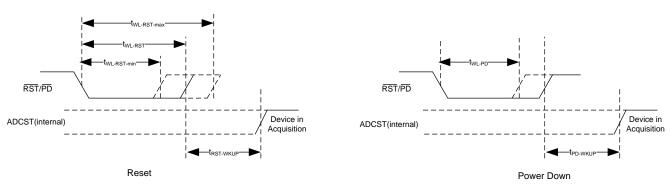

| ASYNCHRON                | OUS RESET AND POWER-DOWN TIMING (See 图 6)                                                          |                                  |                             |                       |        |

| t <sub>WL-RST</sub>      | Pulse duration (low) for reset                                                                     | 50                               |                             | 500                   | ns     |

| t <sub>WL-PD-min</sub>   | Minimum pulse duration (low) for power-down                                                        | 1000                             |                             |                       | ns     |

See Switching Characteristics

See Protocols for Reading From the Device for t<sub>READ</sub>

Other parameters are the same as the SPI-compatible and Parallel Byte Protocols.

ADS9224R ADS9234R ZHCSIJ5C – AUGUST 2018–REVISED JUNE 2019

www.ti.com.cn

#### 6.9 Switching Characteristics

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REF/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

| F                          | PARAMETER                                                             | TEST CONDITIONS                                   | MIN                     | TYP | MAX                     | UNIT |

|----------------------------|-----------------------------------------------------------------------|---------------------------------------------------|-------------------------|-----|-------------------------|------|

| CONVERSION CON             | TROL AND DATA TRANSFER (S                                             | ee 图 1 and 图 2)                                   |                         |     |                         |      |

|                            | Data ready time for present<br>sample: CONVST high to<br>READY high   | Zero cycle latency (zone 1 transfer) for ADS9224R |                         |     | 315                     | ns   |

| t <sub>drdy</sub>          | Data ready time for present<br>sample: CONVST high to<br>READY high   | Zero cycle latency (zone 1 transfer) for ADS9234R |                         |     | 280                     | ns   |

| SPI-COMPATIBLE A           | ND PARALLEL BYTE PROTOCO                                              | DL (See 图 3)                                      |                         |     |                         |      |

| t <sub>DEN_CSDO</sub>      | Delay time: CS falling to data valid on SDO-x                         |                                                   |                         |     | 12                      | ns   |

| t <sub>DZ_CSDO</sub>       | Delay time: CS rising edge to SDO-x tristate                          |                                                   |                         |     | 12                      | ns   |

| t <sub>D_СКDO</sub>        | Delay time: SCLK launch<br>edge to next data valid on<br>SDO-x        | SPI-compatible protocols with single data rate    |                         |     | 15.8                    | ns   |

| t <sub>D_СКDO</sub>        | Delay time: SCLK launch<br>edge to next data valid on<br>SDO-x        | SPI-compatible protocols with double data rate    |                         |     | 21                      | ns   |

| t <sub>D_СКDO</sub>        | Delay time: SCLK launch<br>edge to next data valid on<br>SDO-x        | Parallel byte protocol                            |                         |     | 21                      | ns   |

|                            | Aperture delay                                                        |                                                   |                         | 8   |                         | ns   |

| t <sub>A</sub>             | t <sub>A</sub> mismatch                                               |                                                   |                         | 40  |                         | ps   |

| t <sub>JITTER</sub>        | Aperture jitter                                                       |                                                   |                         | 2   |                         | ps   |

| CLOCK RE-TIMER F           | PROTOCOL WITH STROBE = SC                                             | LK (EXTERNAL CLOCK) <sup>(1)</sup> (See           | 图 4)                    |     |                         |      |

| toff_strobe_do             | Time offset: STROBE edge to next data valid on SDO-x                  |                                                   | -2.5                    |     | 2.5                     | ns   |

| t <sub>D_CS_READY</sub>    | Delay time: CS rising to<br>READY displaying internal<br>device state |                                                   |                         |     | 13.5                    | ns   |

| t <sub>D_CKSTROBE_r</sub>  | Delay time: SCLK rising edge to STROBE rising                         |                                                   |                         |     | 21.5                    | ns   |

| tD_CKSTROBE_f              | Delay time: SCLK falling edge to STROBE falling                       |                                                   |                         |     | 21.5                    | ns   |

| t <sub>PH_STROBE</sub>     | Strobe output high time                                               |                                                   | 0.45 × t <sub>STR</sub> | (   | ).55 × t <sub>STR</sub> | ns   |

| t <sub>PL_STROBE</sub>     | Strobe output low time                                                |                                                   | 0.45 × t <sub>STR</sub> | (   | ).55 × t <sub>STR</sub> | ns   |

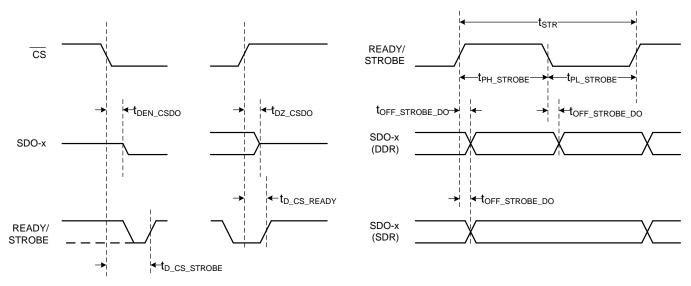

| CLOCK RE-TIMER F           | PROTOCOL WITH STROBE = INT                                            | ERNAL CLOCK <sup>(1)</sup> (See 图 5)              |                         |     |                         |      |

| t <sub>D_CS_STROBE</sub>   | Delay time : $\overline{CS}$ falling to 1 <sup>st</sup> STROBE rising |                                                   | 15                      |     | 50                      | ns   |

| <sup>t</sup> off_strobe_do | Time offset : STROBE<br>edge to next data valid on<br>SDO-x           |                                                   | -2.5                    |     | 2.5                     | ns   |

| t <sub>D_CS_READY</sub>    | Delay time: CS rising to<br>READY displaying internal<br>device state |                                                   |                         |     | 13.5                    | ns   |

| t <sub>INTCLK</sub>        | INTCLK period                                                         |                                                   |                         | 15  |                         | ns   |

|                            |                                                                       | INTCLK                                            |                         | 16  |                         | ns   |

| t <sub>STR</sub>           | STROBE period                                                         | INTCLK / 2                                        |                         | 30  |                         | ns   |

|                            |                                                                       | INTCLK / 4                                        |                         | 60  |                         | ns   |

| t <sub>WH_STR</sub>        | STROBE high period                                                    |                                                   | 0.45 × t <sub>STR</sub> | (   | ).55 × t <sub>STR</sub> | ns   |

| t <sub>WL_STR</sub>        | STROBE low period                                                     |                                                   | 0.45 × t <sub>STR</sub> |     | ).55 × t <sub>STR</sub> | ns   |

(1) Other parameters are the same as the SPI-compatible and Parallel Byte Protocols.

#### Switching Characteristics (continued)

at AVDD = 4.5 V to 5.5V, DVDD = 2.35 V to 5.5 V,  $V_{CM} = V_{REF/2}$ , Internal reference and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C, AVDD = 5V, DVDD = 3.3 V

|                                     | PARAMETER                                          | TEST CONDITIONS                | MIN | TYP  | MAX | UNIT |

|-------------------------------------|----------------------------------------------------|--------------------------------|-----|------|-----|------|

| ASYNCHRONOUS                        | ASYNCHRONOUS RESET AND POWER-DOWN TIMING (See 图 6) |                                |     |      |     |      |

| t <sub>RST-WKUP</sub>               | Wake up time from reset                            |                                |     |      | 1   | μs   |

| t <sub>PD-WKUP</sub> <sup>(2)</sup> | Wake up time from power-<br>down                   |                                |     | 18   | 150 | ms   |

| twkup-refout                        | REFOUT wake-up time                                |                                |     | 15.6 | 140 | ms   |

| t <sub>REFP_x-SETTLE</sub>          | Reference buffer output settling time              | $C_{\text{REFP}_x} = 10 \mu F$ |     | 18   | 150 | ms   |

#### (2) With $C_{REFP_x} = 10\mu F$

(1) The READY output is required for data transfer with zero cycle latency. The STROBE output is required only for clock re-timer (CRT) protocols.

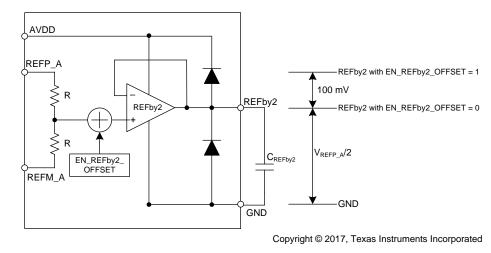

#### 图 1. Conversion Control and Data Transfer With Zero Cycle Latency (Zone 1 Transfer)

(1) The READY output is not required for zone 2 data transfer. The STROBE output is required only for clock re-timer protocols.

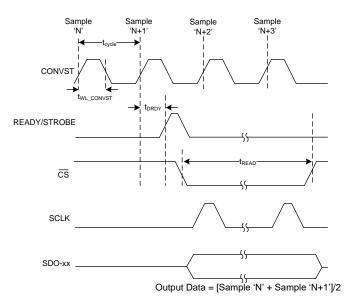

图 2. Conversion Control and Data Transfer With Wider Read Cycle (Zone 2 Transfer)

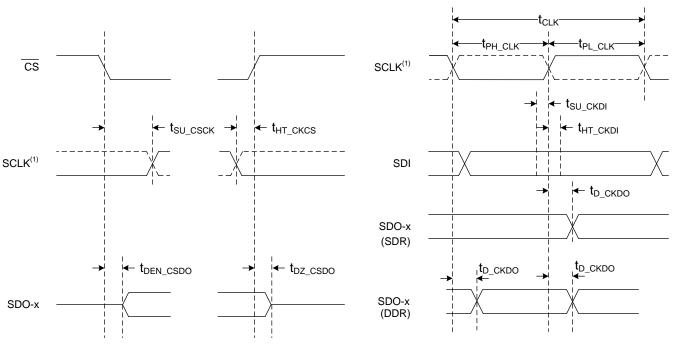

(1) The SCLK polarity, launch edge, and capture edge depend on the SPI protocol selected. DDR is not supported with the parallel byte protocol.

图 3. SPI-Compatible and Parallel Byte Protocols Timing

ADS9224R ADS9234R ZHCSIJ5C – AUGUST 2018– REVISED JUNE 2019

#### www.ti.com.cn

图 4. Clock Re-Timer Protocol (External Clock) Timing

图 6. Asynchronous Reset and Power-Down Timing

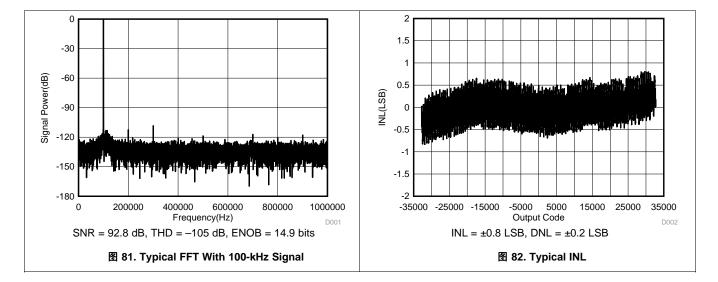

## 6.10 Typical Characteristics: ADS9224R

ADS9224R ADS9234R ZHCSIJ5C – AUGUST 2018 – REVISED JUNE 2019 TEXAS INSTRUMENTS

www.ti.com.cn

#### Typical Characteristics: ADS9224R (接下页)

# Typical Characteristics: ADS9224R (接下页)

TEXAS INSTRUMENTS

www.ti.com.cn

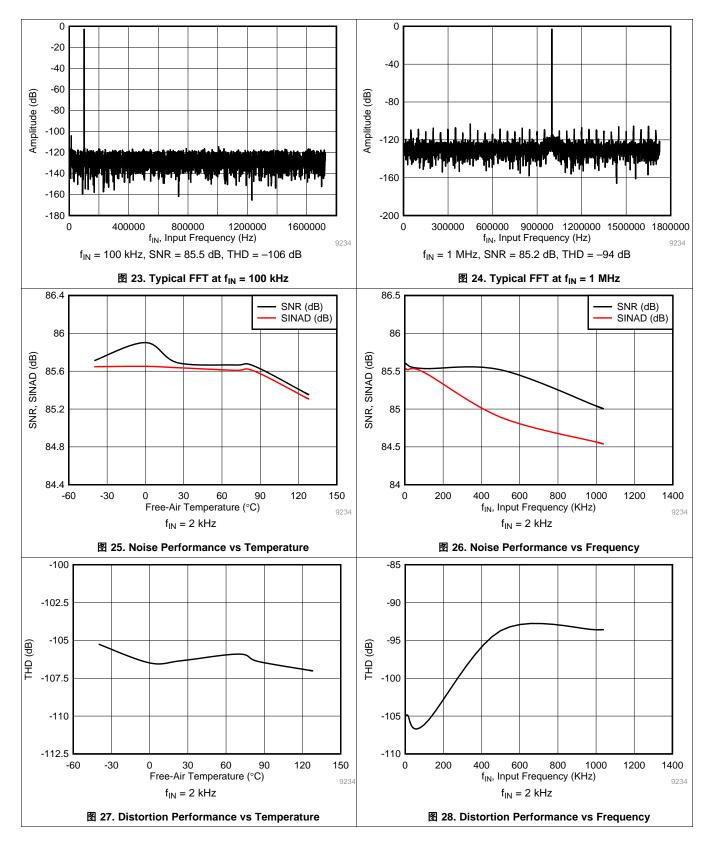

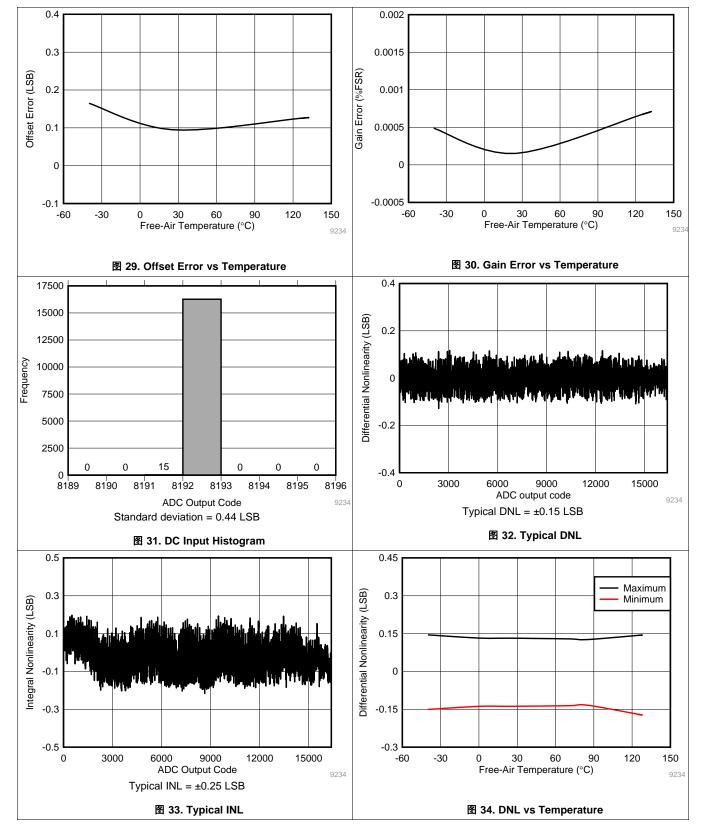

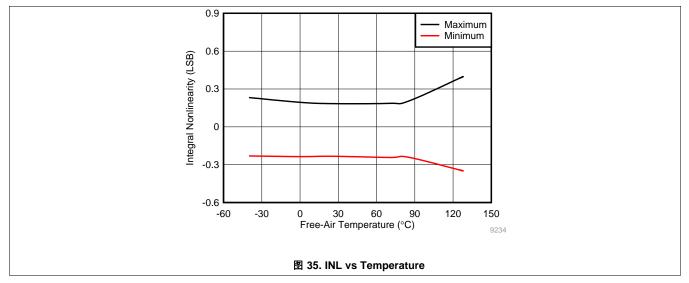

### 6.11 Typical Characteristics: ADS9234R

### Typical Characteristics: ADS9234R (接下页)

TEXAS INSTRUMENTS

www.ti.com.cn

# Typical Characteristics: ADS9234R (接下页)

# 7 Detailed Description

## 7.1 Overview

The device belongs to a family of dual, high-speed, simultaneous-sampling, analog-to-digital converters (ADCs). The device supports fully differential input signals and a full-scale input range equal to  $2 \times V_{\text{REFP x}}$ .

When a conversion is initiated, the difference voltage between the AINP\_x and AINM\_x pins is sampled on the internal capacitor array. The device uses an internal clock to perform conversions. During the conversion process, both analog inputs are disconnected from the sampling capacitors. At the end of conversion process, the device reconnects the sampling capacitors to the AINP\_x and AINM\_x pins and enters an acquisition phase. The device has internal reference and reference buffers to provide the charge required by the ADCs during conversion. The device includes a reference voltage for the ADCs.

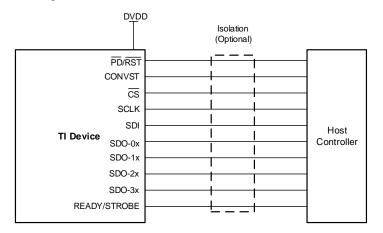

The enhanced serial programming interface (eSPI) digital interface is backward-compatible with traditional SPI protocols. eSPI configurable features simplify board layout, timing, and firmware and support high throughput at lower clock speeds, thus allowing an easy interface with a variety of microcontrollers, digital signal processors (DSPs), and field-programmable gate arrays (FPGAs). The device also provides a byte mode and a wide read cycle to reduce the clock frequency required for data transfer. The device includes a clock re-timer (CRT) to ensure data integrity when data are transferred through digital isolators. The device also supports double data rate (DDR) with SPI-compatible serial interface modes and with a clock re-timer.

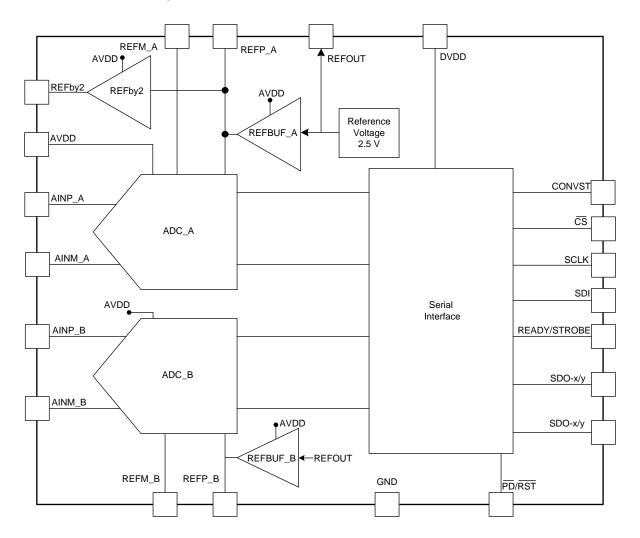

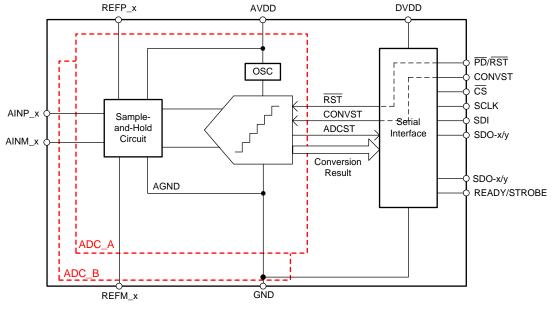

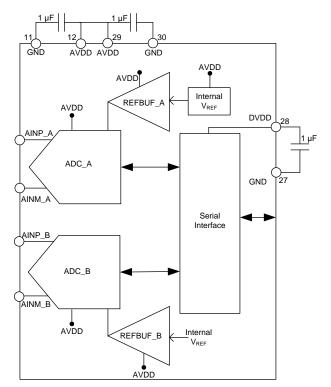

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

The device is comprised of seven modules: two converters (ADC\_A, ADC\_B), two reference buffers (REFBUF\_A, REFBUF\_B), the REFby2 buffer, the reference voltage, and the serial interface, as shown in the *Functional Block Diagram* section.

The converter module samples and converts the analog input into an equivalent digital output code. The reference buffers provide the charge required by the converters for the conversion process. The serial interface module facilitates communication and data transfer between the device and the host controller. The REFby2 buffer provides the common-mode voltage for the amplifiers input driving the analog of the device. The reference voltage is used by the converters for conversion process.

#### 7.3.1 Converter Modules

As shown in  $\mathbb{E}$  36, both converter modules sample the analog input signal, compare this signal with the reference voltage (between the pair of REFP\_x and REFM\_x pins), and generate an equivalent digital output code. The converter module receives the PD/RST and CONVST inputs from the interface module, and output the ADCST signal and the conversion result back to the interface module.

图 36. Converter Modules

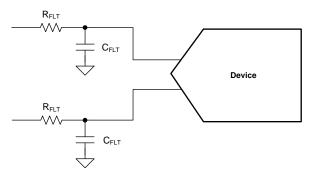

#### 7.3.1.1 Analog Input With Sample-and-Hold

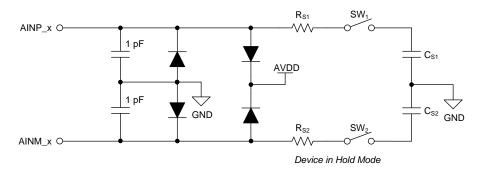

This device supports unipolar, fully differential, analog input signals.  $\mathbb{E}$  37 shows a small-signal equivalent circuit of the sample-and-hold circuit. Each sampling switch is represented by a resistance (R<sub>S1</sub> and R<sub>S2</sub>, typically 120  $\Omega$ ) in series with an ideal switch (SW<sub>1</sub> and SW<sub>2</sub>). The sampling capacitors, C<sub>S1</sub> and C<sub>S2</sub>, are typically 16 pF.

## Feature Description (接下页)

$V_{AINP x} - V_{AINM x}$ .

公式 1 and 公式 2 provide the full-scale input range (FSR) and common-mode voltage ( $V_{CM}$ ), supported at the analog inputs for reference voltage (V<sub>REFOUT</sub>) on the REFOUT pin.

$$FSR = \pm 1.6384 \times V_{REFOUT} = 3.2768 \times V_{REFOUT}$$

(1)

$V_{CM} = 0.8192 \times V_{REFOUT} \pm 0.2 V$

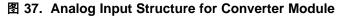

#### 7.3.1.2 ADC Transfer Function

The device output is in two's compliment format. 表 1 and 图 38 show the ideal transfer characteristics for the device.  $\Delta \pm 3$  gives the least significant bit (LSB) for the ADC.

$1 \text{ LSB} = \text{FSR} / 2^{\text{R}}$

where

- FSR is defined in 公式 1 ٠

- R = Resolution of the device

| STEP | INPUT VOLTAGE<br>(AINP_x-AINM_x)               | CODE | CODE DESCRIPTION IDEAL   |      | IDEAL OUTPUT CODE<br>(R = 14) |  |  |  |  |

|------|------------------------------------------------|------|--------------------------|------|-------------------------------|--|--|--|--|

| Α    | $\leq$ -(1.6384 × V <sub>REFOUT</sub> - 1 LSB) | NFSC | Negative full-scale code | 8000 | 2000                          |  |  |  |  |

| В    | 0 LSB to 1 LSB                                 | MC   | Mid code                 | 0000 | 0000                          |  |  |  |  |

| С    | ≥ (1.6384 × V <sub>REFOUT</sub> – 1 LSB)       | PFSC | Positive full-scale code | 7FFF | 1FFF                          |  |  |  |  |

#### 表 1. Transfer Characteristics

(2)

ADS9224R ADS92348

ZHCSIJ5C - AUGUST 2018-REVISED JUNE 2019

(3)

#### 7.3.2 Internal Reference Voltage

The device features an internal reference source with a nominal output value of 2.5 V. The ADC internal reference voltage is brought out on the REFOUT pin. A 1- $\mu$ F decoupling capacitor (C<sub>REFOUT</sub>), as shown in 🕅 39, is recommended to be placed between the REFOUT pin and GND pin. The capacitor must be placed as close to the REFOUT pin as possible. The output impedance of the internal band-gap circuit creates a low-pass filter with this capacitor to band-limit the noise of the reference. The initial accuracy specification for the internal reference can be degraded if the die is exposed to any mechanical or thermal stress. Heating the device when being soldered to a printed circuit board (PCB) and any subsequent solder reflow is a primary cause for shifts in the V<sub>REF</sub> value.

All performance characteristics of the device are specified with the internal reference buffer and a specified value of  $C_{REFP_x}$ . As shown in  $\[B]$  39, place a decoupling capacitor  $C_{REFP_x}$  between the REFP\_x and REFM\_x pins as close to the device as possible.

图 39. Connection Diagram for Reference and Reference Buffers

#### 7.3.3 Reference Buffers

On the CONVST rising edge, both converters start converting the sampled value on the analog input, and the internal capacitors are switched to the REFP\_x pins. Most of the switching charge required during the conversion process is provided by the external decoupling capacitor  $C_{REFP_x}$ . If the charge lost from  $C_{REFP_x}$  is not replenished before the next CONVST rising edge, the subsequent conversion occurs with this different reference voltage and causes a proportional error in the output code. To eliminate these errors, the internal reference buffers of the device maintains the voltage on the REFP\_x pins. The reference buffers have a gain of  $G_{REFBUF}$ , as specified in the *Specifications* section. The voltage at the REFP\_x pins can be calculated as  $V_{REFP_x} = G_{REFBUF} \times V_{REFOUT}$ .

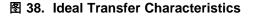

#### 7.3.4 REFby2 Buffer

The device includes a REFby2 buffer for setting the common-mode voltage required by the converter modules. The REFby2 output can be used to drive the  $V_{OCM}$  common-mode input pin of the fully differential amplifiers (similar to the THS4551). The REFby2 output can be increased by 100 mV (for specifications of the REFby2 output, see the *Specifications* section) for providing headroom from GND for the fully differential amplifier. To increase the REFby2 output, set the EN\_REFby2\_OFFSET bit to 1 in the REFby2\_OFFSET register. 40 depicts a block diagram for the REFby2 buffer.

#### 图 40. REFby2 Buffer

#### 7.3.5 Data Averaging

The device can be configured to average two or four samples and provide the averaged value as output data. To configure the data averaging, configure the DATA\_AVG\_CFG register.

#### 7.3.5.1 Averaging of Two Samples

To enable averaging of two samples, set the EN\_DATA\_AVG bits in the DATA\_AVG\_CFG register to 10b. In this mode, the device averages two samples and provides the average of two samples as output data. The output data rate reduces by a factor of two. In this mode, the host must provide two pulses separated by a time of  $t_{CYCLE}$  (see  $t_{CYCLE}$  for a zone 2 transfer in the *Specifications* section) on the CONVST pin. The device sets the READY pin high after a time of  $t_{DRDY}$  (see  $t_{DRDY}$  in the *Specifications* section) from the second rising edge on the CONVST pin. After the READY pin is set high, the host can read the data by using one of the protocols for reading from the device. The host can read the data while providing the two CONVST pulses for acquiring the next two samples. The host must keep  $t_{READ} < [2 \times t_{CYCLE}]$ . A provides the timing for the averaging of two samples.

#### 图 41. Timing for Averaging of Two Samples

ADS9224R ADS9234R ZHCSIJ5C – AUGUST 2018 – REVISED JUNE 2019 TEXAS INSTRUMENTS

www.ti.com.cn

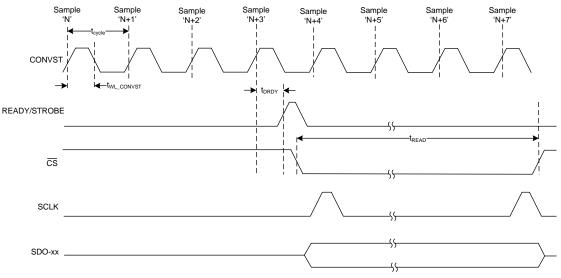

#### 7.3.5.2 Averaging of Four Samples

To enable averaging of four samples, set the EN\_DATA\_AVG bits in the DATA\_AVG\_CFG register to 11b. In this mode, the device averages four samples and provides the average of four samples as output data. The output data rate reduces by a factor of four. In this mode, the host must provide four pulses separated by a time of  $t_{CYCLE}$  (see  $t_{CYCLE}$  for a zone 2 transfer in the *Specifications* section) on the CONVST pin. The device sets the READY pin high after a time of  $t_{DRDY}$  (see  $t_{DRDY}$  in the *Specifications* section) from the fourth rising edge on the CONVST pin. After the READY pin is set high, the host can read the data by using one of the protocols for reading from the device. The host can read the data while providing the four CONVST pulses for acquiring the next four samples. The host must keep  $t_{READ} < [4 \times t_{CYCLE}]$ . A 2 provides the timing for the averaging of four samples.

Output Data = [Sample 'N' + Sample 'N+1' + Sample 'N+2' + Sample 'N+3']/4

图 42. Timing for Averaging of Four Samples

#### 7.4 Device Functional Modes

This device supports three functional states: <u>RST</u> or power-down, ACQ, and CNV. The device state is determined by the status of the CONVST and PD/RST control signals provided by the host controller.

#### 7.4.1 ACQ State

In ACQ state, the device acquires the analog input signal. The device enters ACQ state at power-up, when coming out of power down, after any asynchronous reset, and by the ADCST signal (internal). A PD/RST falling edge takes the device from ACQ state to RST state. A CONVST rising edge takes the device from ACQ state to CNV state.

#### 7.4.2 CNV State

The device moves from ACQ state to CNV state and starts conversion on a rising edge of a CONVST pin. The conversion process uses an internal clock. The host must provide a minimum time of  $t_{CYCLE}$  between two subsequent start of conversions.

#### 7.4.3 Reset or Power-Down

The PD/RST pin is an asynchronous digital input for the device. The pulse duration (low) on the PD/RST pin decides the state for the device (reset or power-down). 8 43 provides the timing diagram for these states. On power-up or after reset the device supports the SPI-00-S protocol for configuring the device and the SPI-00-S-SDR protocol for reading the data from the device. See the *Protocols for Reading From the Device* and *Protocols for Configuring the Device* sections for details.

## Device Functional Modes (接下页)

#### 7.4.3.1 Reset

To enter reset state, the host controller pulls and keeps the  $\overline{PD}/\overline{RST}$  pin low for a duration of  $t_{WL_RST}$  ( $t_{WL_RST-min} \le t_{WL_RST-max}$ ).

In reset state, the device terminates the ongoing conversion or acquisition process and all configuration registers (see the *Register Maps* section) are reset to their default values.

After a delay of  $t_{RST-WKUP}$ , the device enters ACQ state.

#### 7.4.3.2 Power-Down

To enter power-down state, the host controller pulls and keeps the  $\overline{PD}/\overline{RST}$  pin low for a minimum duration of  $t_{WLPD}$ .

In power-down state, all device blocks are powered down and all configuration registers (see the *Register Maps* section) are reset to their default values.

To exit power-down state, the host controller pulls the  $\overline{PD}/\overline{RST}$  pin high. After a delay of t<sub>PD-WKUP</sub>, the device powers up and enters ACQ state.

## Device Functional Modes (接下页)

#### 7.4.4 Conversion Control and Data Transfer Frame

The device supports two modes of conversion control and data transfer, one with zero cycle latency (zone 1 transfer) and another with a wide read cycle (zone 2 transfer).

#### 7.4.4.1 Conversion Control and Data Transfer Frame With Zero Cycle Latency (Zone 1 Transfer)

In this mode of conversion control and data transfer, the device starts conversion on the rising edge of CONVST. The CONVST pin can be pulled low after a minimum time of  $t_{WH_CONVST}$ . After the conversion is finished, the rising edge of the READY/STROBE pin indicates that the data are ready and the data can be read by the host. After the READY pin is set high, as shown in 8 44, the host must pull  $\fbox{CS}$  low and provide clocks on the SCLK pin to read the data in zone 1 without cycle latency. For a zone 1 transfer, the host must provide a minimum delay time of  $t_{D_cONVST_cS}$  (=  $t_{DRDY}$ ) between the rising edge of CONVST and the falling edge of  $\fbox{CS}$ .

The data for the present sample (sample N) is provided by the device on the SDO pins. After all bits are read, the host can pull the  $\overline{CS}$  pin high to end the data transfer frame. After pulling  $\overline{CS}$  high, the host can pull the CONVST pin high to start the next conversion. The host must keep the SDI pin low (NOP0) or high (NOP1) for conversion control and for getting conversion results from the device. In this mode of conversion control, the time between two adjacent rising edges of the CONVST signal ( $t_{CYCLE}$ ) is determined as  $t_{CYCLE} = t_{DRDY} + t_{READ}$ .

- (1) The READY output is required for data transfer with zero cycle latency. The STROBE output is required only for clock re-timer (CRT) protocols. See the *READY/STROBE Output* section for details.

- (2) For t<sub>READ</sub> with different data transfer protocols; see the *Protocols for Reading From the Device* section.

- (3)  $f_{\text{Sample}} = 1 / t_{\text{cycle}}$ .

- 图 44. Conversion Control and Data Transfer Frame With Zero Cycle Latency (Zone 1 Transfer)

#### Device Functional Modes (接下页)

#### 7.4.4.2 Conversion Control and Data Transfer Frame With Wide Read Cycle (Zone 2 Transfer)

In this mode of conversion control and data transfer, the device starts conversion on the rising edge of CONVST. The CONVST pin can be pulled low after a minimum time of  $t_{WH_CONVST}$ . Afte<u>r</u> a time of  $t_{D_CONVST_CS}$  (see  $t_{D_CONVST_CS}$  for zone 2 transfer in the *Specifications* section), the host must pull CS low and provide clocks on the SCLK pin to read the data in zone 2. As shown in A 45, a zone 2 transfer provides more read time ( $t_{read}$ ). The read time available for reading data is maximized when  $t_{D_CONVST_CS}$  is set to the minimum permissible value. The data for the previous sample (sample N-1) is provided by the device on the SDO pins. After all bits are read, the host can pull the CS pin high to end the data transfer frame. After pulling CS high, the host can pull the CONVST pin high to start the next conversion. In this mode of conversion control, a minimum time of  $t_{CYCLE}$  (see  $t_{CYCLE}$  for zone 2 transfer in the *Specifications* section) is required between two adjacent rising edges of the CONVST signal. The host must keep the SDI pin low (NOP0) or high (NOP1) for conversion control and for getting conversion results from the device.

- (1) The READY output is not required for zone 2 data transfer. The STROBE output is required only for clock re-timer (CRT) protocols. See the *READY/STROBE Output* section for details.

- (2) For t<sub>READ</sub> with different data transfer protocols; see the *Protocols for Reading From the Device* section.

- (3)  $f_{\text{Sample}} = 1 / t_{\text{cycle}}$ .

#### 图 45. Conversion Control and Data Transfer Frame With Wide Read Cycle (Zone 2 Transfer)

#### 注

For optimum performance with zone 2 transfer, TI recommends masking the READY output by setting the READY\_MASK bit in the OUTPUT\_DATA\_WORD\_CFG register and using a data transfer protocol with a bus width of more than 2 SDOs or the parallel byte protocol to keep [ $t_{D_{CONVST_CS}} + t_{READ}$ ] below 150 ns. See the *Protocols for Reading From the Device* section for details on different protocols for reading the data.

## 7.5 READY/STROBE Output

The READY/STROBE pin has multiple functions. The READY and STROBE signals are multiplexed to this pin. When CS is low, STROBE is output and when CS is high, READY is output.

#### 7.5.1 READY Output

After power-up or after exiting power-down (a rising edge on  $\overline{PD/RST}$ ), the READY signal is set high. After a time of 0.9 ms, this signal goes low, indicating that the device is initialized and the registers can be configured. However, conversions can be performed with the desired accuracy only after a time of  $t_{PD-WKUP}$  (see the *Specifications* section). After power-up, for a zone 1 transfer (see  $\mathbb{R}$  44), the device starts conversion on the CONVST rising edge and the READY pin remains low during the conversion process. After a time of  $t_{DRDY}$ , the conversion process completes, READY is set high, and data can be read by the host. The host can read data by bringing  $\overline{CS}$  high and by providing clocks on SCLK. After  $\overline{CS}$  is brought low, READY is set low. For a zone 2 transfer, TI recommends masking the READY output by setting the READY\_MASK bit in the OUTPUT\_DATA\_WORD\_CFG register.

#### 7.5.2 STROBE Output

In clock re-timer protocols, the device sends out data on the SDO lines with synchronized clock on the STROBE line. The data are synchronized to the rising edge of the STROBE pulses. In CRT protocols, the host can use the STROBE output for latching the data. The STROBE for the CRT protocols is either derived from the external SCLK provided by the host or from the internal oscillator. The STROBE signal is held low for protocols other than the CRT protocols.

#### 7.6 Programming

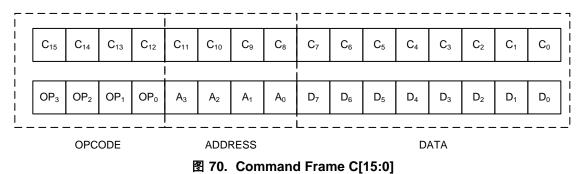

#### 7.6.1 Output Data Word

The output data word, as shown in  $\frac{1}{8}$  2, consists of a conversion result of N bits, where N is the width of the output data word. The output data word is provided on data lines (SDO-xx) for each ADC.

| DEVICE   | RESOLUTION<br>OF DEVICE (R) | WIDTH OF<br>OUTPUT DATA<br>WORD (N) | CONTENT OF OUTPUT<br>DATA WORD <sup>(1)(2)</sup> | MSB OF CONVERSION<br>RESULT WITH LEFT<br>ALIGNMENT | MSB OF CONVERSION<br>RESULT WITH RIGHT<br>ALIGNMENT |

|----------|-----------------------------|-------------------------------------|--------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|

| ADS9224R | 16                          | 16                                  | 16-bit conversion in 2's<br>compliment format    | D <sub>N-1</sub> (= D <sub>15</sub> )              | D <sub>N-1</sub> (= D <sub>15</sub> )               |

| ADS9234R | 14                          | 16                                  | 14-bit conversion in 2's<br>compliment format    | D <sub>N-1</sub> (= D <sub>13</sub> )              | D <sub>N-3</sub> (= D <sub>13</sub> )               |

#### 表 2. Output Data Word

(1) The device provides register data in the output data word during register read operation.

(2) When a fixed pattern data is enabled, the device provides a fixed pattern in the output data word.

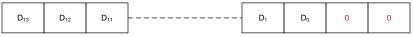

For ADS9234R devices with 14-bit resolution, the output data word can be left-aligned or right-aligned by configuring the DATA\_RIGHT\_ALIGNED bit. With left alignment, the device appends zeros in the end of the output data word. With right alignment, the device appends MSBs in the beginning of the output data word. 🛛 46 shows the data alignment in the data output word.

Left Aligned Data with Zeros appended at the end

| D <sub>13</sub> | D <sub>13</sub> | D <sub>13</sub> | D <sub>12</sub> |  | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |  |

|-----------------|-----------------|-----------------|-----------------|--|----------------|----------------|----------------|--|

|-----------------|-----------------|-----------------|-----------------|--|----------------|----------------|----------------|--|

Right Aligned Data with MSBs appended in the beginning (Sign Extension)

#### 图 46. Data Alignment for ADS9234R Devices

#### 7.6.2 Data Transfer Protocols

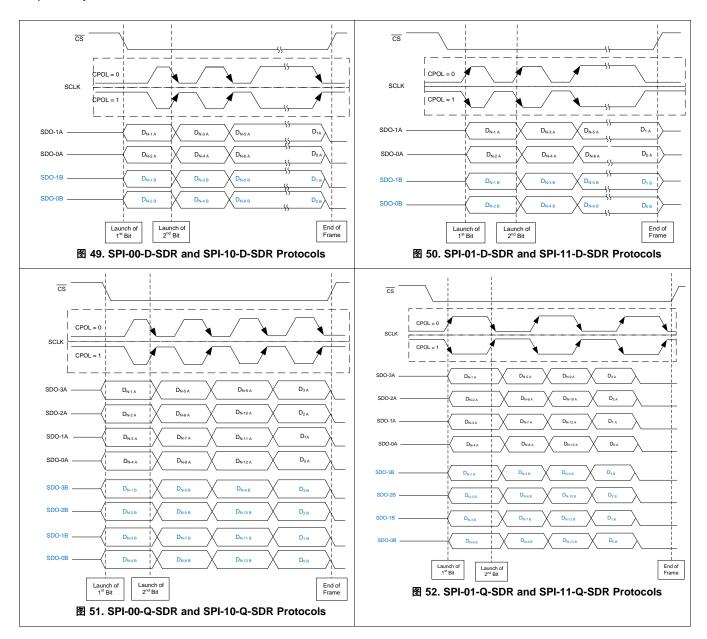

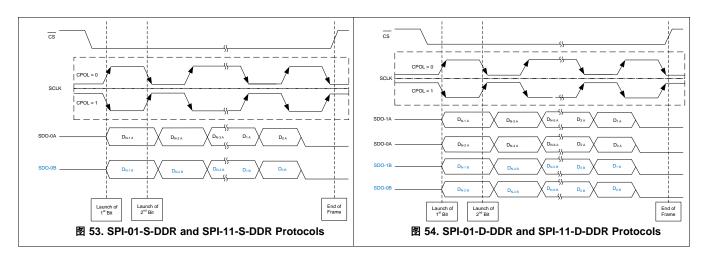

This device features an enhanced-SPI digital interface that allows the host controller to operate at slower SCLK speeds and still achieve the required throughput and response time. The enhanced-SPI digital interface module offers three options to reduce the SCLK speed required for data transfer:

- Increase the width of the output data bus (dual SDO, quad SDO, or parallel byte)

- Enable double data rate (DDR) transfer

- Wider read cycle by extending the data transfer window (zone 2 transfer)

These three options can be combined to achieve further reduction in SCLK speed.

#### 7.6.2.1 Protocols for Reading From the Device

The protocols for the data-read operation can be broadly classified into five categories:

- 1. Legacy, SPI-compatible protocols (SPI-xy-S-SDR)

- 2. SPI-compatible protocols with bus width options and single data rate (SPI-xy-D-SDR and SPI-xy-Q-SDR)

- 3. SPI-compatible protocols with bus width options and double data rate (SPI-x1-S-DDR, SPI-x1-D-DDR, and SPI-x1-Q-DDR)

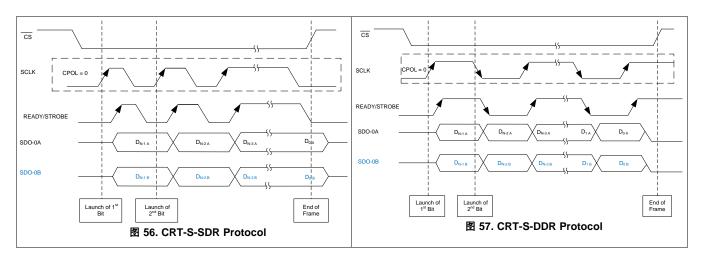

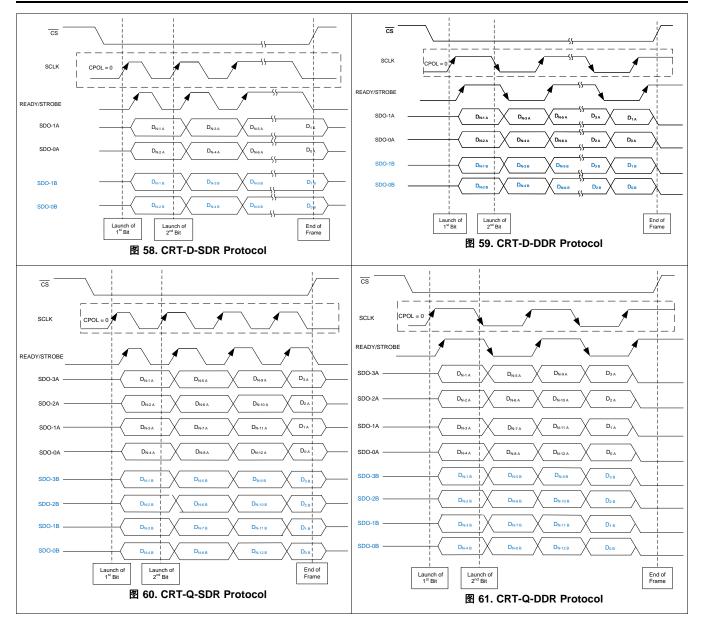

- 4. Clock re-timer (CRT) protocols (CRT-S-SDR, CRT-D-SDR, CRT-Q-SDR, CRT-S-DDR, CRT-D-DDR, and CRT-Q-DDR)

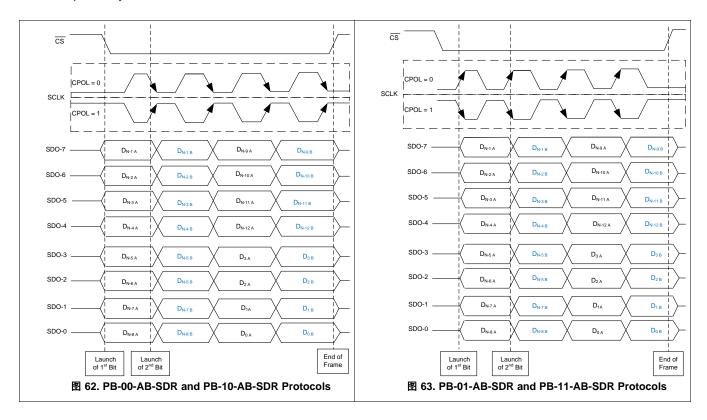

- 5. Parallel byte protocol (PB-xy-AB-SDR, PB-xy-AA-SDR)

#### 7.6.2.1.1 Legacy, SPI-Compatible Protocols (SPI-xy-S-SDR)

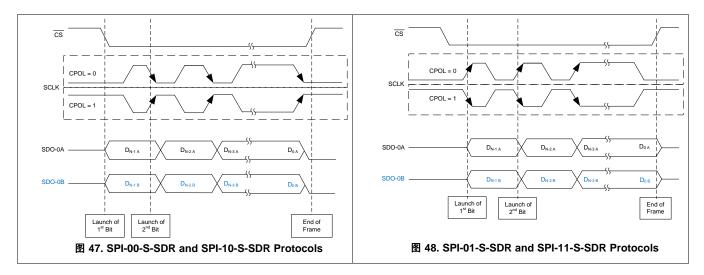

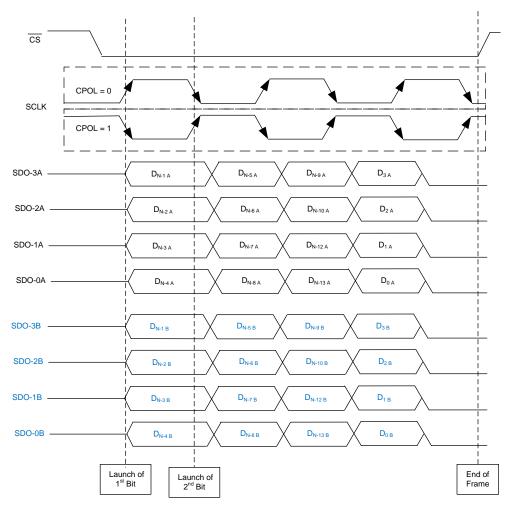

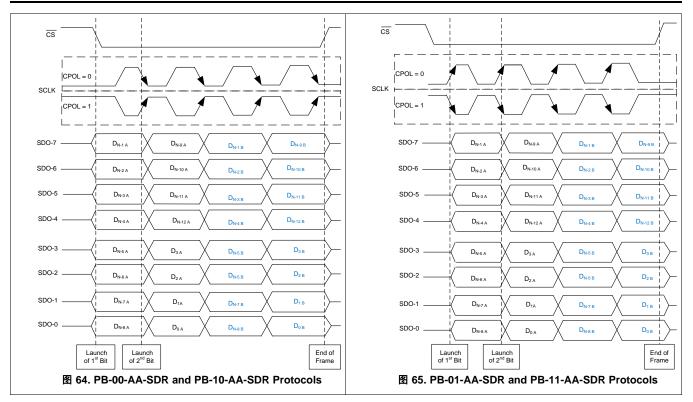

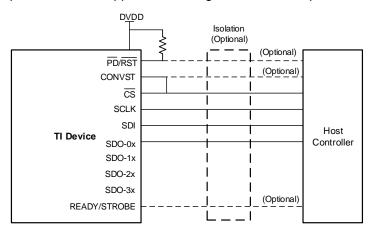

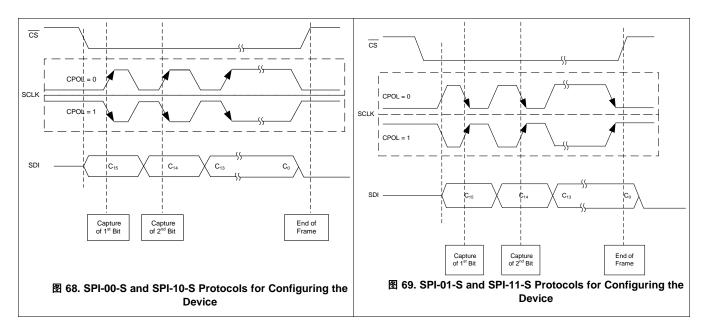

The device supports legacy, SPI-compatible protocols with all combinations of clock phase and polarity. In this data transfer protocol, the device provides data from ADC\_A on SDO-0A and data from ADC\_B on SDO-0B. On power-up or after reset, the device supports the SPI-00-S-SDR protocol for reading data from the device. 表 3 provides the details of different legacy SPI protocols to read data from the device.