ZHCSDT7E -APRIL 2015-REVISED SEPTEMBER 2017

**AFE5816**

# 具有 90mW/通道功耗、1-nV/√Hz 噪声、14 位 65MSPS 或 12 位 80MSPS ADC 以及 CW 无源混频器的 AFE5816 16 通道超声波 AFE

#### 1 特性

- 面向超声波应用的 16 通道 应用应用的 32 通道 AFE:

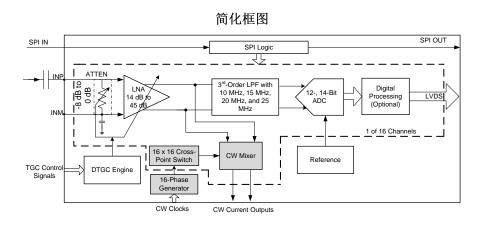

- 输入衰减器、低噪声放大器 (LNA)、低通滤波器 (LPF)、模数转换器 (ADC) 和 连续波 (CW) 混频器

- 信号链针对时间增益补偿 (TGC) 和 CW 模式进 行了优化

- 数字时间增益补偿 (DTGC)

- 总增益范围: 6dB 至 45dB

- 线性输入范围: 1 V<sub>PP</sub>

- 具有 DTGC 功能的输入衰减器:

- 衰减范围为 0dB 至 8dB (步长为 0.125dB)

- 支持匹配的阻抗:

- 50Ω 至 800Ω 的源阻抗

- 具有 DTGC 功能的低噪声放大器 (LNA):

- 增益范围为 14dB 至 45dB (步长为 0.125dB)

- 低输入电流噪声: 1.2pA/√Hz

- 三阶线性相位低通滤波器 (LPF):

- 10MHz、15MHz、20MHz 和 25MHz

- 具有可编程分辨率的模数转换器 (ADC):

- 14 位 ADC: 65MSPS 时的空闲通道信噪比 (SNR) 为 75dBFS

- 12 位 ADC: 80MSPS 时 的空闲通道 SNR 为 72dBFS

- LVDS 接口,速率最高达 1GBPS

- 针对噪声和功耗进行了优化:

- 90mW/通道,1nV/√Hz(65MSPS,TGC 模式)

- 55mW/通道,1.45nV/√Hz(40MSPS, TGC 模式)

- 59mW/通道(CW 模式)

- 出色的器件间增益匹配:

- ±0.5dB (典型值)

- 低谐波失真等级: -60dBc

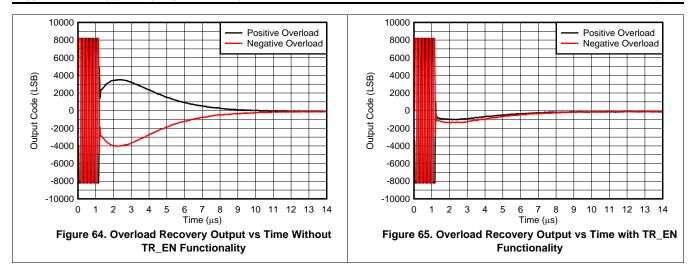

- 快速且持续的过载恢复

- 连续波 (CW) 路径:

- 无源混频器

- 低近端相位噪声:1KHz 时为 -148dBc/Hz

- 相位分辨率: λ/16

- 支持 16X、8X、4X 和 1X CW 时钟

- 三阶和五阶谐波 12dB 抑制

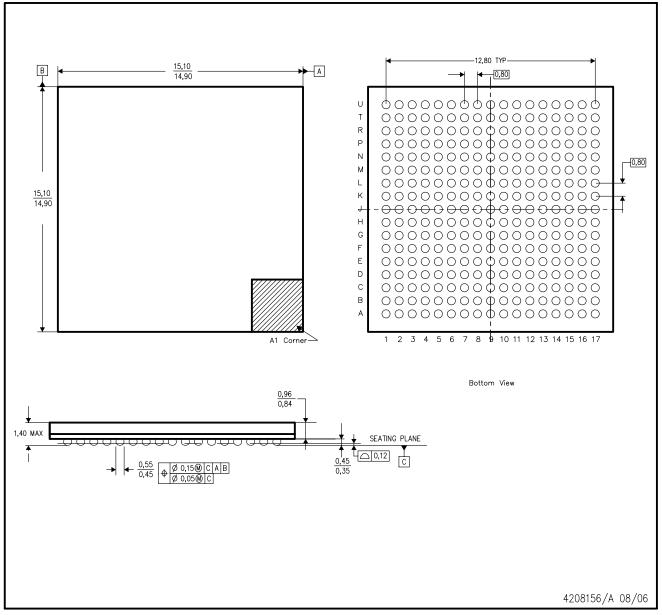

- 小型封装: 15mm x 15mm NFBGA-289

#### 2 应用

- 医疗超声波成像

- 无损检测设备

- 声纳成像设备

- 多通道高速数据采集

#### 3 说明

AFE5816 是一套高度集成的模拟前端 (AFE) 解决方案,专用于需要高性能、低功耗和小尺寸的超声波系统。

#### 器件信息(1)

| 器件型号    | 封装          | 封装尺寸 (标称值)        |

|---------|-------------|-------------------|

| AFE5816 | nFBGA (289) | 15.00mm × 15.00mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的封装选项附录。

| 710 |

|-----|

| 7   |

| 1 | 特性1                                      |    | 9.3 Feature Description                  | 31              |

|---|------------------------------------------|----|------------------------------------------|-----------------|

| 2 | 应用 1                                     |    | 9.4 Device Functional Modes              | 74              |

| 3 | 说明1                                      |    | 9.5 Programming                          | 79              |

| 4 | 修订历史记录 3                                 | 10 | Application and Implementation           | 81              |

| 5 | 说明(续)4                                   |    | 10.1 Application Information             | <mark>81</mark> |

| 6 | Device Family Comparison Table 6         |    | 10.2 Typical Application                 | 81              |

| 7 | Pin Configuration and Functions          |    | 10.3 Do's and Don'ts                     |                 |

| 8 | Specifications                           |    | 10.4 Initialization Set Up               |                 |

| U | 8.1 Absolute Maximum Ratings             | 11 | Power Supply Recommendations             | 86              |

|   | 8.2 ESD Ratings                          |    | 11.1 Power Sequencing and Initialization | 86              |

|   | 8.3 Recommended Operating Conditions     | 12 | Layout                                   | 87              |

|   | 8.4 Thermal Information                  |    | 12.1 Layout Guidelines                   | 87              |

|   | 8.5 Electrical Characteristics: TGC Mode |    | 12.2 Layout Example                      | 88              |

|   | 8.6 Electrical Characteristics: CW Mode  | 13 | Register Maps                            | 95              |

|   | 8.7 Digital Characteristics              |    | 13.1 Serial Register Map                 | 95              |

|   | 8.8 Output Interface Timing Requirements | 14 | 器件和文档支持                                  | 159             |

|   | 8.9 Serial Interface Timing Requirements |    | 14.1 文档支持                                | 159             |

|   | 8.10 Typical Characteristics: TGC Mode   |    | 14.2 社区资源                                | 159             |

|   | 8.11 Typical Characteristics: CW Mode    |    | 14.3 商标                                  | 159             |

| 9 | Detailed Description                     |    | 14.4 静电放电警告                              | 159             |

|   | 9.1 Overview                             |    | 14.5 Glossary                            |                 |

|   | 9.2 Functional Block Diagram30           | 15 | 机械、封装和可订购信息                              | 159             |

### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

## Changes from Revision D (November 2015) to Revision E Page Added Latency Between a Transition in TGC SLOPE and the Resulting Change in Gain table and associated Changed HPF\_ROUND\_ENABLE register bit (register 21, bit 5) to HPF\_ROUND\_EN\_CH1-8 and HPF\_ROUND\_EN\_CH9-16 bits in last paragraph of Digital HPF section .......70

|  | 修订历史记录( | (接下页) |

|--|---------|-------|

|--|---------|-------|

| Cł       | anges from Revision A (April 2015) to Revision B                                                                                 | Page       |

|----------|----------------------------------------------------------------------------------------------------------------------------------|------------|

| <u> </u> | Changed Functional Block Diagram: removed references to AFE58JD16                                                                | 30         |

| •        | 从文档中删除了 AFE58JD16                                                                                                                |            |

| Cł       | nanges from Revision B (June 2015) to Revision C                                                                                 | Page       |

| •        | 添加了社区资源部分                                                                                                                        | 159        |

| •        | 已更改说明部分                                                                                                                          |            |

| •        | 已更改器件信息表和简化框图                                                                                                                    |            |

| •        | 已更改特性部分:已在第一个特性要点中添加第二个分项,已更改 $ADC$ 和针对噪声和功率进行了优化特性要点,并已添加第一个分项和最后一个分项至 $CW$ 特性要点部分)                                             |            |

| •        | 将完整文档发布至 Web:添加了器件比较表、引脚配置和功能部分、规范部分、详细说明部分、应用和实施部分、电源相关建议部分、布局部分以及寄存器映射部分                                                       | 1          |

| Cł       | nanges from Revision C (August 2015) to Revision D                                                                               | Page       |

| •        | 已删除 从相关文档 部分删除了 WEBENCH                                                                                                          | 159        |

| •        | Deleted register 202 from VCA Register Map table                                                                                 | 135        |

| •        | Added register descriptions for registers 65 and 66                                                                              | 133        |

| •        | Changed bits 7-5 from PIN_PAT_LVDS to PAT_LVDS15[2:0] in register 59                                                             |            |

| •        | Changed bit 5 from 0 to HPF_ROUND_EN_CH9-16 in register 45                                                                       |            |

| •        | . Changed HPF_ROUND_EN to HPF_ROUND_EN_CH1-8 in register 21                                                                      |            |

| •        | Changed 001 row description from half frame 0, half frame 1 to half frame 1, half frame 0 in Pattern Mode Bit  Description table | 100        |

| •        | Added registers 65 and 66 to ADC Register Map table                                                                              | 98         |

| •        | Changed PIN_PAT_LVDS to PAT_LVDS15[2:0] in register 59 of ADC Register Map table                                                 | 98         |

| •        | 已添加 <i>PLL Initialization</i> section                                                                                            |            |

| •        | 已添加 PLL initialization method (step 4) to <i>Initialization Set Up</i> section                                                   |            |

| •        | 已添加 last paragraph to Partial Power-Up and Power-Down Mode section                                                               | <b>7</b> 7 |

#### 5 说明 (续)

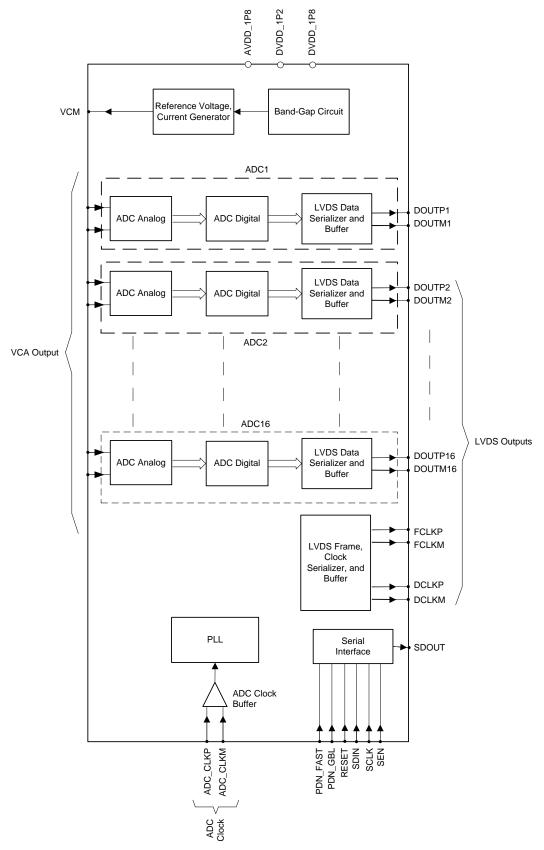

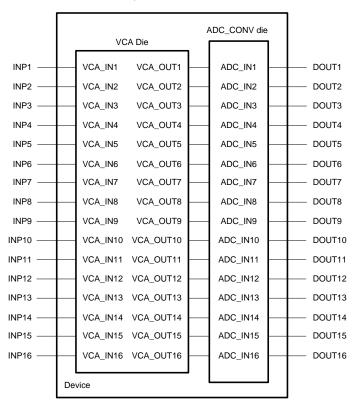

AFE5816 是一款集成模拟前端 (AFE),针对医疗超声波应用进行了优化。AFE5816 是一款多芯片模块 (MCM)器件,包含两个芯片: VCA 和 ADC\_CONV。每个芯片均有 16 条通道。

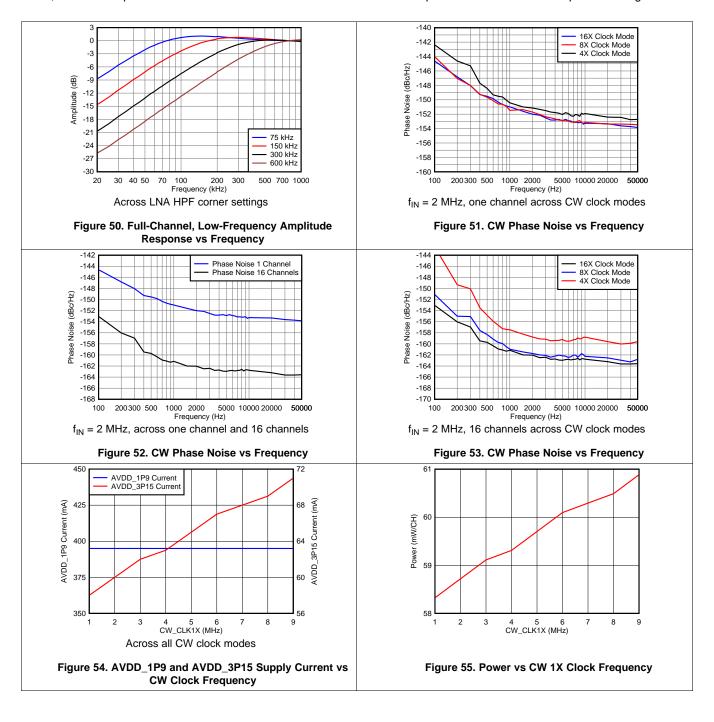

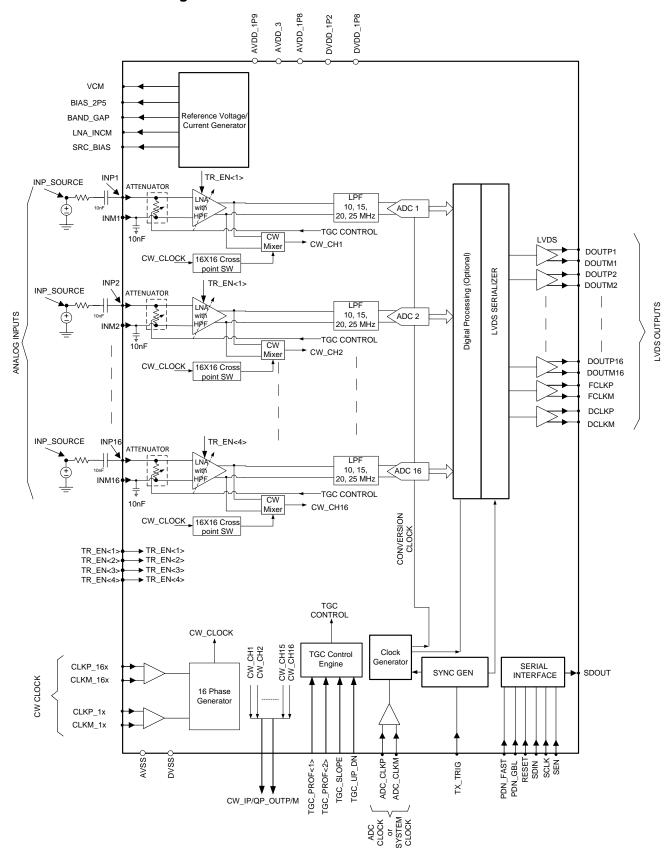

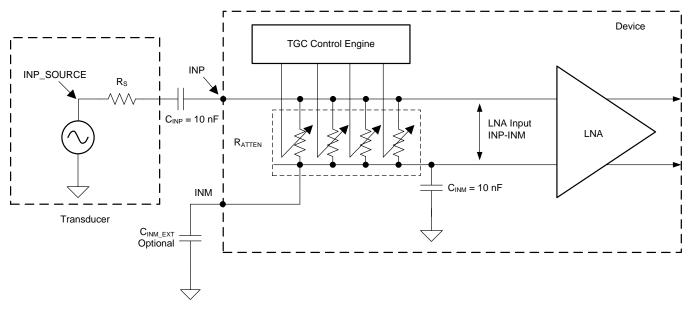

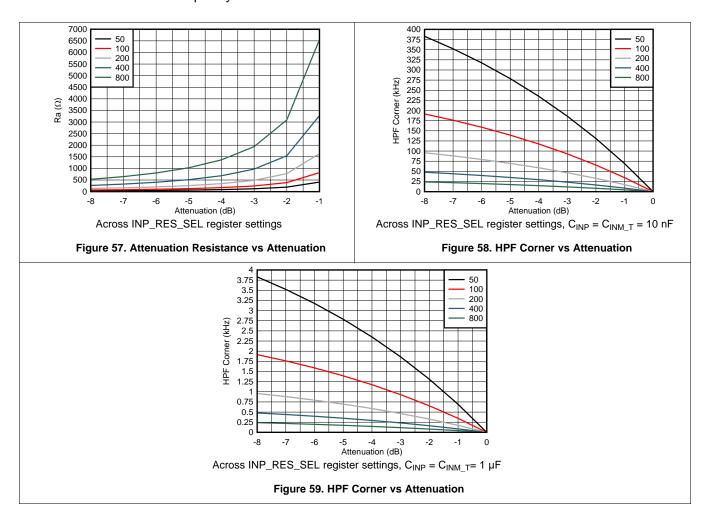

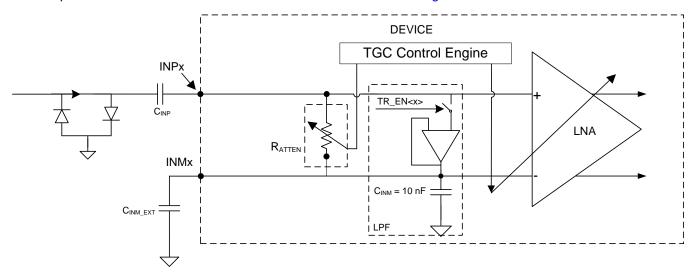

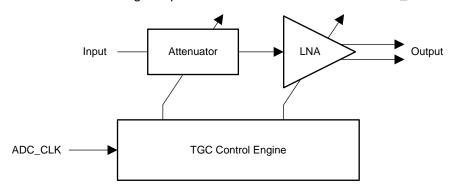

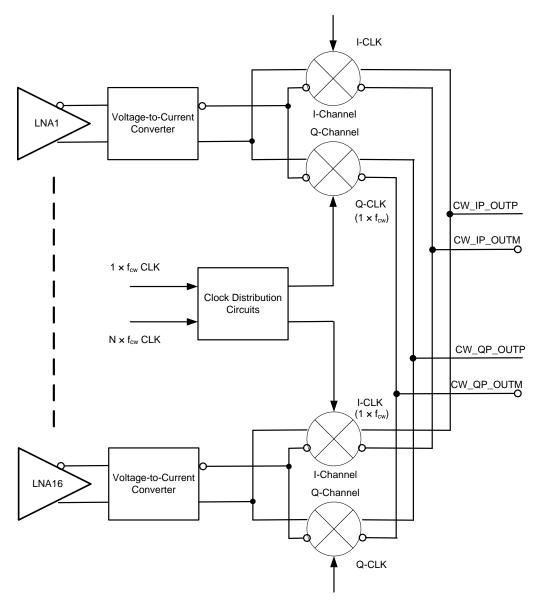

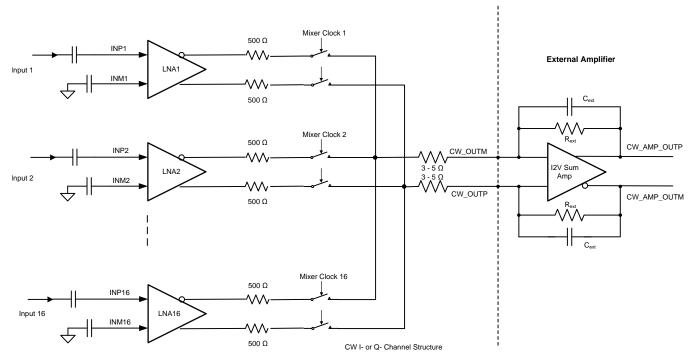

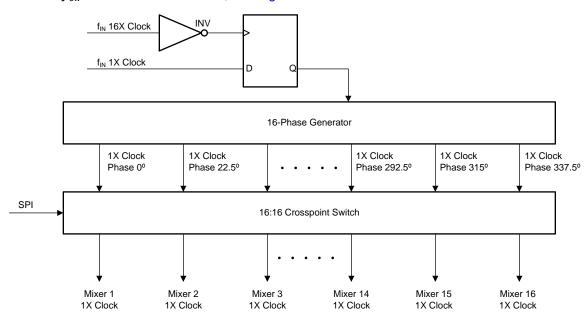

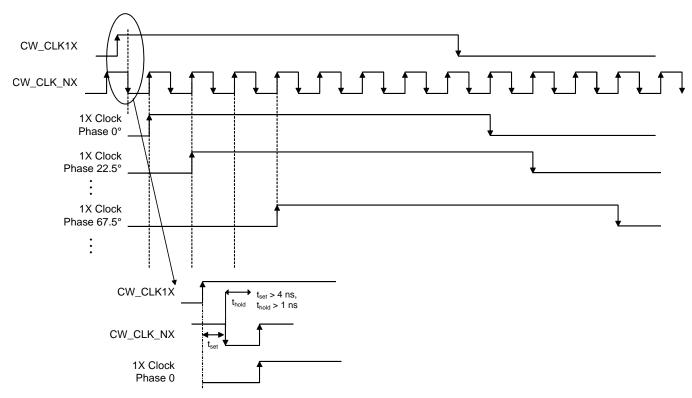

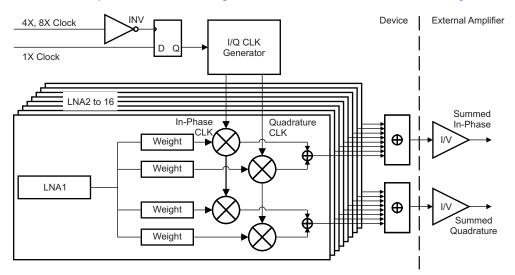

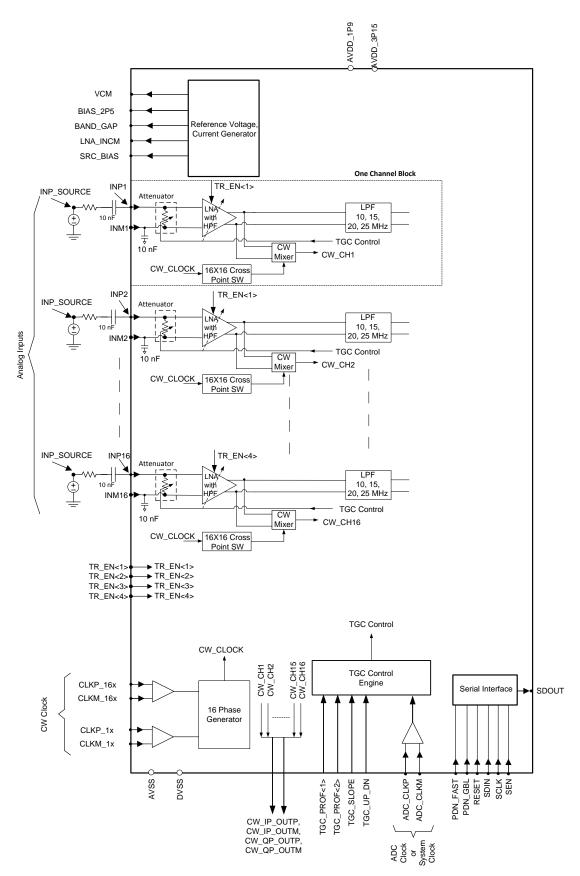

VCA 芯片中的每条通道均可配置为两种模式:时间增益补偿 (TGC)模式和连续波 (CW)模式。在 TGC 模式下,每条通道包含一个输入衰减器 (ATTEN)、一个带有可变增益的低噪声放大器 (LNA)以及一个三阶低通滤波器 (LPF)。衰减器支持的衰减范围为 0dB 至 8dB,LNA 支持的增益范围为 14dB 至 45dB。LPF 的截止频率可配置为 10MHz、15MHz、20MHz 或 25 MHz,以便支持频率不同的超声波应用。在 CW 模式下,每条通道包含一个增益固定为 18dB 的 LNA 以及一个具有 16 种可选相位延迟的低功耗无源混频器。通过对每个模拟输入信号施加不同的相位延迟可执行片上波束赋形操作。CW 混频器中的谐波滤波器通过抑制三阶和五阶谐波来增强 CW 多普勒测量的灵敏度。CW 模式支持三种时钟模式: 16 倍频、8 倍频和 4 倍频。

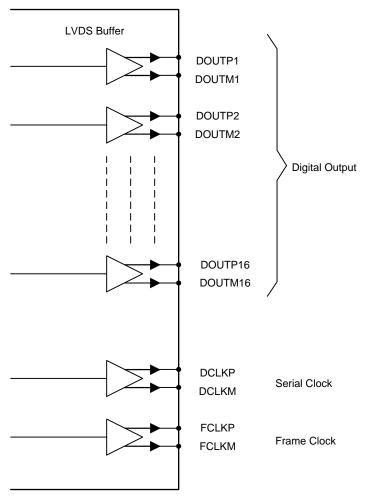

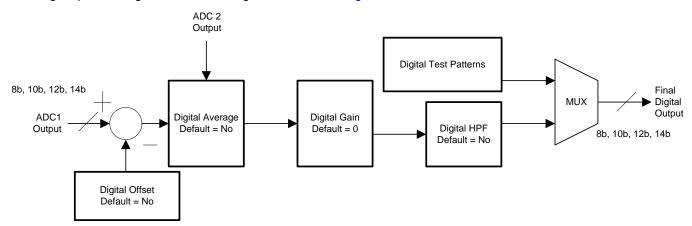

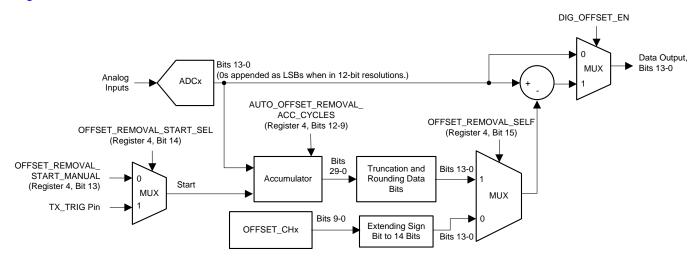

ADC\_CONV 芯片的每条通道都具有一个高性能模数转换器 (ADC),该转换器的分辨率可编程为 14 位或 12 位。 ADC 在 14 位 和 12 位模式下分别可实现 75dBFS 和 72dBFS 的信噪比 (SNR)。该 ADC 在低通道增益时仍具有出色的 SNR。该器件的最高运行速度为 65MSPS 和 80MSPS,分别提供 14 位和 12 位输出。ADC 设计为根据采样率调整其功耗。ADC 的输出接口为低压差分信令 (LVDS) 接口,可轻松与低成本现场可编程门阵列 (FPGA) 连接。

AFE5816 还允许选择多种功率和噪声组合,从而优化系统性能。因此,对于电池寿命要求严格的系统而言,这些器件是一套非常适合的超声波 AFE 解决方案。AFE5816 采用 15mm × 15mm NFBGA-289 封装(ZAV 封装,S-PBGA-N289),额定工作温度范围为 −40°C 至 +85°C。此器件还与 AFE5818 系列器件引脚兼容。的最后一段

# 6 Device Family Comparison Table

| DEVICE   | DESCRIPTION                                                                                                                                                     | PACKAGE     | BODY SIZE (NOM)     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|

| AFE5818  | 16-channel, ultrasound, analog front-end (AFE) with 124-mW/channel, 0.75-nV/ $\sqrt{\rm Hz}$ noise, 14-bit, 65-MSPS or 12-bit, 80-MSPS ADC and passive CW mixer | NFBGA (289) | 15.00 mm × 15.00 mm |

| AFE5812  | Fully integrated, 8-channel ultrasound AFE with passive CW mixer, and digital I/Q demodulator, 0.75 nV/ $\sqrt{\rm Hz}$ , 14 and 12 bits, 65 MSPS, 180 mW/ch    | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5809  | 8-channel ultrasound AFE with passive CW mixer, and digital I/Q demodulator, 0.75 nV/ $\sqrt{\rm Hz}$ , 14 and 12 bits, 65 MSPS, 158 mW/ch                      | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5808A | 8-channel ultrasound AFE with passive CW mixer, 0.75 nV/ $\sqrt{\text{Hz}}$ , 14 and 12 bits, 65 MSPS, 158 mW/ch                                                | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5807  | 8-channel ultrasound AFE with passive CW mixer, 1.05 nV/ $\sqrt{\rm Hz}$ , 12 bits, 80 MSPS, 117 mW/ch                                                          | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5803  | 8-channel ultrasound AFE, 0.75 nV/\(\sqrt{Hz}\), 14 and 12 bits, 65 MSPS, 158 mW/ch                                                                             | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5805  | 8-channel ultrasound AFE, 0.85 nV/\Hz, 12 bits, 50 MSPS, 122 mW/ch                                                                                              | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5804  | 8-channel ultrasound AFE, 1.23 nV/\(\sqrt{Hz}\), 12 bits, 50 MSPS, 101 mW/ch                                                                                    | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5801  | 8-channel variable-gain amplifier (VGA) with octal high-speed ADC, 5.5 nV/ $\sqrt{\text{Hz}}$ , 12 bits, 65 MSPS, 65 mW/ch                                      | VQFN (64)   | 9.00 mm × 9.00 mm   |

| AFE5851  | 16-channel VGA with high-speed ADC, 5.5 nV/√Hz, 12 bits, 32.5 MSPS, 39 mW/ch                                                                                    | VQFN (64)   | 9.00 mm × 9.00 mm   |

| VCA5807  | 8-channel voltage-controlled amplifier for ultrasound with passive CW mixer, 0.75 nV/ $\sqrt{\text{Hz}}$ , 99 mW/ch                                             | HTQFP (80)  | 14.00 mm × 14.00 mm |

| VCA8500  | 8-channel, ultralow-power VGA with low-noise pre-amp, 0.8 nV/\(\overline{Hz}\), 65 mW/ch                                                                        | VQFN (64)   | 9.00 mm × 9.00 mm   |

| ADS5294  | Octal-channel, 14-bit, 80-MSPS ADC, 75-dBFS SNR, 77 mW/ch                                                                                                       | HTQFP (80)  | 14.00 mm × 14.00 mm |

| ADS5292  | Octal-channel, 12-bit, 80-MSPS ADC, 70-dBFS SNR, 66 mW/ch                                                                                                       | HTQFP (80)  | 14.00 mm × 14.00 mm |

| ADS5295  | Octal-channel, 12-bit, 100-MSPS ADC, 70.6-dBFS SNR, 80 mW/ch                                                                                                    | HTQFP (80)  | 14.00 mm × 14.00 mm |

| ADS5296A | 10-bit, 200-MSPS, 4-channel, 61-dBFS SNR, 150-mW/ch and 12-bit, 80-MSPS, 8-channel, 70-dBFS SNR, 65-mW/ch ADC                                                   | VQFN (64)   | 9.00 mm × 9.00 mm   |

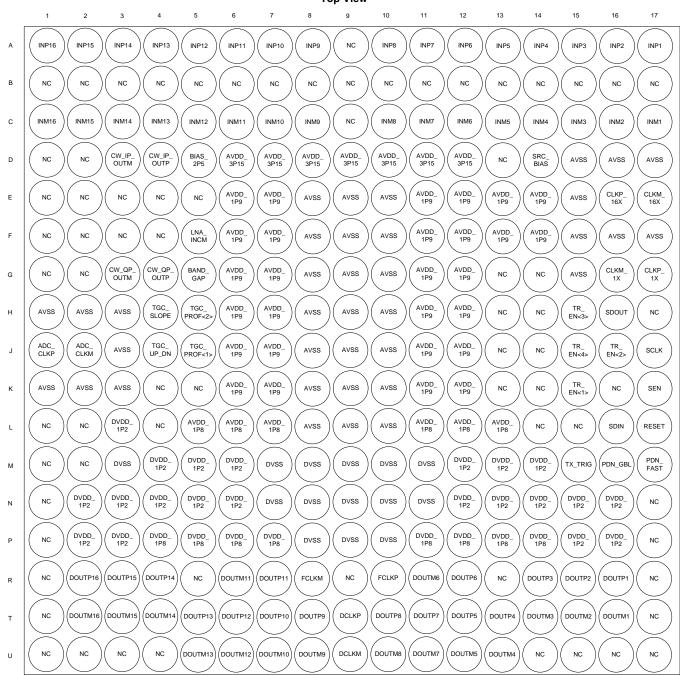

### 7 Pin Configuration and Functions

#### ZAV Package 289-Bumps NFBGA Top View

#### **Pin Functions**

|            | Pin Functions                                                                                                     |     |                                                                                                                                                                                                                                                                                         |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN        |                                                                                                                   |     |                                                                                                                                                                                                                                                                                         |  |  |

| NAME       | NO.                                                                                                               | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                             |  |  |

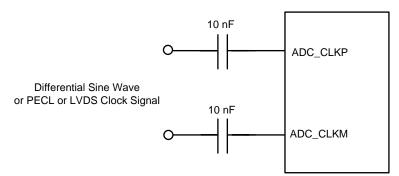

| ADC_CLKM   | J2                                                                                                                | I   | Differential clock input pin used for ADC conversion, negative. A single-ended clock is also supported. Connect ADC_CLKM to dc ground when using a single-ended clock.                                                                                                                  |  |  |

| ADC_CLKP   | J1                                                                                                                | I   | Differential clock input pin used for ADC conversion, positive. A single-ended clock is also supported. Connect the ADC clock to the ADC_CLKP pin when using a single-ended clock.                                                                                                      |  |  |

| AVDD_1P8   | L5-L7, L11-L13                                                                                                    | Р   | Analog supply pins, 1.8 V (ADC_CONV die)                                                                                                                                                                                                                                                |  |  |

| AVDD_1P9   | E6, E7, E11-E14, F6, F7,<br>F11-F14, G6, G7, G11, G12,<br>H6, H7, H11, H12, J6, J7,<br>J11, J12, K6, K7, K11, K12 | Р   | Analog supply pins, 1.9 V (VCA die) <sup>(1)</sup>                                                                                                                                                                                                                                      |  |  |

| AVDD_3P15  | D6-D12                                                                                                            | Р   | Analog supply pins, 3.15 V (VCA die)                                                                                                                                                                                                                                                    |  |  |

| AVSS       | D15-D17, E8-E10, E15, F8-<br>F10, F15-F17, G8-G10, G15,<br>H1-H3, H8-H10, J3, J8-J10,<br>K1-K3, K8-K10, L8-L10    | G   | Analog ground pins                                                                                                                                                                                                                                                                      |  |  |

| BAND_GAP   | G5                                                                                                                | 0   | Bypass to analog ground with a 1-µF capacitor.                                                                                                                                                                                                                                          |  |  |

| BIAS_2P5   | D5                                                                                                                | 0   | Bypass to analog ground with a 1-μF capacitor.                                                                                                                                                                                                                                          |  |  |

| CLKM_1X    | G16                                                                                                               | I   | Differential clock input for the 1X CW clock, negative. A single-ended clock is also supporte In single-ended clock mode, the CLKM_1X pin is internally pulled to ground.  In 1X clock mode, this pin is the negative quadrature-phase clock input for the CW mixer. (2)                |  |  |

| CLKP_1X    | G17                                                                                                               | I   | Differential clock input for the 1X CW clock, positive. A single-ended clock is also supported. Connect the 1X CW clock to the CLKP_1X pin when using a single-ended clock. In 1X clock mode, this pin is the positive quadrature-phase clock input for the CW mixer. (2)               |  |  |

| CLKM_16X   | E17                                                                                                               | I   | Differential clock input for the 16X, 8X, and 4X CW clocks, negative.  A single-ended clock is also supported.  In single-ended clock mode, the CLKM_16X pin is internally pulled to ground. (2)                                                                                        |  |  |

| CLKP_16X   | E16                                                                                                               | I   | Differential clock input for the 16X, 8X, and 4X CW clocks, positive.  A single-ended clock is also supported.  Connect the 16X CW clock to the CLKP_16X pin when using a single-ended clock.  In 1X CW clock mode, this pin is the positive in-phase clock input for the CW mixer. (2) |  |  |

| CW_IP_OUTM | D3                                                                                                                | 0   | In-phase CW differential summed current output, negative. (2)                                                                                                                                                                                                                           |  |  |

| CW_IP_OUTP | D4                                                                                                                | 0   | In-phase CW differential summed current output, positive. (2)                                                                                                                                                                                                                           |  |  |

| CW_QP_OUTM | G3                                                                                                                | 0   | Quadrature-phase CW differential summed current output, negative. (2)                                                                                                                                                                                                                   |  |  |

| CW_QP_OUTP | G4                                                                                                                | 0   | Quadrature-phase CW differential summed current output, positive. (2)                                                                                                                                                                                                                   |  |  |

| DCLKM      | U9                                                                                                                | 0   | Low-voltage differential signaling (LVDS) serialized data clock outputs                                                                                                                                                                                                                 |  |  |

| DCLKP      | Т9                                                                                                                |     | (receiver bit alignment)                                                                                                                                                                                                                                                                |  |  |

| DOUTM1     | T16                                                                                                               | 0   | LVDS serialized differential data outputs for channel 1                                                                                                                                                                                                                                 |  |  |

| DOUTP1     | R16                                                                                                               |     |                                                                                                                                                                                                                                                                                         |  |  |

| DOUTM2     | T15                                                                                                               | 0   | LVDS serialized differential data outputs for channel 2                                                                                                                                                                                                                                 |  |  |

| DOUTP2     | R15                                                                                                               |     |                                                                                                                                                                                                                                                                                         |  |  |

| DOUTM3     | T14                                                                                                               | 0   | LVDS serialized differential data outputs for channel 3                                                                                                                                                                                                                                 |  |  |

| DOUTP3     | R14                                                                                                               |     | 2.50 contained and only and output to one men                                                                                                                                                                                                                                           |  |  |

| DOUTM4     | U13                                                                                                               | 0   | LVDS serialized differential data outputs for channel 4                                                                                                                                                                                                                                 |  |  |

| DOUTP4     | T13                                                                                                               |     |                                                                                                                                                                                                                                                                                         |  |  |

| DOUTM5     | U12                                                                                                               | 0   | LVDS serialized differential data outputs for channel 5                                                                                                                                                                                                                                 |  |  |

| DOUTP5     | T12                                                                                                               |     | 2.50 contained annothing and output to ordinario                                                                                                                                                                                                                                        |  |  |

| DOUTM6     | R11                                                                                                               | 0   | LVDS serialized differential data outputs for channel 6                                                                                                                                                                                                                                 |  |  |

| DOUTP6     | R12                                                                                                               |     | 2.50 contained unformed data outputs for originate o                                                                                                                                                                                                                                    |  |  |

| DOUTM7     | U11                                                                                                               | 0   | LVDS serialized differential data outputs for channel 7                                                                                                                                                                                                                                 |  |  |

| DOUTP7     | T11                                                                                                               |     | EVEC Serialized differential data outputs for chariffer /                                                                                                                                                                                                                               |  |  |

| DOUTM8     | U10                                                                                                               | 0   | LVDS serialized differential data outputs for channel 8                                                                                                                                                                                                                                 |  |  |

| DOUTP8     | T10                                                                                                               |     | LVDS senanzed differential data outputs for charmer 6                                                                                                                                                                                                                                   |  |  |

| DOUTM9     | U8                                                                                                                | 0   | LVDS serialized differential data outputs for channel 9                                                                                                                                                                                                                                 |  |  |

| DOUTP9     | Т8                                                                                                                |     | Ev DO Sonanzea amerentia data outpus for Graffiel 5                                                                                                                                                                                                                                     |  |  |

<sup>(1)</sup> In low-power mode, the typical power supply for AVDD\_1P9 is 1.8 V.(2) When CW mode is not used, this pin can be floated.

# Pin Functions (continued)

|          | PIN                                                     |     |                                                                                                                 |  |

|----------|---------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.                                                     | I/O | DESCRIPTION                                                                                                     |  |

| DOUTM10  | U7                                                      | .,0 | DESCRIPTION                                                                                                     |  |

| DOUTP10  | T7                                                      | 0   | LVDS serialized differential data outputs for channel 10                                                        |  |

| DOUTM11  | R6                                                      |     |                                                                                                                 |  |

| DOUTP11  | R7                                                      | 0   | LVDS serialized differential data outputs for channel 11                                                        |  |

| DOUTM12  | U6                                                      |     |                                                                                                                 |  |

| DOUTP12  | T6                                                      | 0   | LVDS serialized differential data outputs for channel 12                                                        |  |

| DOUTM13  | U5                                                      |     |                                                                                                                 |  |

| DOUTP13  | T5                                                      | Ο   | LVDS serialized differential data outputs for channel 13                                                        |  |

| DOUTM14  | T4                                                      |     |                                                                                                                 |  |

| DOUTP14  | R4                                                      | 0   | LVDS serialized differential data outputs for channel 14                                                        |  |

| DOUTM15  | T3                                                      |     |                                                                                                                 |  |

| DOUTP15  | R3                                                      | 0   | LVDS serialized differential data outputs for channel 15                                                        |  |

| DOUTM16  | T2                                                      |     |                                                                                                                 |  |

| DOUTP16  | R2                                                      | Ο   | LVDS serialized differential data outputs for channel 16                                                        |  |

| DVDD_1P2 | L3, M4-M6, M12-M14, N2-N6,<br>N12-N16, P2, P3, P15, P16 | Р   | 1.2-V digital supply pins for the ADC digital block                                                             |  |

| DVDD_1P8 | P4-P7, P11-P14                                          | Р   | 1.8-V digital supply pins for the ADC digital, digital I/Os, phase-locked loop (PLL), and LVDS interface blocks |  |

| DVSS     | M3, M7-M11, N7-N11, P8-<br>P10                          | G   | Digital ground (ADC_CONV die).                                                                                  |  |

| FCLKM    | R8                                                      | 0   | LVDS serialized differential frame clock outputs (receiver word alignment).                                     |  |

| FCLKP    | R10                                                     | U   | LVDS Senailzed differential frame clock outputs (receiver word alignment).                                      |  |

| INM1     | C17                                                     | 1   | Complementary analog input for channel 1. <sup>(3)</sup>                                                        |  |

| INM2     | C16                                                     | Ţ   | Complementary analog input for channel 2. (3)                                                                   |  |

| INM3     | C15                                                     | I   | Complementary analog input for channel 3. (3)                                                                   |  |

| INM4     | C14                                                     | 1   | Complementary analog input for channel 4. (3)                                                                   |  |

| INM5     | C13                                                     | 1   | Complementary analog input for channel 5. (3)                                                                   |  |

| INM6     | C12                                                     | 1   | Complementary analog input for channel 6. (3)                                                                   |  |

| INM7     | C11                                                     | 1   | Complementary analog input for channel 7. (3)                                                                   |  |

| INM8     | C10                                                     | 1   | Complementary analog input for channel 8. <sup>(3)</sup>                                                        |  |

| INM9     | C8                                                      | ı   | Complementary analog input for channel 9. <sup>(3)</sup>                                                        |  |

| INM10    | C7                                                      | 1   | Complementary analog input for channel 10. <sup>(3)</sup>                                                       |  |

| INM11    | C6                                                      | ı   | Complementary analog input for channel 11. <sup>(3)</sup>                                                       |  |

| INM12    | C5                                                      | 1   | Complementary analog input for channel 12. <sup>(3)</sup>                                                       |  |

| INM13    | C4                                                      | 1   | Complementary analog input for channel 13. <sup>(3)</sup>                                                       |  |

| INM14    | C3                                                      | I   | Complementary analog input for channel 14. (3)                                                                  |  |

| INM15    | C2                                                      | ı   | Complementary analog input for channel 15. (3)                                                                  |  |

| INM16    | C1                                                      | 1   | Complementary analog input for channel 16. (3)                                                                  |  |

| INP1     | A17                                                     | I   | Analog input for channel 1. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP2     | A16                                                     | I   | Analog input for channel 2. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP3     | A15                                                     | I   | Analog input for channel 3. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP4     | A14                                                     | 1   | Analog input for channel 4. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP5     | A13                                                     | I   | Analog input for channel 5. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP6     | A12                                                     | I   | Analog input for channel 6. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP7     | A11                                                     | I   | Analog input for channel 7. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP8     | A10                                                     | I   | Analog input for channel 8. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP9     | A8                                                      | 1   | Analog input for channel 9. AC-couple to device input with a 10-nF capacitor.                                   |  |

| INP10    | A7                                                      | I   | Analog input for channel 10. AC-couple to device input with a 10-nF capacitor.                                  |  |

| INP11    | A6                                                      | I   | Analog input for channel 11. AC-couple to device input with a 10-nF capacitor.                                  |  |

<sup>(3)</sup> The LNA high-pass filter (HPF) response of the channel depends on the capacitor connected at the INMx pin. By default, leave this pin floating. For very low-frequency applications, connect a capacitor  $> 1 \mu F$ .

# Pin Functions (continued)

|              | PIN                                                                                                                                                                                                                              |     |                                                                                                                                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO. I/O |                                                                                                                                                                                                                                  | I/O | DESCRIPTION                                                                                                                                         |

| INP12        | A5                                                                                                                                                                                                                               | I   | Analog input for channel 12. AC-couple to device input with a 10-nF capacitor.                                                                      |

| INP13        | A4                                                                                                                                                                                                                               | I   | Analog input for channel 13. AC-couple to device input with a 10-nF capacitor.                                                                      |

| INP14        | A3                                                                                                                                                                                                                               | I   | Analog input for channel 14. AC-couple to device input with a 10-nF capacitor.                                                                      |

| INP15        | A2                                                                                                                                                                                                                               | I   | Analog input for channel 15. AC-couple to device input with a 10-nF capacitor.                                                                      |

| INP16        | A1                                                                                                                                                                                                                               | I   | Analog input for channel 16. AC-couple to device input with a 10-nF capacitor.                                                                      |

| LNA_INCM     | F5                                                                                                                                                                                                                               | 0   | Bypass to ground with a 1-μF capacitor.                                                                                                             |

| NC           | A9, B1-B17, C9, D1, D2, D13,<br>E1-E5, F1-F4, G1, G2, G13,<br>G14, H13, H14, H17, J13,<br>J14, K4, K5, K13, K14, K16,<br>L1, L2, L4, L14, L15, M1, M2,<br>R5, R9, R13, N1, N17, P1,<br>R1, R17, P17, T1, T17, U1-<br>U4, U14-U17 | _   | Unused pins; do not connect                                                                                                                         |

| PDN_FAST     | M17                                                                                                                                                                                                                              | I   | Partial power-down control pin for the entire device with an internal 16-k $\Omega$ pulldown resistor; active high. (4)                             |

| PDN_GBL      | M16                                                                                                                                                                                                                              | 1   | Global (complete) power-down control pin for the entire device with an internal 16-k $\Omega$ pulldown resistor; active high. (4)                   |

| RESET        | L17                                                                                                                                                                                                                              | I   | Hardware reset pin with an internal 16-kΩ pull-down resistor; active high. (4)                                                                      |

| SCLK         | J17                                                                                                                                                                                                                              | I   | Serial programming interface clock pin with an internal 16-kΩ pulldown resistor. (4)                                                                |

| SDIN         | L16                                                                                                                                                                                                                              | I   | Serial programming interface data pin with an internal 16-kΩ pulldown resistor. (4)                                                                 |

| SDOUT        | H16                                                                                                                                                                                                                              | 0   | Serial programming interface readout pin. This pin is in tri-state by default. (4)                                                                  |

| SEN          | K17                                                                                                                                                                                                                              | I   | Serial programming interface enable pin, active low. This pin has a 16-k $\Omega$ pullup resistor. (4)                                              |

| SRC_BIAS     | D14                                                                                                                                                                                                                              | 0   | Bypass to ground with a 1-μF capacitor.                                                                                                             |

| TGC_PROF<1>  | J5                                                                                                                                                                                                                               | 1   | Digital TGC profile 1 select pin. This pin has an internal 150-kΩ pulldown resistor; active high. (4)                                               |

| TGC_PROF<2>  | H5                                                                                                                                                                                                                               | 1   | Digital TGC profile 2 select pin. This pin has an internal 150-k $\Omega$ pulldown resistor; active high. (4)                                       |

| TGC_SLOPE    | H4                                                                                                                                                                                                                               | I   | Digital TGC control pin. This pin has an internal 150-k $\Omega$ pulldown resistor. (4)                                                             |

| TGC_UP_DN    | J4                                                                                                                                                                                                                               | I   | Digital TGC control pin. This pin has an internal 150-k $\Omega$ pulldown resistor. (4)                                                             |

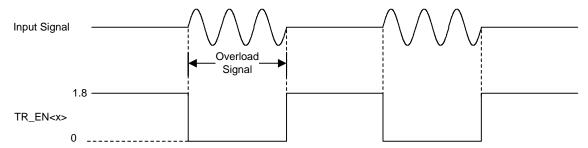

| TR_EN<1>     | K15                                                                                                                                                                                                                              | 1   | TR enable pin 1; disconnects the LNA HPF from the input pins of channels 1 to 4. $^{(4)}$ This pin has an internal 150-k $\Omega$ pullup resistor.  |

| TR_EN<2>     | J16                                                                                                                                                                                                                              | I   | TR enable pin 2; disconnects the LNA HPF from the input pins of channels 5 to 8. $^{(4)}$ This pin has an internal 150-k $\Omega$ pullup resistor.  |

| TR_EN<3>     | H15                                                                                                                                                                                                                              | Į   | TR enable pin 3; disconnects the LNA HPF from the input pins of channels 9 to 12. $^{(4)}$ This pin has an internal 150-k $\Omega$ pullup resistor. |

| TR_EN<4>     | J15                                                                                                                                                                                                                              | I   | TR enable pin 4; disconnects the LNA HPF from the input pins of channels 13 to 16. (4) This pin has an internal 150-k $\Omega$ pullup resistor.     |

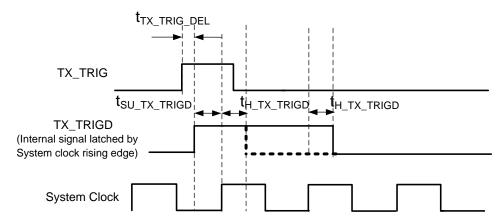

| TX_TRIG      | M15                                                                                                                                                                                                                              | I   | This pin synchronizes test patterns across devices. This pin has a 20-k $\Omega$ pulldown resistor. (4)                                             |

#### (4) A 1.8-V logic level is required.

# **Table 1. Pin Name to Signal Name Map**

| SIGNAL NUMBER | PIN NAME                | SIGNAL NAME |

|---------------|-------------------------|-------------|

| 1             | ADC_CLKP - ADC_CLKM     | ADC_CLK     |

| 2             | CLKP_1X - CLKM_1X       | CW_CLK1X    |

| 3             | CLKP_16X - CLKM_16X     | CW_CLK_NX   |

| 4             | CW_IP_OUTP - CW_IP_OUTM | CW_IP_OUT   |

| 5             | CW_QP_OUTP - CW_QP_OUTM | CW_QP_OUT   |

| 6             | DOUTPx – DOUTMx         | DOUT        |

| 7             | FCLKP – FCLKM           | FCLK        |

| 8             | DCLKP – DCLKM           | DCLK        |

| 9             | CMLx_OUTP - CMLx_OUTM   | CMLx_OUT    |

### 8 Specifications

### 8.1 Absolute Maximum Ratings

over operating free-air temperature range, unless otherwise noted (1)

|                           |                           | MIN  | MAX  | UNIT |

|---------------------------|---------------------------|------|------|------|

|                           | AVDD_1P8                  | -0.3 | 2.2  |      |

|                           | AVDD_1P9                  | -0.3 | 2.2  |      |

| Supply voltage range      | AVDD_3P15                 | -0.3 | 3.9  | V    |

| ,                         | DVDD_1P2                  | -0.3 | 1.35 |      |

|                           | AVDD_1P8                  |      |      |      |

| Voltage at analog inputs  |                           | -0.3 |      | V    |

| Voltage at digital inputs |                           | -0.3 |      | V    |

| Temperature               |                           |      | 105  | °C   |

|                           | Storage, T <sub>stg</sub> | -55  | 150  |      |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| \/                 | Clastrostatia diasharas | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range, unless otherwise noted

|                     |                                    | PARAMETER                                                 | MIN  | TYP  | MAX  | UNIT |

|---------------------|------------------------------------|-----------------------------------------------------------|------|------|------|------|

| SUPPLIE             | S                                  |                                                           |      |      |      |      |

| V <sub>A_1P8</sub>  | AVDD_1P8 voltage                   |                                                           | 1.7  | 1.8  | 1.9  | V    |

| V                   | AVDD_1P9 voltage                   | Low-noise mode, medium-power mode                         | 1.8  | 1.9  | 2.0  | V    |

| V <sub>A_1P9</sub>  | AVDD_1F9 Vollage                   | Low-power mode                                            | 1.75 | 1.8  | 2.0  | V    |

| V <sub>A_3P15</sub> | AVDD_3P15 voltage                  |                                                           | 3    | 3.15 | 3.3  | V    |

| $V_{D_{-}1P2}$      | DVDD_1P2 voltage                   |                                                           | 1.15 | 1.2  | 1.25 | V    |

| $V_{D_1P8}$         | DVDD_1P8 voltage                   |                                                           | 1.7  | 1.8  | 1.9  | V    |

| TEMPER              | ATURE                              |                                                           |      |      | Ÿ    |      |

| T <sub>A</sub>      | Ambient temperature                |                                                           | -40  |      | 85   | ů    |

| BIAS VO             | LTAGES                             |                                                           |      |      |      |      |

|                     |                                    | ADC_CLKP, ADC_CLKM in differential mode                   |      | 0.7  |      |      |

|                     | Common-mode voltage <sup>(1)</sup> | CLKP_1X, CLKM_1X, CLKP_16X, CLKM_16X in differential mode |      | 1.5  |      | V    |

|                     | Common-mode voltage                | CW_IP_OUTP, CW_IP_OUTM, CW_QP_OUTP, CW_QP_OUTM            |      | 0.9  |      | V    |

|                     |                                    | (INM1, INP1), (INM2, INP2)(INM16, INP16)                  |      | 1    |      |      |

|                     |                                    | BAND_GAP                                                  |      | 1.2  |      |      |

|                     | Bias voltage <sup>(1)</sup>        | BIAS_2P5                                                  |      | 2.5  |      | \/   |

|                     | bias voltage "                     | LNA_INCM                                                  |      | 1    |      | V    |

|                     |                                    | SRC_BIAS                                                  |      | 0.5  |      |      |

<sup>(1)</sup> Internally set by the device.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **Recommended Operating Conditions (continued)**

over operating free-air temperature range, unless otherwise noted

|                    |                              | PARAMETER                                                                         |          | MIN | TYP  | MAX | UNIT         |

|--------------------|------------------------------|-----------------------------------------------------------------------------------|----------|-----|------|-----|--------------|

| ADC CL             | OCK INPUT: ADC_CLK           |                                                                                   |          |     |      |     |              |

|                    | ADC alask framework          | 14-bit ADC resolution                                                             |          | 5   |      | 65  | MHz          |

| f <sub>CLKIN</sub> | ADC clock frequency          | 12-bit ADC resolution                                                             |          | 5   |      | 80  | IVIHZ        |

|                    |                              | Sine-wave, ac-coupled                                                             |          | 0.7 |      |     | ·            |

| $V_{DEADC}$        | Differential clock amplitude | LVPECL, ac-coupled                                                                |          |     | 1.6  |     | $V_{PP}$     |

|                    |                              | LVDS, ac-coupled                                                                  |          |     | 0.7  |     | ı            |

| V <sub>SEADC</sub> | Single-ended clock amplitude | LVCMOS on ADC_CLKP with ADC_CLKM grounded                                         |          |     | 1.8  |     | V            |

| D <sub>ADC</sub>   | ADC_CLK duty cycle           |                                                                                   |          |     | 50%  | 60% |              |

| CW CLO             | CK INPUT: CW_CLK1X, CW_      | _CLK_NX                                                                           |          |     |      |     |              |

|                    |                              | CW_CLK1X across CW clock modes in resee the CW_CLK_MODE register bits in research |          |     |      | 8   | MHz          |

| CW <sub>CLK</sub>  | CW clock frequency           | CW CLK NX across CW clock modes;                                                  | 16X mode |     | 16X  |     | ·            |

| 02.1               | , ,                          | see the CW_CLK_MODE register bits in                                              | 8X mode  |     | 8X   |     | CW_<br>CLK1X |

|                    |                              | register 192                                                                      | 4X mode  |     | 4X   |     | OLIVIA       |

| $V_{DECW}$         | Differential clock amplitude | CW_CLK1X, CW_CLK_NX. LVDS, ac-cou                                                 | pled     |     | 0.7  |     | $V_{PP}$     |

| V <sub>SECW</sub>  | Single-ended clock amplitude | LVCMOS on CLKP_1X, CLKP_16X with CLKM_1X, CLKM_16X grounded or floating           |          |     | 3.15 |     | V            |

| D <sub>CW</sub>    | CLK duty cycle               | CW_CLK1X, CW_CLK_NX                                                               |          | 40% | 50%  | 60% |              |

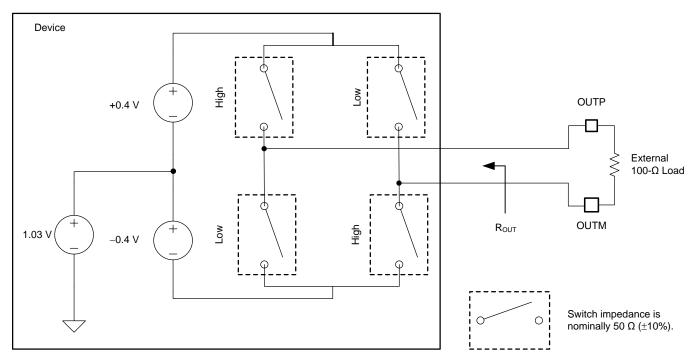

|                    | OUTPUT (LVDS)                |                                                                                   |          |     |      |     |              |

| R <sub>L</sub>     | Differential load resistance |                                                                                   |          |     | 100  |     | Ω            |

#### 8.4 Thermal Information

|                        |                                              | AFE5816     |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | ZAV (NFBGA) | UNIT |

|                        |                                              | 289 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 26.1        | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 5.6         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 11.7        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.2         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 11.0        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 8.5 Electrical Characteristics: TGC Mode

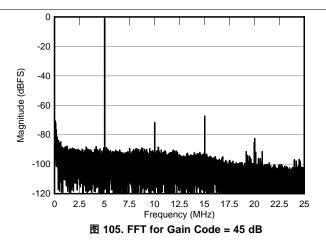

At  $T_A$  = 25°C, unless otherwise noted. **Supply:** AVDD\_1P8 = 1.8 V, AVDD\_1P9 = 1.9 V, AVDD\_3P15 = 3.15 V, and DVDD\_1P2 = 1.2 V, DVDD\_1P8 = 1.8 V. **Input to the device:** input signal is ac-coupled to INP with a 10-nF capacitor and is applied with source resistance  $R_S$  = 50  $\Omega$  at frequency  $f_{IN}$  = 5 MHz, and a 50-MHz differential clock is applied on ADC\_CLK. **Device settings:** gain code = 319 (total gain = 45 dB), 14-bit ADC resolution, LVDS interface to capture ADC data, and output amplitude  $V_{OUT}$  = -1 dBFS. Minimum and maximum values are specified across the full temperature range.

|                    | PARAMETER                    | TEST CONDI                                                        | TION                                     | MIN TYP                              | MAX | UNIT                 |

|--------------------|------------------------------|-------------------------------------------------------------------|------------------------------------------|--------------------------------------|-----|----------------------|

| GENERAL            |                              |                                                                   |                                          |                                      |     |                      |

|                    |                              | At INP_SOURCE node; see the Function                              | nal Block Diagram section                | 1                                    |     | .,                   |

| $V_{MAX}$          | Maximum linear input voltage | At INPx node; see the Functional Block                            | Diagram section                          | 0.4                                  |     | $V_{PP}$             |

| C <sub>INP</sub>   | Input capacitance            |                                                                   |                                          |                                      |     | pF                   |

| G <sub>CODE</sub>  | Gain code <sup>(1)</sup>     | Programs the total gain                                           | Programs the total gain                  |                                      | 319 |                      |

|                    |                              | Low-noise mode and medium-power mo                                | ode                                      | (6 + 0.125 ×<br>G <sub>CODE</sub> )  |     | ٩D                   |

| G <sub>TOT</sub>   | Total gain                   | Low-power mode                                                    |                                          | (12 + 0.125 ×<br>G <sub>CODE</sub> ) |     |                      |

| G <sub>RANGE</sub> | Gain range                   |                                                                   |                                          | 39                                   |     | dB                   |

| G <sub>SLOPE</sub> | Gain slope                   |                                                                   |                                          |                                      |     | dB/G <sub>CODE</sub> |

| T <sub>TGC</sub>   | TGC response time            | G <sub>CODE</sub> changed from 64 to 319                          | G <sub>CODE</sub> changed from 64 to 319 |                                      |     | μs                   |

|                    |                              |                                                                   | Low-noise mode                           | 1                                    |     | 1                    |

| $V_{N,IRN}$        | Input voltage noise          | $R_S = 0 \Omega$ , calculated in band of 4-MHz to 6-MHz frequency | Medium-power mode                        | 1.3                                  |     | nV/√ <del>Hz</del>   |

|                    |                              | lo o ivii iz iroquorioy                                           | Low-power mode                           | 1.45                                 |     |                      |

| I <sub>N,IRN</sub> | Input-referred current noise | Across low-noise, medium-power, and l                             | ow-power mode                            | 1.2                                  |     | pA/√ <del>Hz</del>   |

|                    |                              |                                                                   | Low-noise mode                           | 3.6                                  |     | 1                    |

|                    |                              | $R_S = 50 \Omega$                                                 | Medium-power mode                        | 4.5                                  |     | dB                   |

| NE                 | Naine 6                      |                                                                   | Low-power mode                           | 5.0                                  |     |                      |

| NF                 | Noise figure <sup>(2)</sup>  |                                                                   | Low-noise mode                           | 1.2                                  |     |                      |

|                    |                              | $R_S = 400 \Omega$                                                | Medium-power mode                        | 1.5                                  |     | dB                   |

|                    |                              |                                                                   | Low-power mode                           | 1.6                                  |     |                      |

<sup>(1)</sup> The gain code range from 0 to 63 controls the input attenuation and the gain code range from 64 to 319 controls the LNA gain.

<sup>(2)</sup> NF is measured as the SNR at the output of the device relative to the SNR at the input resulting from ths noise of source resistance Rs.

At  $T_A$  = 25°C, unless otherwise noted. **Supply:** AVDD\_1P8 = 1.8 V, AVDD\_1P9 = 1.9 V, AVDD\_3P15 = 3.15 V, and DVDD\_1P2 = 1.2 V, DVDD\_1P8 = 1.8 V. **Input to the device:** input signal is ac-coupled to INP with a 10-nF capacitor and is applied with source resistance  $R_S$  = 50  $\Omega$  at frequency  $f_{IN}$  = 5 MHz, and a 50-MHz differential clock is applied on ADC\_CLK. **Device settings:** gain code = 319 (total gain = 45 dB), 14-bit ADC resolution, LVDS interface to capture ADC data, and output amplitude  $V_{OUT}$  = -1 dBFS. Minimum and maximum values are specified across the full temperature range.

|                    | PARAMETER                               | TEST COND                                                                         | ITION                                  | MIN  | TYP     | MAX | UNIT          |

|--------------------|-----------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------|------|---------|-----|---------------|

| GENERAL            | (continued)                             |                                                                                   |                                        |      |         |     |               |

|                    |                                         | Without a signal, calculated in a 1-MHz                                           | $R_S = 330 \Omega$                     |      | -20     |     |               |

|                    |                                         | to 10-MHz bandwidth                                                               | $R_S = 100 \Omega$                     |      | -26     |     |               |

|                    | Channel-to-channel noise                | With a signal, calculated in a 1-MHz to                                           | Total gain = 45 dB                     |      | -17     |     |               |

| K <sub>CORR</sub>  | correlation factor <sup>(3)</sup>       | 10-MHz bandwidth                                                                  | Total gain = 26 dB                     |      | -14     |     | dB            |

|                    |                                         | With a signal, calculated in a 1-MHz                                              | Total gain = 45 dB                     |      | -13     |     |               |

|                    |                                         | bandwidth around a 5-MHz input signal frequency                                   | Total gain = 26 dB                     |      | -10     |     |               |

| SNR                | Signal to paiga ratio                   | SNR calculated in 750 kHz to Nyquist                                              | Total gain = 14 dB                     | 65   | 68      |     | dDEC          |

| SINK               | Signal-to-noise ratio                   | bandwidth                                                                         | Total gain = 45 dB                     | 55   | 58      |     | UDFS          |

| SNR <sub>NB</sub>  | Narrow-band SNR                         | SNR calculated in 2-MHz bandwidth around input signal frequency                   | Total gain = 30 dB                     | 72.5 | 76      |     | dBFS          |

|                    |                                         |                                                                                   |                                        |      | 10      |     |               |

|                    |                                         |                                                                                   | Low-noise and medium-                  |      | 15      |     |               |

|                    |                                         |                                                                                   | power mode                             |      | 20      |     |               |

| LPF                | 3rd-order, low-pass filter              | –3-dB cutoff frequency across<br>LPF_PROG register settings;                      |                                        |      | 25      |     | ns Degrees dB |

| LFF                | Sid-order, low-pass liller              | see register 199                                                                  |                                        |      | 5       |     | IVITIZ        |

|                    |                                         |                                                                                   | Low-power mode                         |      | 7.5     |     |               |

|                    |                                         |                                                                                   | Low-power mode                         |      | 10      |     |               |

|                    |                                         |                                                                                   |                                        |      | 12.5    |     |               |

| $\Delta_{LPF}$     | LPF bandwidth variation                 |                                                                                   |                                        |      | ±5%     |     |               |

| $\Delta_{Gr}$      | Channel-to-channel group delay matching | 2-MHz to 15-MHz input signal frequence                                            | 2-MHz to 15-MHz input signal frequency |      |         |     | ns            |

| $\Delta_{\phi}$    | Channel-to-channel phase matching       | 15-MHz signal                                                                     |                                        |      | 11      |     | Degrees       |

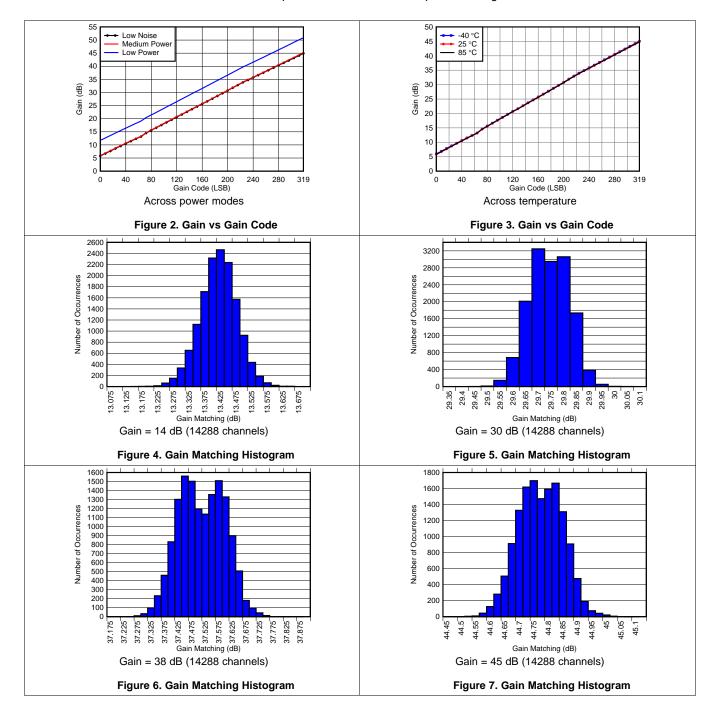

|                    |                                         | Device-to-device, average across                                                  | G <sub>CODE</sub> < 64                 |      | ±0.5    |     |               |

| 0                  | 0:                                      | channels                                                                          | G <sub>CODE</sub> > 64                 | -1   | ±0.5    | 1   | ID.           |

| G <sub>MATCH</sub> | Gain matching                           | Observation abservation and desire                                                | G <sub>CODE</sub> < 64                 |      | ±0.5    |     | ав            |

|                    |                                         | Channel-to-channel, same device                                                   | G <sub>CODE</sub> > 64                 | -1   | ±0.5    | 1   |               |

| HD2                | Second-order harmonic                   | Output amplitude = -1 dBFS, gain = 45                                             | dB                                     |      | -65     |     | dD-           |

| HD2                | distortion                              | Output amplitude = -1 dBFS, gain = 6 d                                            | dB                                     |      | -55     |     | abc           |

| LIDO               | Third-order harmonic                    | Output amplitude = -1 dBFS, gain = 45                                             | dB                                     |      | -60     |     | -ID-          |

| HD3                | distortion                              | Output amplitude = -1 dBFS, gain = 6 d                                            | dB                                     |      | -60     |     | abc           |

| TUD                | Tatal barras and addantian              | Output amplitude = -1 dBFS, gain = 45                                             | dB                                     |      | -58     |     | -ID-          |

| THD                | Total harmonic distortion               | Output amplitude = -1 dBFS, gain = 6 dB                                           |                                        |      | -54     |     | UDC           |

| IMD3               | Third-order intermodulation distortion  | Input frequency 1 = 5 MHz at -1 dBFS,<br>input frequency 2 = 5.01 MHz at -21 dBFS |                                        |      | -75     |     | dBc           |

| XTALK              | Fundamental crosstalk                   | Signal applied to a single channel. Crosstalk measured on neighboring channel.    |                                        |      | -55     |     | dBc           |

| PN <sub>1kHz</sub> | Phase noise                             | Calculated at 1-kHz offset from 5-MHz                                             | input signal frequency                 |      | -129    |     | dBc/Hz        |

| V <sub>ORO</sub>   | Output offset                           |                                                                                   |                                        |      | ±600    |     | LSB           |

| G <sub>LNA</sub>   | LNA gain range in TGC mode              |                                                                                   |                                        | 1    | 4 to 45 |     | dB            |

<sup>(3)</sup> The noise-correlation factor is defined as 10 x log<sub>10</sub>[Nc / (Nc + Nu)], where Nc is the correlated noise power in a single channel and Nu is the uncorrelated noise power in a single channel. The noise-correlation factor measurement is described by the equation:

Nc

N\_16Ch

1

$$\frac{NC}{(Nu+Nc)} = \frac{N_{-}10CH}{(N_{-}1Ch\times240)} - \frac{1}{15}$$

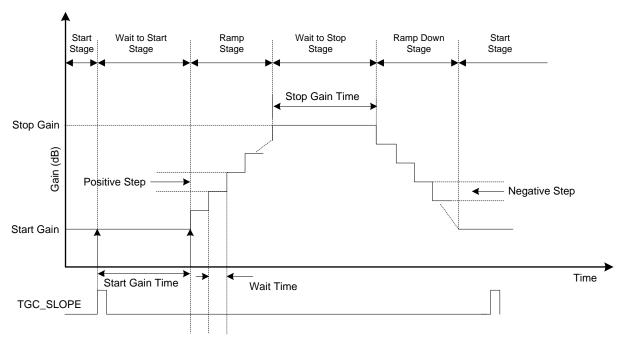

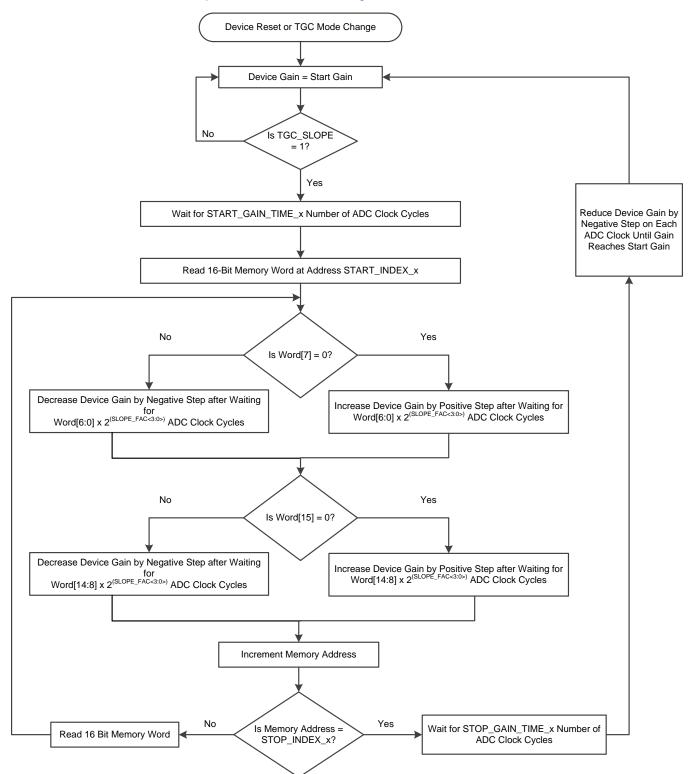

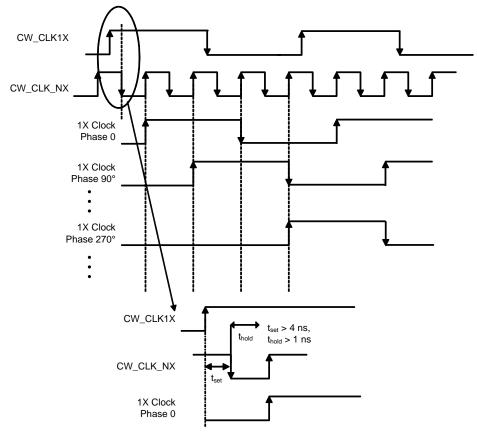

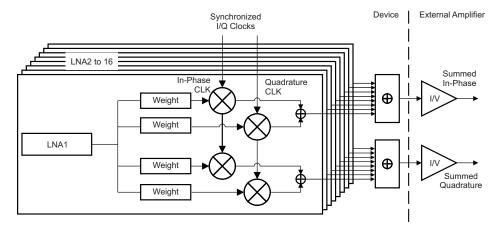

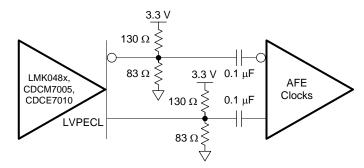

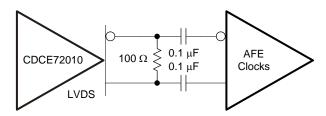

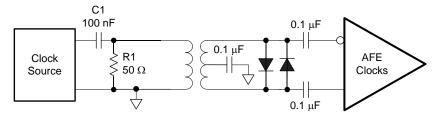

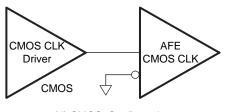

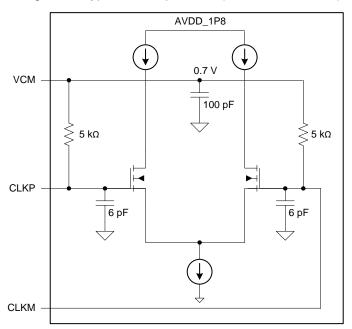

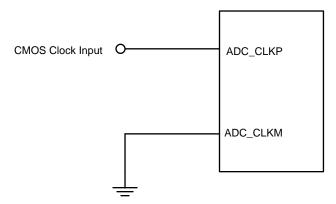

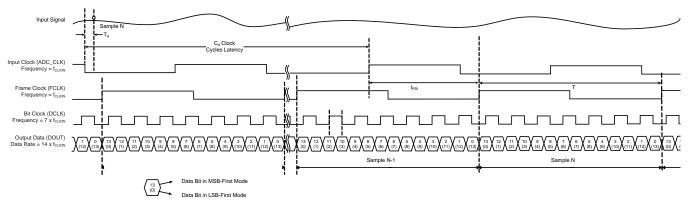

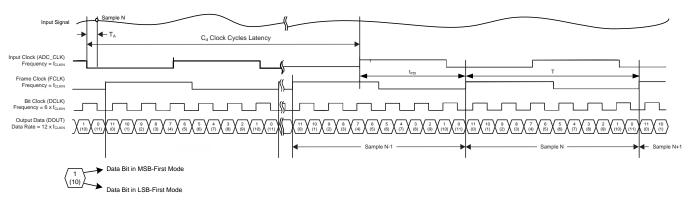

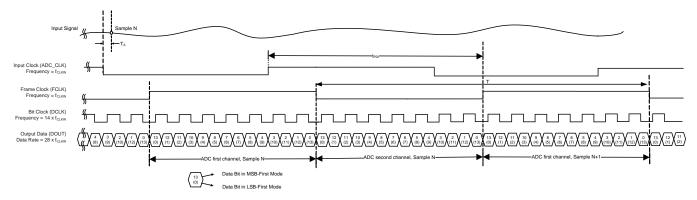

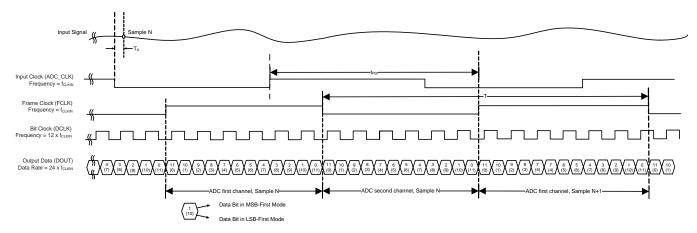

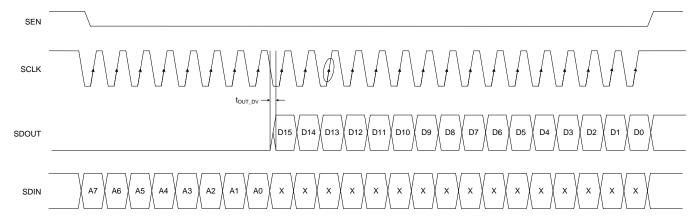

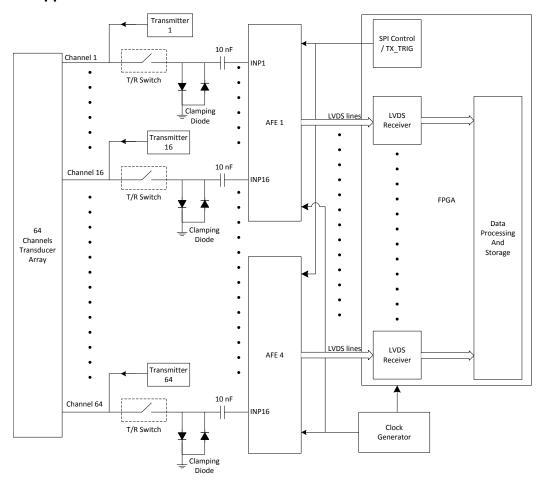

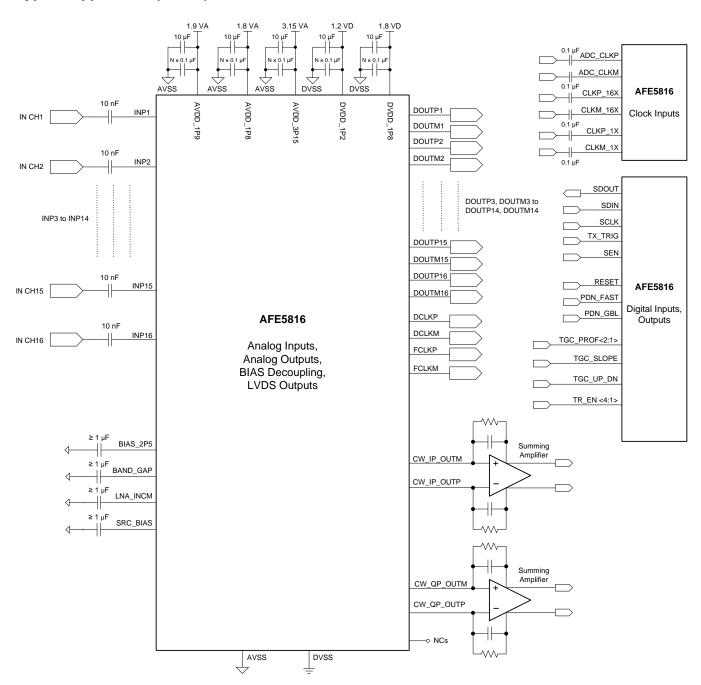

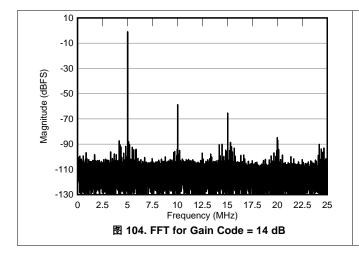

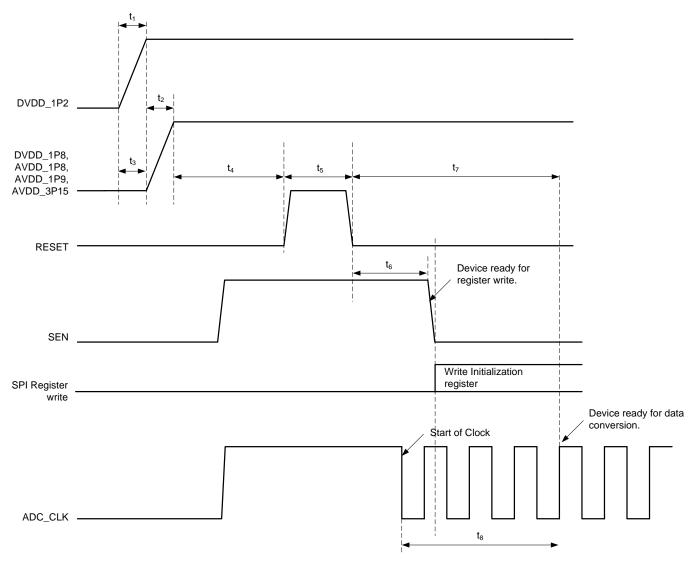

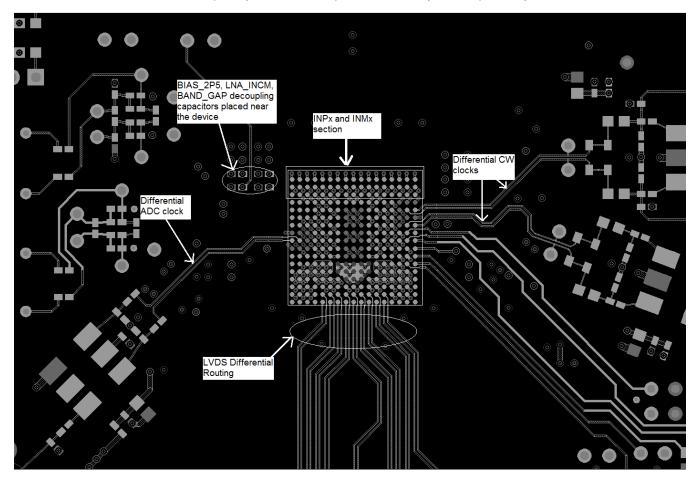

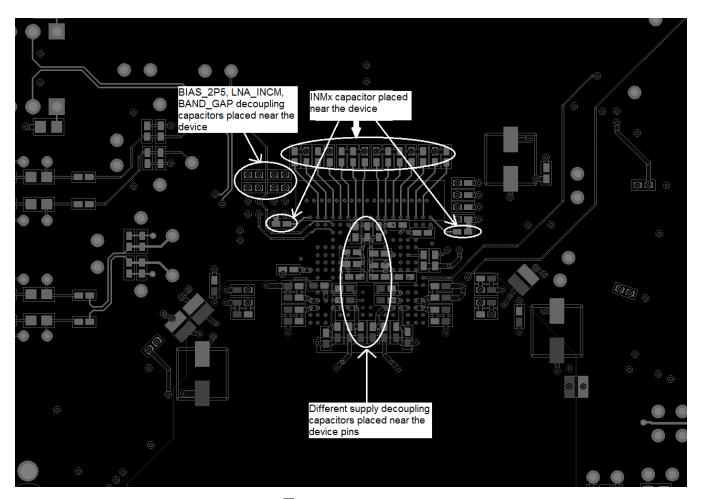

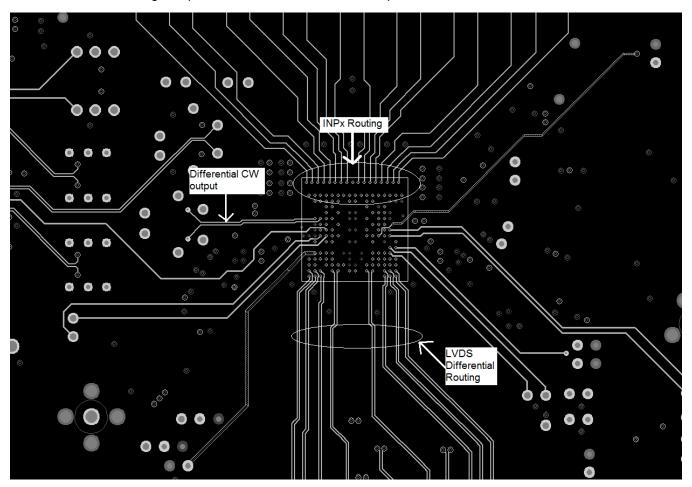

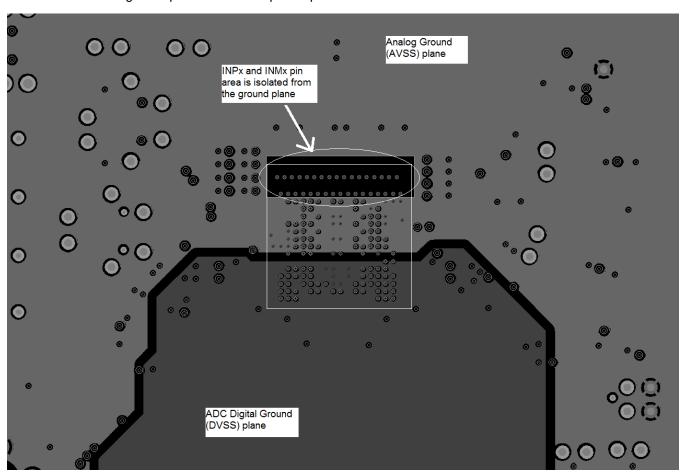

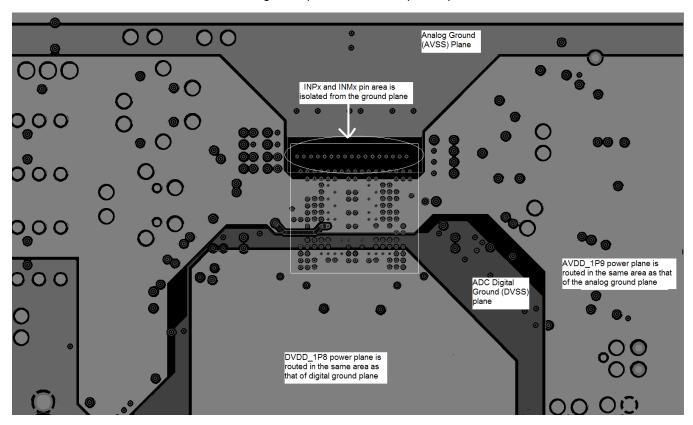

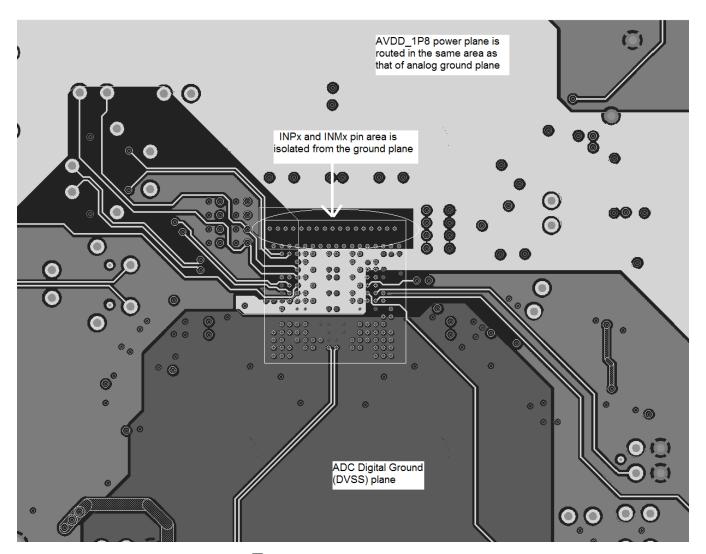

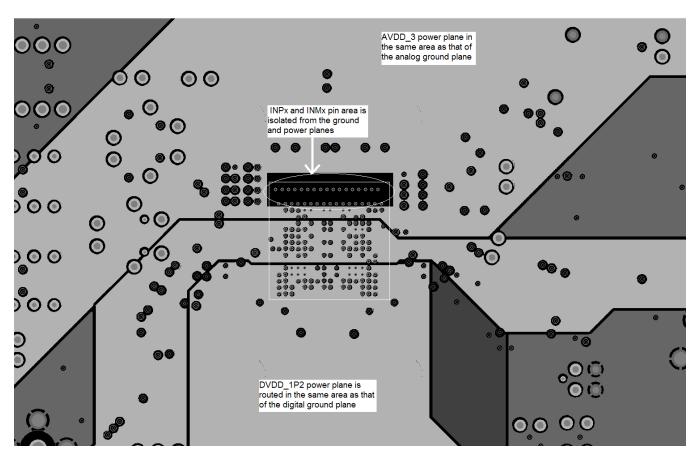

where N\_16CH is the noise power of the summed 16 channels and N\_1CH is the noise power of one channel.