CSD43301Q5M

ZHCSAI6B-DECEMBER 2012-REVISED MAY 2013

www.ti.com.cn

# NexFET™ 智能同步整流器

### 特性

- V<sub>DD</sub>为 4.5V 时, R<sub>on</sub>为 55mΩ(典型值)

- 集成

- 最大额定电流 80A

- 高密度 小外形尺寸无引线 (SON) 5mm × 6mm 封装

- 超低电感封装

- 系统已优化的印刷电路板 (PCB) 封装

- 与 **TTL IN** 信号兼容

- 无卤素

- 符合 RoHS 绿色环保标准-无铅端子镀层无卤素

## 应用范围

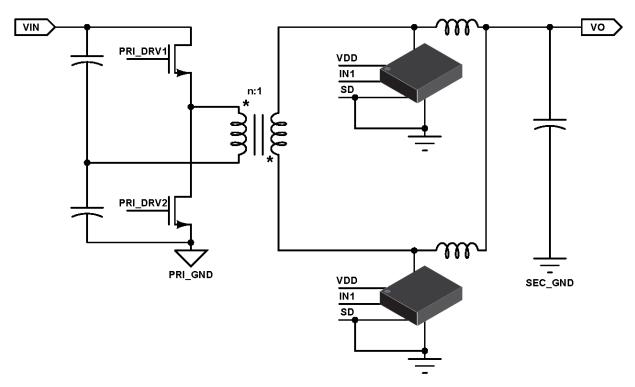

• 针对 DC/DC 转换器的次级同步整流

## 说明

CSD43301Q5M NexFET™ 智能同步整流器是一款针 对高功率高密度 DC/DC 转换器内的次级同步整流而进 行了高度优化的设计。这个产品集成有驱动器集成电 路 (IC) 和超低功耗 R<sub>on</sub>功率金属氧化物半导体场效应 晶体管 (MOSFET) 来完善同步整流功能。此外,已经 对印刷电路板 (PCB) 封装进行了优化以帮助减少设计 时间并简化总体系统设计。

| 订购信息        |                                     |             |      |      |  |  |  |  |  |  |

|-------------|-------------------------------------|-------------|------|------|--|--|--|--|--|--|

| 器件          | 封装                                  | 介质          | 数量   | 出货   |  |  |  |  |  |  |

| CSD43301Q5M | 小外形尺寸无引线<br>(SON) 5mm × 6mm<br>塑料封装 | 13-英寸<br>卷带 | 2500 | 卷带包装 |  |  |  |  |  |  |

Figure 1. Application Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. NexFET is a trademark of Texas Instruments.

## CSD43301Q5M

ZHCSAI6B-DECEMBER 2012-REVISED MAY 2013

TEXAS INSTRUMENTS

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

$T_A = 25^{\circ}C$  (unless otherwise noted)

|                                           |                                           | VA   | VALUE                 |      |  |

|-------------------------------------------|-------------------------------------------|------|-----------------------|------|--|

|                                           |                                           | MIN  | MAX                   | UNIT |  |

| DRAIN to PGN                              | IN, SD to P <sub>GND</sub> <sup>(2)</sup> |      | 12                    | V    |  |

| DRAIN to PGN                              | <sub>ID</sub> (10ns)                      | -7   | 14                    | V    |  |

| $V_{\text{DD}}$ to $P_{\text{GND}}$       |                                           | -0.3 | 8                     | V    |  |

| IN, SD to P <sub>GN</sub>                 | D <sup>(2)</sup>                          | -0.3 | V <sub>DD</sub> + 0.3 | V    |  |

| IN, SD to P <sub>GND</sub> <sup>(2)</sup> | Human Body Model (HBM)                    |      | 2000                  | V    |  |

| ESD Rating                                | Charged Device Model (CDM)                |      | 500                   | V    |  |

| Power Dissipa                             | ation (P <sub>D</sub> )                   |      | 12                    | W    |  |

| Operating Ter                             | nperature Range, (T <sub>J</sub> )        | -40  | 150                   | °C   |  |

| Storage Temp                              | perature Range, (T <sub>STG</sub> )       | -65  | 150                   | °C   |  |

(1) Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to Absolute Maximum rated conditions for extended periods may affect device reliability.

(2) Must not exceed 8V

## **RECOMMENDED OPERATING CONDITIONS**

$T_A = 25^{\circ}$  (unless otherwise noted)

| Parameter                                                  | Conditions | MIN | MAX  | UNIT |

|------------------------------------------------------------|------------|-----|------|------|

| Bias Voltage (V <sub>DD</sub> )                            |            | 4.5 | 6    | V    |

| Input Supply Voltage (V <sub>IN</sub> )                    |            |     | 9.6  | V    |

| Continuous Output Current (I <sub>OUT</sub> )              |            |     | 80   | А    |

| Peak Output Current, (I <sub>OUT-PK</sub> ) <sup>(1)</sup> |            |     | 120  | А    |

| Switching Frequency, (f <sub>SW</sub> )                    |            |     | 1500 | kHz  |

| Minimum IN Pulse Width                                     |            | 48  |      | ns   |

| Operating Temperature                                      |            | -40 | 125  | °C   |

(1) Peak Output Current is applied for  $t_p = 50\mu s$ .

#### THERMAL INFORMATION

$T_A = 25^{\circ}C$  (unless otherwise noted)

|                 | PARAMETER                                             | MIN | TYP | MAX | UNIT |

|-----------------|-------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta JC}$ | Thermal Resistance, Junction-to-Case (Top of package) |     |     | 20  | °C/W |

| $R_{\theta JB}$ | Thermal Resistance, Junction-to-Board <sup>(1)</sup>  |     |     | 2   | °C/W |

(1)  $R_{\theta JB}$  value based on hottest board temperature within 1mm of the package.

ELECTRICAL CHARACTERISTICS

$T_A = 25^{\circ}C$ ,  $V_{DD} = 5V$  (unless otherwise noted)

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|------|------|------|

| Device On Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |      |      |      |      |

| D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sub>D</sub> = 50A, , T <sub>J</sub> = 25°C                       |      | 0.55 | 0.70 | mΩ   |

| R <sub>on</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I <sub>D</sub> = 50A, T <sub>J</sub> = 125°C                        |      | 0.70 | 0.88 | mΩ   |

| V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                     |      |      |      |      |

| Standby Supply Current ( I <sub>DD</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $SD = V_{DD} = 5V$                                                  |      | 153  | 300  | μA   |

| Operating Supply Current (I <sub>DD</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SD = 0V,<br>IN = 50% Duty Cycle, f <sub>SW</sub> = 300kHz           |      | 29.5 |      | mA   |

| POWER-ON RESET AND UNDER VOLTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AGE LOCKOUT                                                         | ·    |      |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $T_A = 25^{\circ}C$                                                 | 3.9  | 4.2  | 4.5  | V    |

| tandby Supply Current (I <sub>DD</sub> )<br>perating Supply Current (I <sub>DD</sub> )<br><b>OWER-ON RESET AND UNDER VOLT</b><br>ower on Reset (V <sub>DD</sub> Rising)<br>VLO (V <sub>DD</sub> Falling)<br>ysteresis<br>I<br>I Logic Level High (V <sub>INH</sub> )<br>I Logic Level High (V <sub>INL</sub> )<br>I longic Level Low (V <sub>INL</sub> )<br>I nput Hysteresis<br>I to DRAIN Propagation Delay (t <sub>PDLH</sub> )<br>I to DRAIN Propagation Delay (t <sub>PDHL</sub> )<br>inimum Pulse Width Changes Output<br>D<br>D Logic Level High Threshold (V <sub>IH</sub> ) | $T_A = -40^{\circ}C$ to $140^{\circ}C$                              | 3.7  | 4.2  | 4.65 | V    |

| UVLO (V <sub>DD</sub> Falling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     | 3.45 | 3.9  | 4.35 | V    |

| Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     | 200  | 300  | 500  | mV   |

| IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      |      |      |      |

| IN Logic Level High (V <sub>INH</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     | 2.0  |      |      | V    |

| IN Logic Level Low (V <sub>INL</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |      |      | 0.8  | V    |

| IN Input Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |      | 0.8  |      | V    |

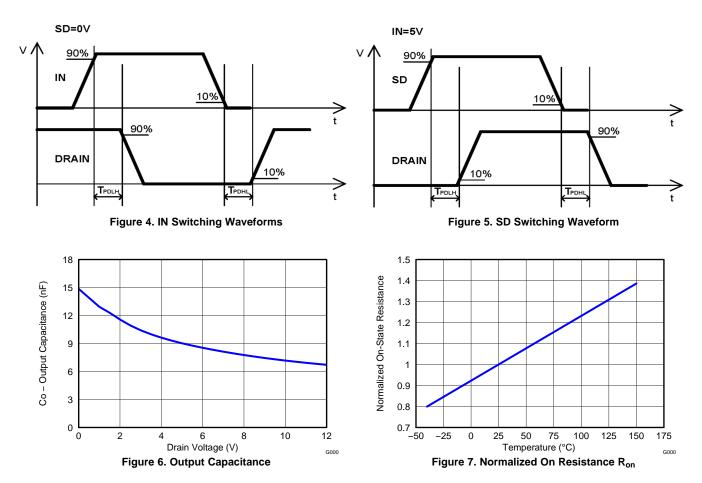

| IN to DRAIN Propagation Delay (t <sub>PDLH</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      | 32   |      | ns   |

| IN to DRAIN Propagation Delay (t <sub>PDHL</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{DD} = 5V, SD = 0, I_D = 25A$ (See Figure 4)                     |      | 80   |      | ns   |

| Minimum Pulse Width Changes Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      | 36   | 48   | ns   |

| SD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      |      |      |      |

| SD Logic Level High Threshold (V <sub>IH</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     | 2.0  |      |      | V    |

| SD Logic Level Low Threshold (VIL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      |      | 0.8  | V    |

| Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |      | 0.8  |      | V    |

| SD to DRAIN Propagation Delay (t <sub>PDLH</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      | 80   |      | ns   |

| SD to DRAIN Propagation Delay (t <sub>PDHL</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{DD} = 5V$ , IN = $V_{DD}$ , I <sub>D</sub> = 25A (See Figure 5) |      | 32   |      | ns   |

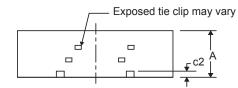

| Dynamic Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |      |      |      |      |

| Output Capacitance (C <sub>O</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | N/ 6N/                                                              |      | 10   | 13   | nF   |

| Output Charge (Q <sub>O</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>DRAIN</sub> = 6V                                             |      | 54   |      | nC   |

| Body Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     | · ·  |      |      |      |

| Forward Voltage (V <sub>F</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sub>D</sub> = 40A                                                |      | 0.75 | 0.85 | V    |

| Reverse Recovery Charge (Q <sub>RR</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |      | 161  |      | nC   |

| Reverse Recovery Time Delay (t <sub>RR</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $I_{D} = 40A, V_{DRAIN} = 6V, di/dt = 150A/\mu s$                   |      | 72   |      | ns   |

TEXAS INSTRUMENTS

www.ti.com.cn

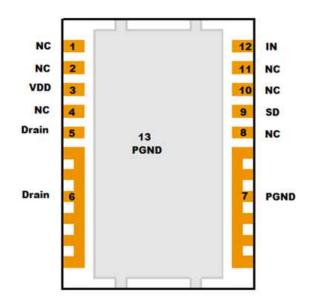

**PIN CONFIGURATION**

Figure 2. Pin Configuration

#### **PIN DESCRIPTION**

| PIN                |                  | DESCRIPTION                                                                                                                                        |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                | NAME             | DESCRIPTION                                                                                                                                        |

| 1,2,4, 8,<br>10,11 | NC               | No connect. These should not be used for any electrical connection. These pins should not be connected to each other. Connect to dead copper only. |

| 3                  | V <sub>DD</sub>  | Supply Voltage for IC                                                                                                                              |

| 5,6                | DRAIN            | Drain terminal of internal MOSFET                                                                                                                  |

| 7                  | P <sub>GND</sub> | Power Ground and source terminal of the internal MOSFET. Needs to be connected to Pin 13 on PCB                                                    |

| 9                  | SD               | Shut Down Pin: Logic High disables the Device                                                                                                      |

| 12                 | IN               | Input for Gate Driver                                                                                                                              |

| 13                 | P <sub>GND</sub> | Power Ground and source terminal of the internal MOSFET. Needs to be connected to Pin 7 on PCB                                                     |

CSD43301Q5M ZHCSAI6B – DECEMBER 2012 – REVISED MAY 2013

www.ti.com.cn

### **TYPICAL DEVICE CHARACTERISTICS**

CSD43301Q5M ZHCSAI6B-DECEMBER 2012-REVISED MAY 2013

0.8 40 T<sub>C</sub> = 25°C T<sub>C</sub> = 125°C  $V_{IN} = 6V$ 38 - On-State Resistance (m0) - 0.7 - 0.6 - 0.5 - 0.5  $f_{SW} = 300 \text{kHz}$ 36 I<sub>DD</sub> - Supply Current (mA) 34 32 30 28 26 24 ط<sup>ة</sup> 0.45 22 0.4 **L** 4.5 20 4.8 5.1 5.4 5.7 4.4 4.6 4.8 5 5.4 5.6 5.8 6 6 5.2 6.2  $V_{\text{DD}}$  - Supply Voltage  $\,$  (V) V<sub>DD</sub> - Supply Voltage (V) G000 G000 Figure 8. On Resistance vs. Supply Voltage Figure 9. Supply Current vs. Supply Voltage 160 V<sub>DRAIN</sub> =0V 140  $V_{DD} = 5V$ I<sub>DD</sub> - Supply Current (mA) 120 100 80 60 40 20 0 ∟ 200

400

600

800

f<sub>SW</sub> - Switching Frequency (kHz)

Figure 10. Supply Current vs. Switching Frequency

1000

1200

1400

1600

G000

www.ti.com.cn

#### **Application Information**

### V<sub>DD</sub> and Under-Voltage Lockout (UVLO)

The driver IC in the CSD43301Q5M has an internal UVLO protection feature on the  $V_{DD}$  pin. Whenever the driver is in the UVLO condition (i.e. when  $V_{DD}$  voltage is less than  $V_{ON}$  during power up and when  $V_{DD}$  voltage is less than  $V_{OFF}$  during power down), this circuit holds the gate of the integrated MOSFET LOW, regardless of the status of IN and SD. The UVLO is typically 4.2V with 300-mV typical hysteresis. This hysteresis helps prevent chatter when low  $V_{DD}$  supply voltages have noise from the power supply and also when there are droops in the  $V_{DD}$  bias voltage when the system commences switching and there is a sudden increase in  $I_{DD}$ . This provides the capability to operate at low voltage levels (below 5V), along with best-in-class switching characteristics. For example, at power up, the MOSFET remains OFF until the  $V_{DD}$  voltages reaches the UVLO threshold. This prevents operating the MOSFET in the linear region and conducting a large load current at the same time, which often results in device overheating and can potentially damage the device.

Since the driver draws current from the V<sub>DD</sub> pin to bias all internal circuits, for the best high-speed circuit performance, Multi-Layer Ceramic Capacitor (MLCC) bypass capacitors are recommended to prevent noise problems. A 1  $\mu$ F MLCC type capacitor should be located as close as possible to the V<sub>DD</sub> to GND pins of the gate driver.

#### **Operating Supply Current**

The driver IC in the CSD43301Q5M has a low quiescent current in normal operation.  $I_{DDQ}$  is less than 0.2 mA when the device is disabled (SD = 0). The operating current vs. supply voltage is shown in Figure 9, and the operating current vs. frequency is shown in Figure 10.

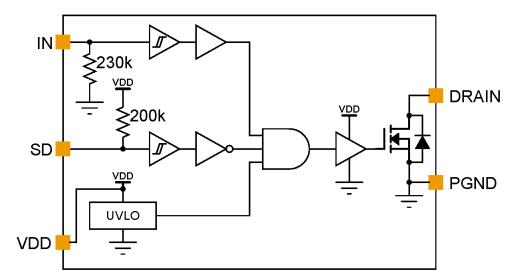

#### Input Stage

The input pins (IN and SD) of the CSD43301Q5M are based on a TTL/CMOS compatible input threshold logic that is independent of the  $V_{DD}$  supply voltage. With a typical high threshold of 2.2 V and a typical low threshold of 1.2 V, the logic level thresholds can be conveniently driven with PWM control signals derived from 3.3-V or 5-V digital power controllers. Wider hysteresis (typical of 0.8 V) offers enhanced noise immunity compared to traditional TTL logic implementations, where the hysteresis is typically less than 0.5 V. These devices also feature tight control of the input pin threshold voltage levels which eases system design considerations and ensures stable operation across temperature. The very low input capacitance on these pins reduces loading and increases switching speed. The device features an important safety function wherein, whenever any of the input pins are in a floating condition, the output of the respective channel is held in the low state. This is achieved using a  $V_{DD}$  pull-up resistor on the SD input or a GND pull-down resistor on the IN input. This can be seen in the block diagram in Figure 3.

#### **Power Dissipation**

Power Dissipation of the CSD43301Q5M used in secondary rectification is given by the following:

| $P_{LOSS} = P_{DRV} + P_{COND} + P_{SW}$  | (1) |

|-------------------------------------------|-----|

| where driver loss is given by             |     |

| $P_{DRV} = V_{DD} \times I_{DD}$          | (2) |

| and conduction loss is given by           |     |

| $P_{COND} = I_{D_{LRMS}}^2 \times R_{ON}$ | (3) |

Switching losses consist of body diode conduction losses during dead time, body diode reverse recovery losses, and output charge losses, given by the following:

$$P_{SW} = I_D \times V_F \times (DT_R + DT_F) \times F_{SW} + Q_{RR} \times V_{DRAIN} \times F_{SW} + \frac{1}{2}Q_{OSS} \times V_{DRAIN} \times F_{SW}$$

(4)

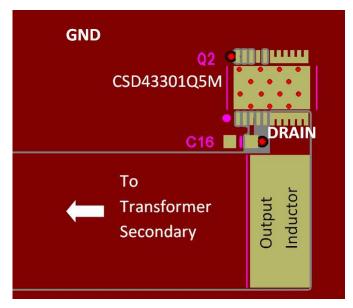

#### **Recommended PCB Design Overview**

The CSD43301Q5M features extremely low nominal  $R_{ON}$ . In order to maximize the performance of this device, some simple layout guidelines should be followed.

- The DRAIN pins of the CSD43301Q5M should be placed as close as possible to the inductor and connected with a short wide trace. This reduces PCB conduction losses and reduce switching noise level. <sup>(1)</sup>

- The GND pin (pin 7) must be connected into the thermal pad (pin 13) on the bottom of the device via a copper pour (without thermal spokes) for maximum performance.

- The CSD43301Q5M has the ability to use the GND planes as the primary thermal path. As such, the use of thermal vias is an effective way to pull away heat from the device and into the system board. Concerns of solder voids and manufacturability problems can be addressed by the use of three basic tactics to minimize the amount of solder attach that will wick down via the barrel:

- Intentionally space out the vias from each other to avoid a cluster of holes in a given area.

- Use the smallest drill size allowed in your design. The example in Figure 11 uses vias with a 10 mil drill hole and a 16 mil capture pad.

- Tent the opposite side of the via with a solder mask.

In the end, the number and size of the thermal vias should align with the end user's PCB design rules and manufacturing types.

Figure 11. Recommended PCB Layout (Top Down View)

(1) Keong W. Kam, David Pommerenke, "EMI Analysis Methods for Synchronous Buck Converter EMI Root Cause Analysis", University of Missouri – Rolla

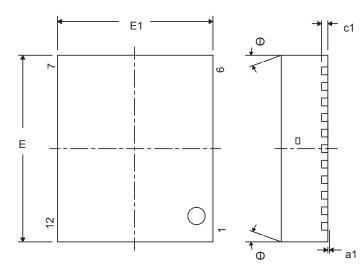

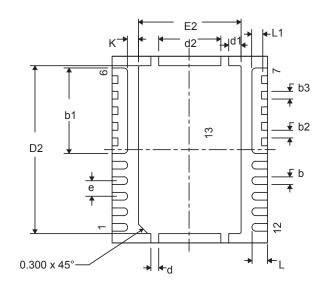

#### **MECHANICAL DATA**

TOP VIEW

SIDE VIEW

#### BOTTOM VIEW

| DIM |       | MILLIMETERS |       |       | INCHES    |       |  |  |  |  |

|-----|-------|-------------|-------|-------|-----------|-------|--|--|--|--|

| DIM | Min   | Nom         | Max   | Min   | Nom       | Max   |  |  |  |  |

| А   | 1.400 | 1.450       | 1.500 | 0.055 | 0.057     | 0.059 |  |  |  |  |

| A1  | 0.000 | 0.000       | 0.050 | 0.000 | 0.000     | 0.002 |  |  |  |  |

| b   | 0.200 | 0.250       | 0.350 | 0.008 | 0.010     | 0.013 |  |  |  |  |

| b1  |       | 2.750 TYP   |       |       | 0.108 TYP |       |  |  |  |  |

| b2  | 0.200 | 0.250       | 0.320 | 0.008 | 0.010     | 0.013 |  |  |  |  |

| b3  |       | 0.250 TYP   |       |       | 0.010 TYP |       |  |  |  |  |

| c1  | 0.150 | 0.200       | 0.250 | 0.006 | 0.008     | 0.010 |  |  |  |  |

| c2  | 0.150 | 0.200       | 0.250 | 0.006 | 0.008     | 0.010 |  |  |  |  |

| D2  | 5.300 | 5.400       | 5.500 | 0.209 | 0.213     | 0.217 |  |  |  |  |

| d   | 0.200 | 0.250       | 0.300 | 0.008 | 0.010     | 0.012 |  |  |  |  |

| d1  | 0.350 | 0.400       | 0.450 | 0.014 | 0.016     | 0.018 |  |  |  |  |

| d2  | 1.900 | 2.000       | 2.100 | 0.075 | 0.079     | 0.083 |  |  |  |  |

| Е   | 5.900 | 6.000       | 6.100 | 0.232 | 0.236     | 0.240 |  |  |  |  |

| E1  | 4.900 | 5.000       | 5.100 | 0.193 | 0.197     | 0.201 |  |  |  |  |

| E2  | 3.200 | 3.300       | 3.400 | 0.126 | 0.130     | 0.134 |  |  |  |  |

| е   |       | 0.500 TYP   |       |       | 0.020 TYP |       |  |  |  |  |

| K   |       | 0.350 TYP   |       |       | 0.014 TYP |       |  |  |  |  |

| L   | 0.400 | 0.500       | 0.600 | 0.016 | 0.020     | 0.024 |  |  |  |  |

| L1  | 0.210 | 0.310       | 0.410 | 0.008 | 0.012     | 0.016 |  |  |  |  |

| θ   | 0.00  | _           | _     | 0.00  | _         | _     |  |  |  |  |

## CSD43301Q5M

ZHCSAI6B-DECEMBER 2012-REVISED MAY 2013

www.ti.com.cn

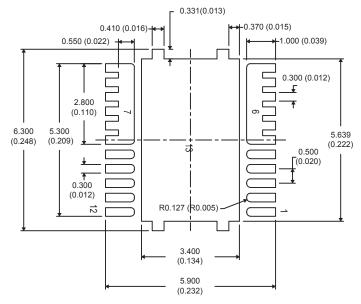

### **Recommended PCB Pattern**

NOTE: Dimensions are in mm (inches).

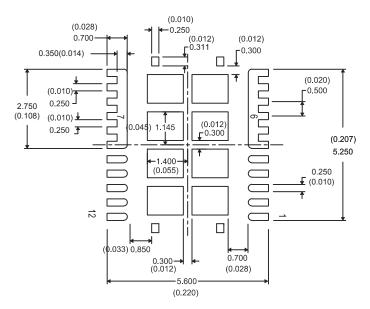

#### **Recommended Stencil**

NOTE: Dimensions are in mm (inches).

## **REVISION HISTORY**

| Cł | hanges from Original (December 2012) to Revision A                                   | Page |  |  |  |  |  |  |  |  |  |

|----|--------------------------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|--|

| •  | Changed Figure 3                                                                     |      |  |  |  |  |  |  |  |  |  |

| Cł | hanges from Revision A (December 2012) to Revision B                                 | Page |  |  |  |  |  |  |  |  |  |

| •  | Changed the MECHANICAL DATA image and corresponding table                            |      |  |  |  |  |  |  |  |  |  |

| •  | Changed the Recommended PCB Pattern - lead width From: 0.300(0.012) To: 0.350(0.014) | 10   |  |  |  |  |  |  |  |  |  |

| •  | Changed the Recommended Stencil image                                                | 10   |  |  |  |  |  |  |  |  |  |

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)        | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|------------------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| CSD43301Q5M      | ACTIVE        | LSON-CLIP    | DQP                | 12   | 2500           | RoHS-Exempt<br>& Green | (6)<br>NIPDAU                 | Level-2-260C-1 YEAR  | -55 to 125   | 43301M                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

www.ti.com

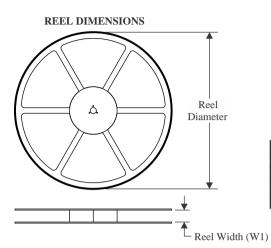

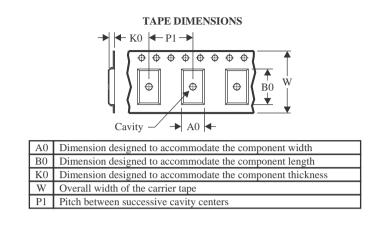

## TAPE AND REEL INFORMATION

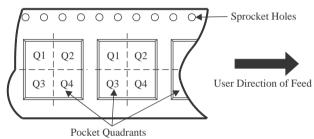

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions | are | nominal |

|-----------------|-----|---------|

|-----------------|-----|---------|

| Device      | 0             | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|---------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CSD43301Q5M | LSON-<br>CLIP | DQP                | 12 | 2500 | 330.0                    | 12.4                     | 5.3        | 6.3        | 1.8        | 8.0        | 12.0      | Q1               |

www.ti.com

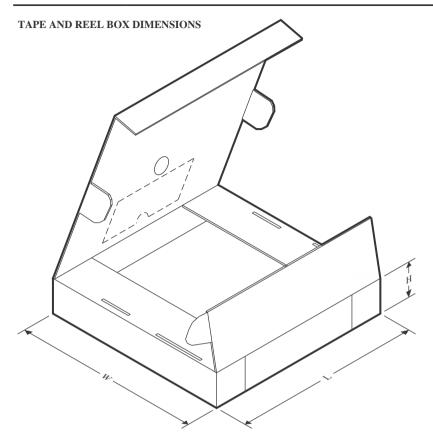

# PACKAGE MATERIALS INFORMATION

3-Jun-2023

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CSD43301Q5M | LSON-CLIP    | DQP             | 12   | 2500 | 346.0       | 346.0      | 33.0        |

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司