🕳 Order

Now

Support & Community

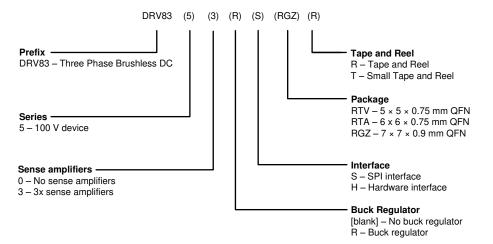

#### DRV8350, DRV8350R DRV8353, DRV8353R

ZHCSIN3A-AUGUST 2018-REVISED JUNE 2019

# DRV835x 100V 三相智能栅极驱动器

- 1 特性

- 9V 至 100V 三半桥栅极驱动器

- 可选的集成降压稳压器

- 可选的三个低侧电流分流放大器

- 智能栅极驱动架构

Texas

INSTRUMENTS

- 可调转换率控制,可实现优异的 EMI 性能

- V<sub>GS</sub> 握手和最小死区时间插入,可避免发生击穿

- 50mA 至 1A 峰值拉电流

- 100mA 至 2A 峰值灌电流

- 通过强下拉能力减小 dV/dt

- 集成栅极驱动器电源

- 高侧倍增电荷泵可实现 100% PWM 占空比控制

- 低侧线性稳压器

- 集成 LM5008A 降压稳压器

- 6V 至 95V 工作电压范围

- 2.5V 至 75V、350mA 输出能力

- 集成三个电流分流放大器

- 可调增益(5、10、20、40 V/V)

- 双向或单向支持

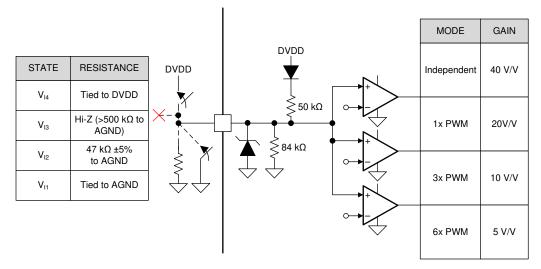

- 6x、3x、1x 和独立 PWM 模式

- 支持 120° 有传感器运行

- 提供 SPI 或硬件接口

- 低功耗睡眠模式(V<sub>VM</sub> = 48V 时为 20µA)

- 集成式保护 特性

- VM 欠压锁定 (UVLO)

- 栅极驱动电源欠压 (GDUV)

- MOSFET V<sub>DS</sub> 过流保护 (OCP)

- MOSFET 击穿保护

- 栅极驱动器故障 (GDF)

- 热警告和热关断 (OTW/OTSD)

- 故障状态指示器 (nFAULT)

# 2 应用

- 三相无刷直流 (BLDC) 电机模块

- 风扇、风机和泵

- 电动自行车、电动踏板车和电动汽车

- 电动和园艺工具、割草机

- 无人机、机器人和遥控玩具

- 工厂自动化和纺织机

# 3 说明

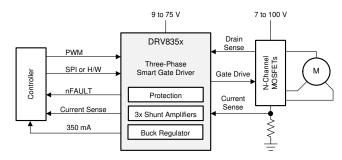

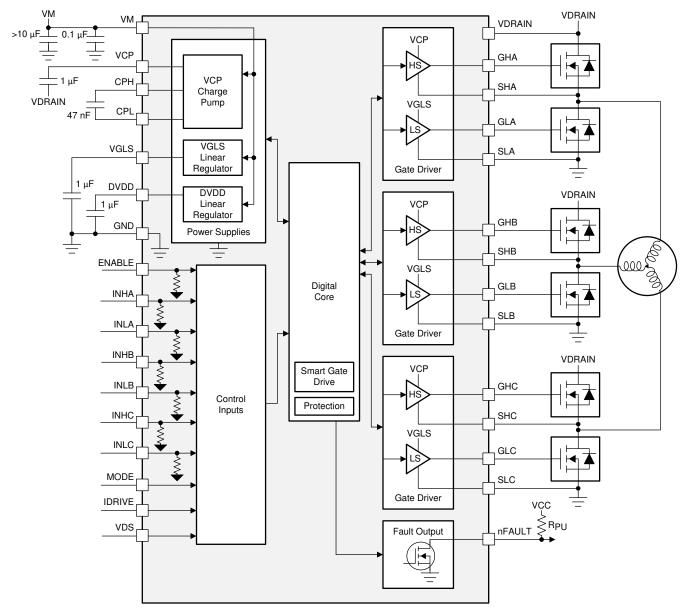

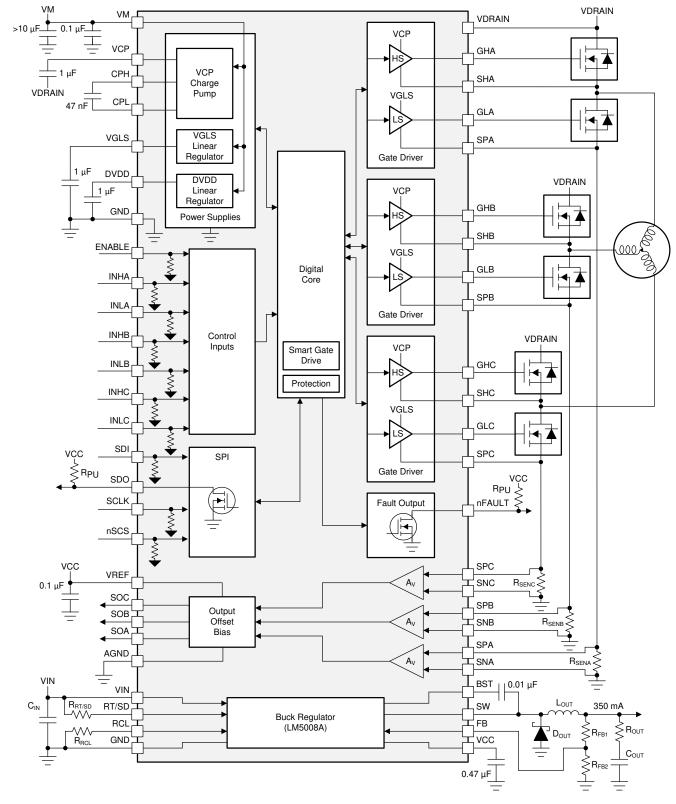

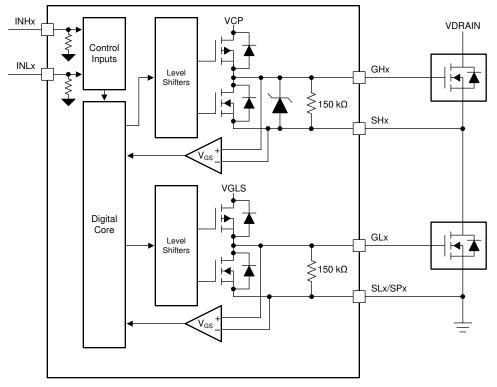

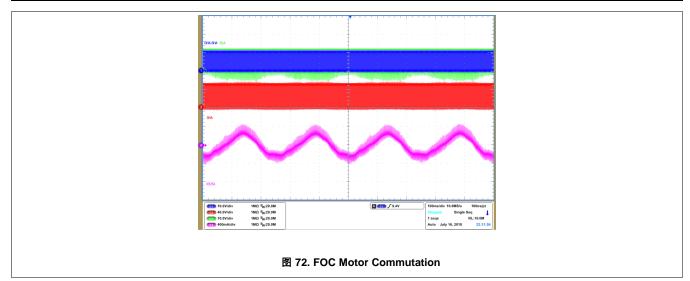

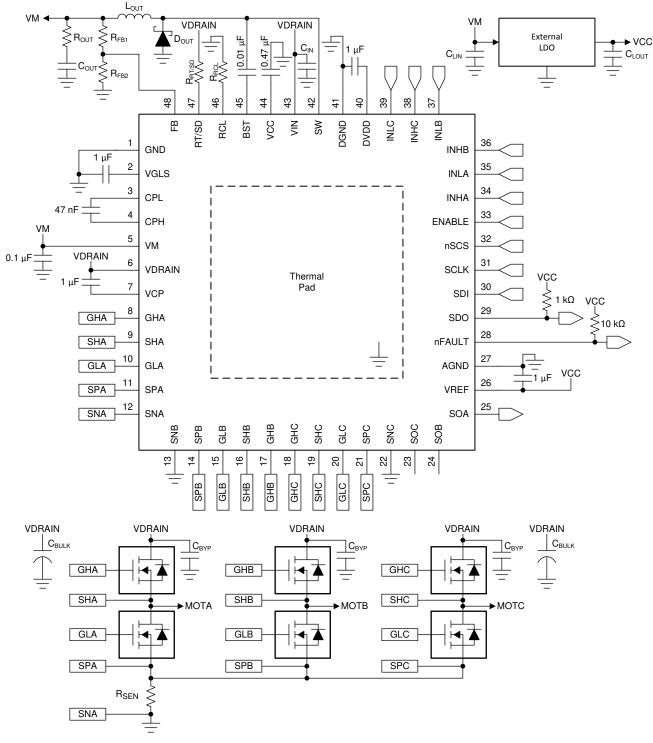

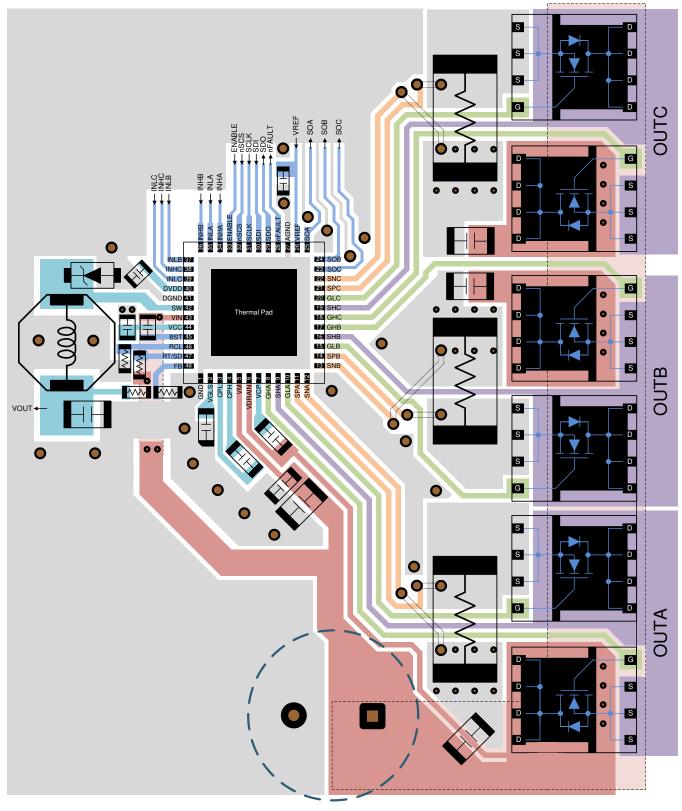

DRV835x 系列器件均为高度集成的栅极驱动器,适用 于三相无刷直流 (BLDC) 电机 应用标准。这些 应用 包 括 BLDC 电机的场定向控制 (FOC)、正弦电流控制和 梯形电流控制。该器件型号提供了可选的集成式分流放 大器以支持不同的电机控制方案,还提供了降压稳压 器,以为栅极驱动器或外部控制器供电。

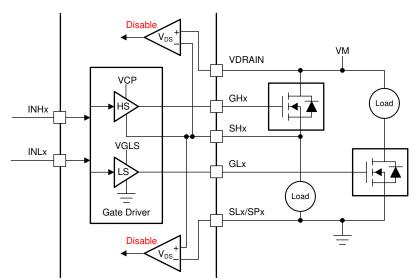

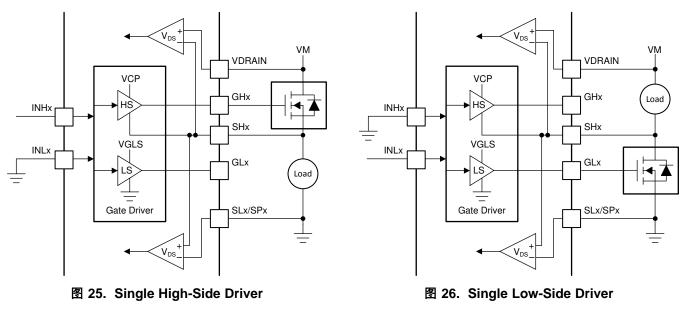

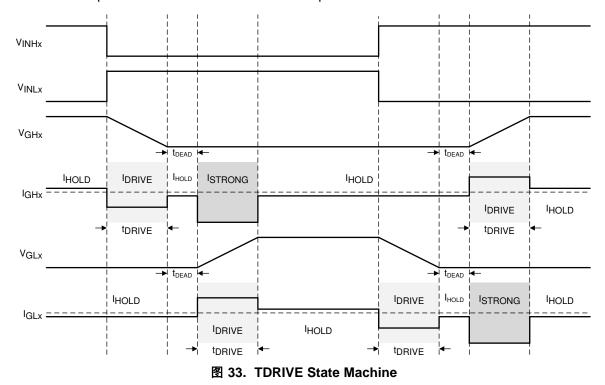

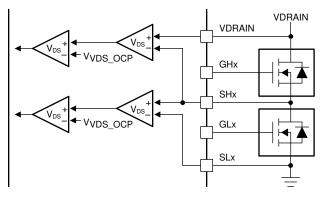

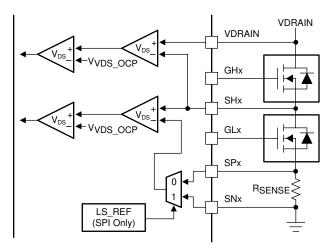

DRV835x 通过采用智能栅极驱动 (SGD) 架构减少了 MOSFET 压摆率控制和保护电路通常所需要的外部组 件数量。SGD 架构还可优化死区时间以防止击穿问 题,在通过 MOSFET 压摆率控制技术降低电磁干扰 (EMI) 方面带来了灵活性,并可通过 V<sub>GS</sub> 监控器防止 栅极短路问题。强大的栅极下拉电路有助于防止不必要 的 dV/dt 寄生栅极开启事件。

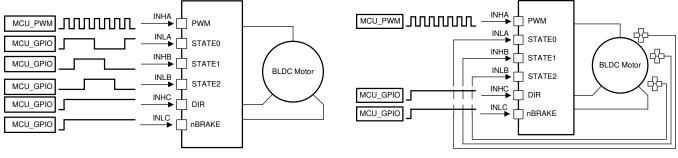

该系列器件支持各种 PWM 控制模式(6x、3x、1x 和 独立模式),可简化与外部控制器的连接。这些模式可 减少电机驱动器 PWM 控制信号所需的控制器输出数 量。该系列器件还包括 1x PWM 模式,因此可通过内 部阻塞换向表轻松对 BLDC 电机进行传感器式梯形控 制。

### 器件信息<sup>(1)</sup>

| 器件型号     | 封装        | 封装尺寸(标称值)       |  |  |  |  |

|----------|-----------|-----------------|--|--|--|--|

| DRV8350  | WQFN (32) | 5.00mm × 5.00mm |  |  |  |  |

| DRV8350R | VQFN (48) | 7.00mm × 7.00mm |  |  |  |  |

| DRV8353  | WQFN (40) | 6.00mm × 6.00mm |  |  |  |  |

| DRV8353R | VQFN (48) | 7.00mm × 7.00mm |  |  |  |  |

|          |           |                 |  |  |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

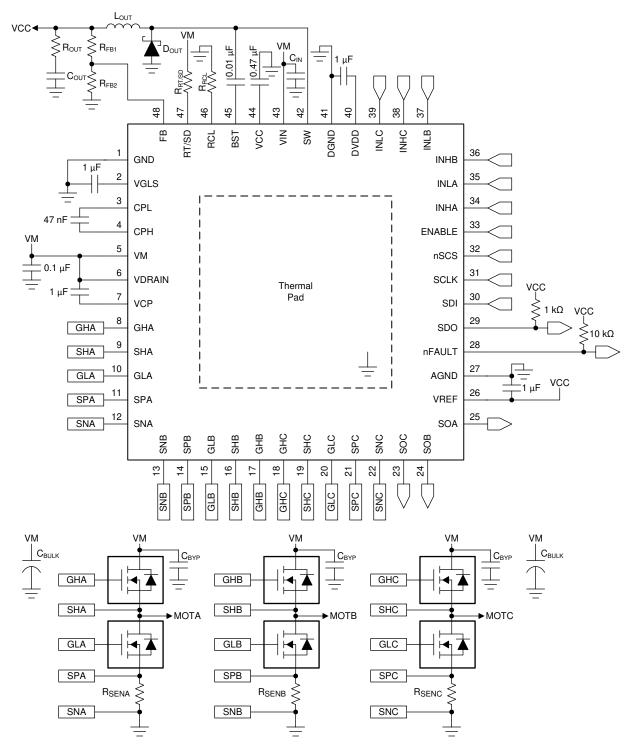

## 简化原理图

# DRV8350, DRV8350R DRV8353, DRV8353R

ZHCSIN3A-AUGUST 2018-REVISED JUNE 2019

# 目录

| 1 | 特性   |                                     |

|---|------|-------------------------------------|

| 2 | 应用   | 1                                   |

| 3 | 说明   | 1                                   |

| 4 | 修订   | 历史记录                                |

| 5 | Dev  | ice Comparison Table 3              |

| 6 | Pin  | Configuration and Functions 3       |

| 7 | Spe  | cifications10                       |

|   | 7.1  | Absolute Maximum Ratings 10         |

|   | 7.2  | ESD Ratings 11                      |

|   | 7.3  | Recommended Operating Conditions 11 |

|   | 7.4  | Thermal Information 11              |

|   | 7.5  | Electrical Characteristics 12       |

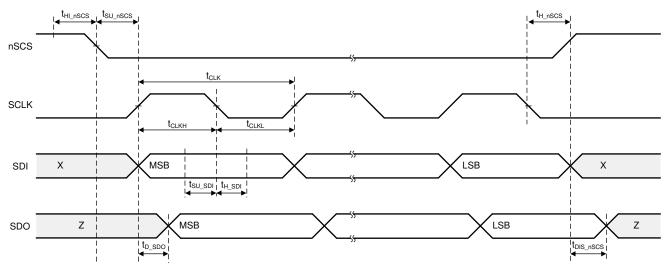

|   | 7.6  | SPI Timing Requirements 18          |

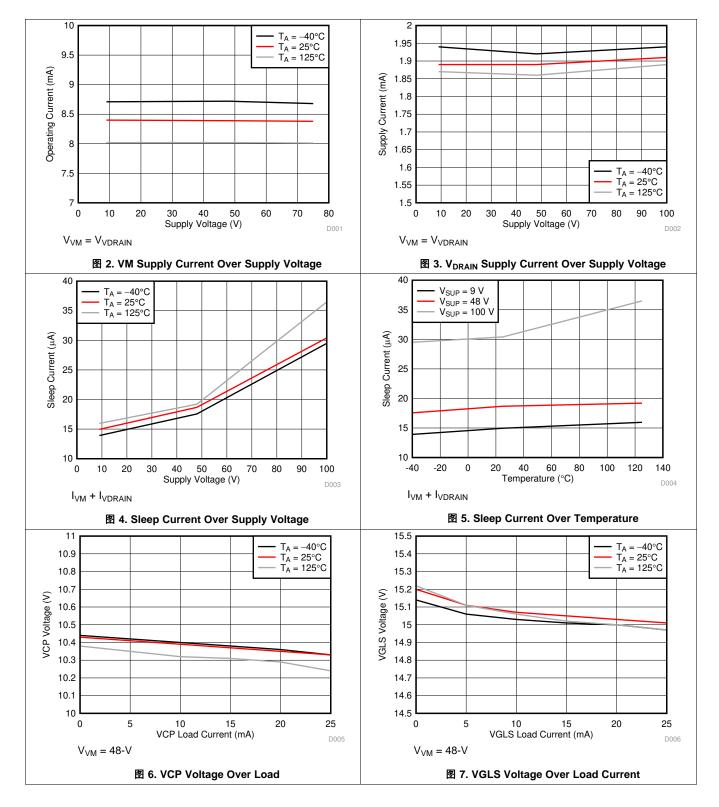

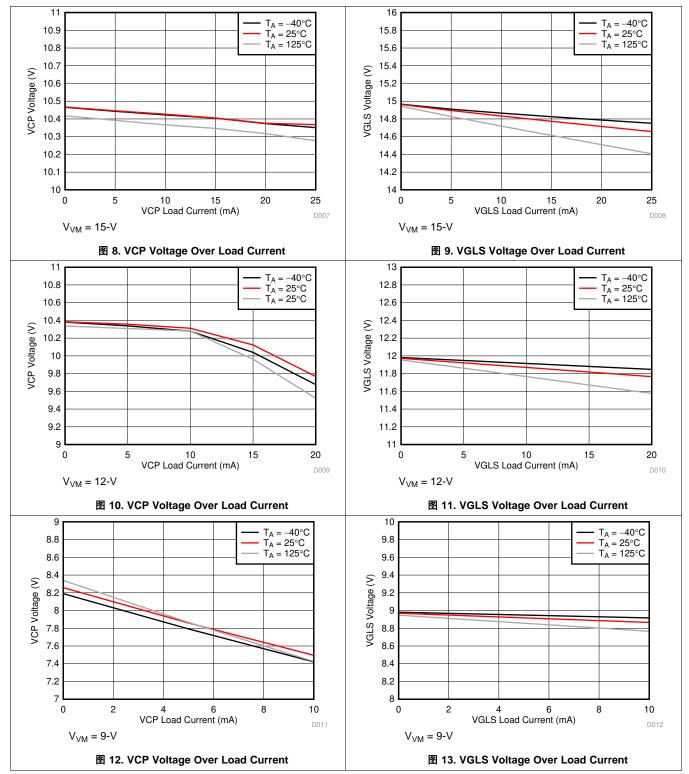

|   | 7.7  | Typical Characteristics 19          |

| 8 | Deta | ailed Description 21                |

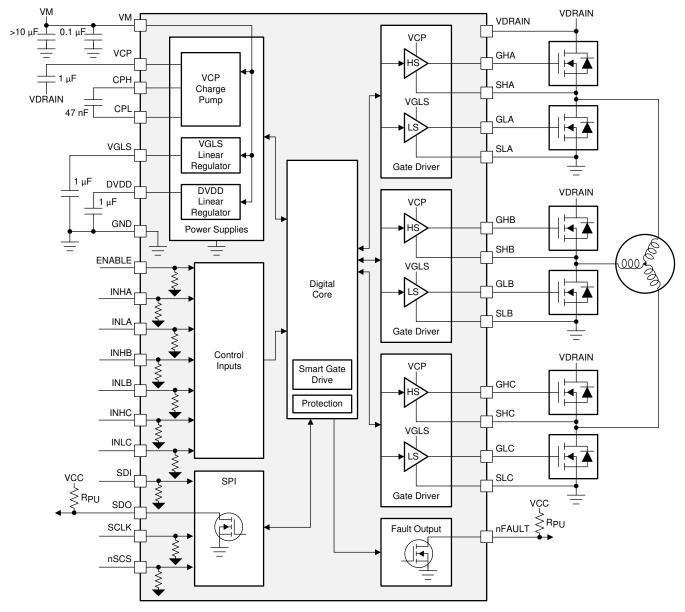

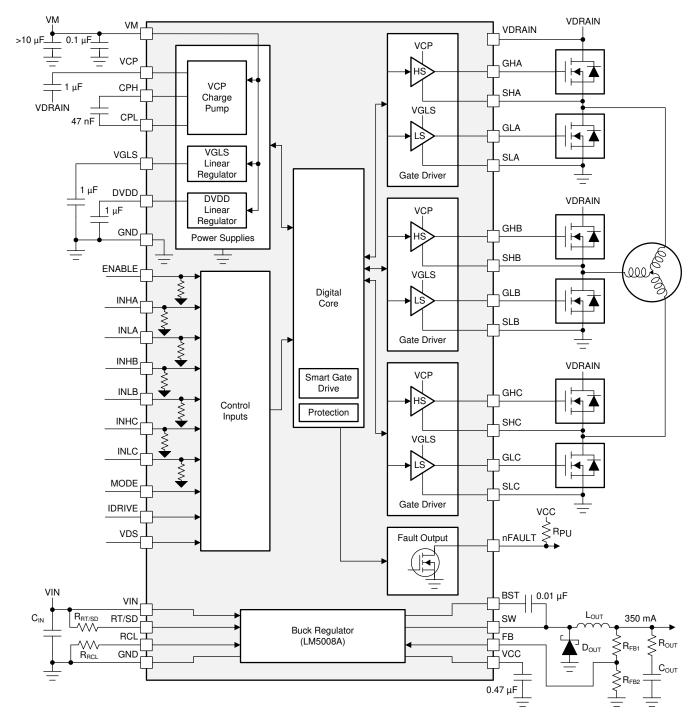

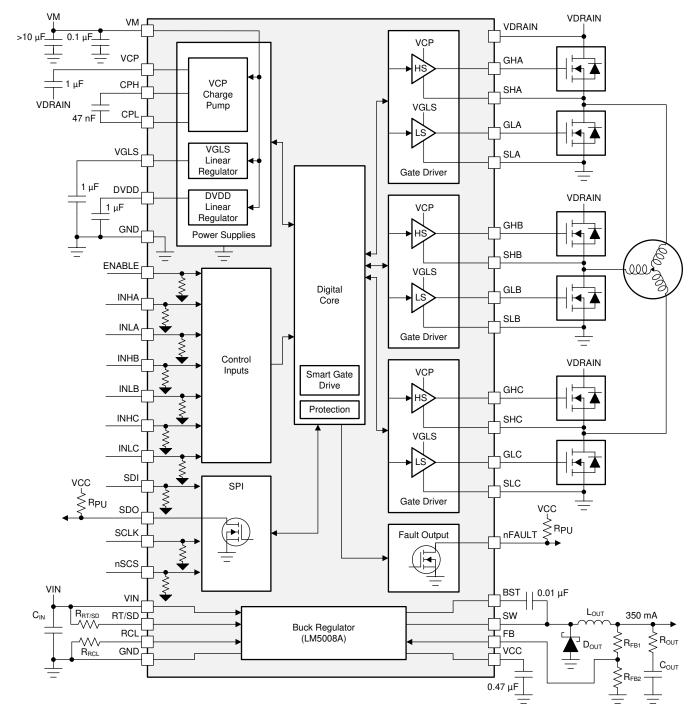

|   | 8.1  | Overview 21                         |

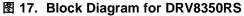

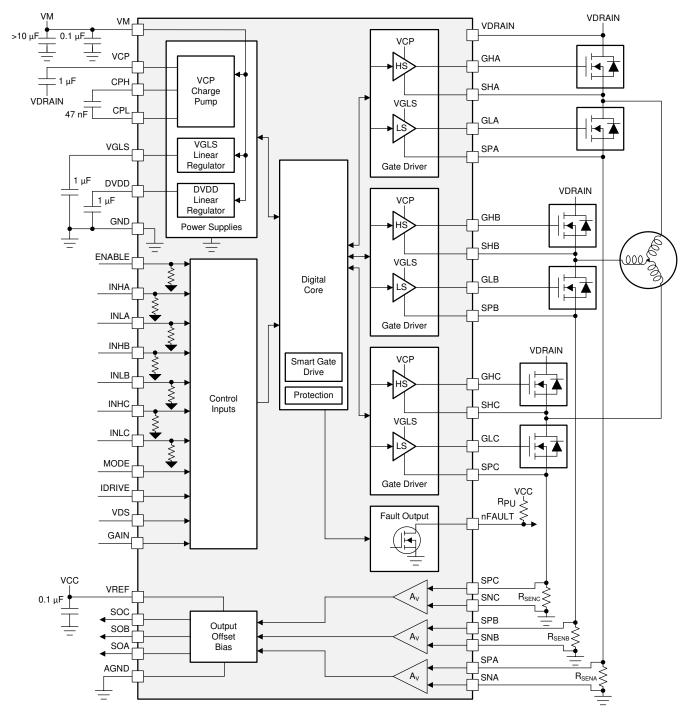

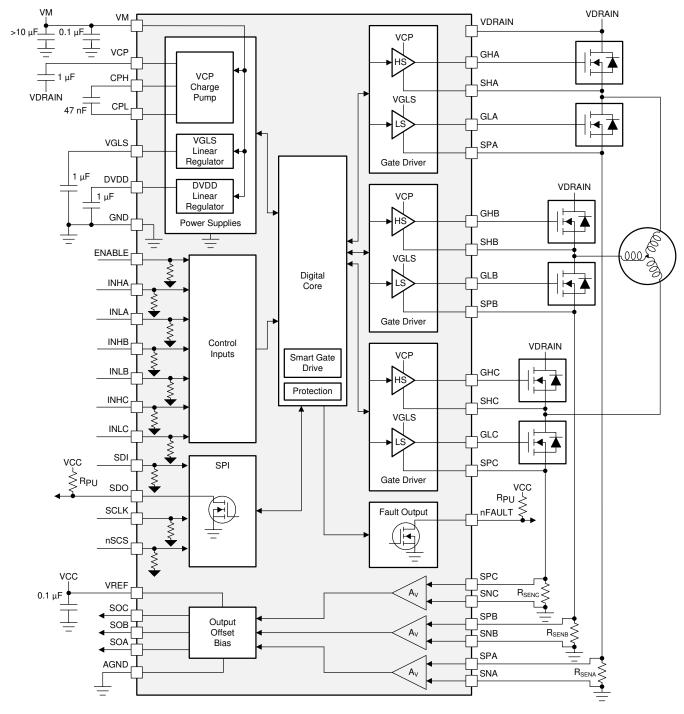

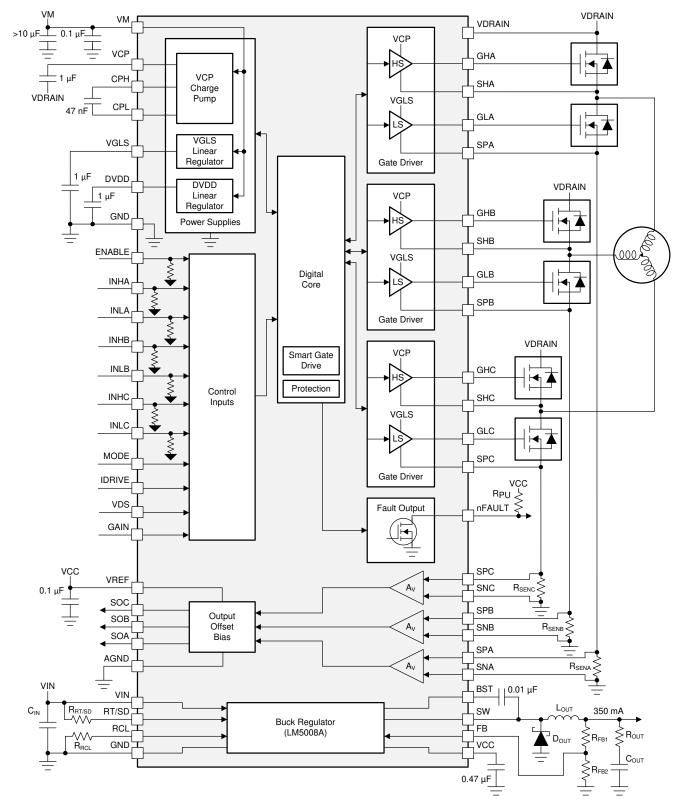

|   | 8.2  | Functional Block Diagram 22         |

|   | 8.3  | Feature Description 30              |

|   | 8.4  | Device Functional Modes 53          |

|   | 8.5  | Programming 54                      |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

Changes from Original (Assessed 2040) to Devision A

|   | ranges from Original (August 2016) to Revision A Page |  |   |  |  |  |  |  |  |  |

|---|-------------------------------------------------------|--|---|--|--|--|--|--|--|--|

| • | 己更改 将文档状态更改为生产数据                                      |  | 1 |  |  |  |  |  |  |  |

| • | 己删除 从 DRV8350 和 DRV8353 器件中删除了仅供预览的标注                 |  | 1 |  |  |  |  |  |  |  |

#### 8.6 Register Maps ..... 56 9 10.1 Bulk Capacitance Sizing ...... 77 11 11.2 Layout Example ...... 79 12 器件和文档支持 ...... 80 12.1 器件支持...... 80 12.2 12.3 12.4 接收文档更新通知 ...... 81 12.7

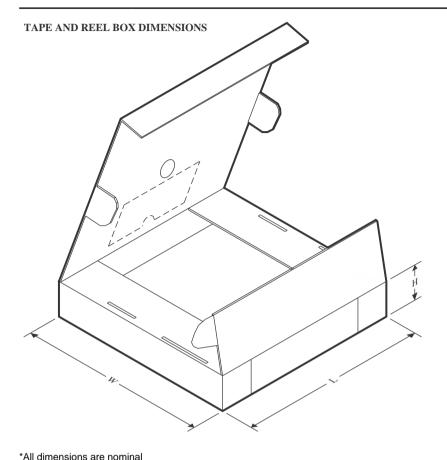

机械、封装和可订购信息......81 13

EXAS

# 5 Device Comparison Table

| DEVICE   | VARIANT   | SHUNT AMPLIFIERS | BUCK REGULATOR | INTERFACE    |

|----------|-----------|------------------|----------------|--------------|

| DRV8350  | DRV8350H  |                  | None           | Hardware (H) |

| DK V6350 | DRV8350S  | 0                | None           | SPI (S)      |

|          | DRV8350RH | 0                | 250 m (D)      | Hardware (H) |

| DRV8350R | DRV8350RS |                  | 350 mA (R)     | SPI (S)      |

| DD\/0252 | DRV8353H  |                  | Nees           | Hardware (H) |

| DRV8353  | DRV8353S  | 2                | None           | SPI (S)      |

|          | DRV8353RH | 3                | 250 m (D)      | Hardware (H) |

| DRV8353R | DRV8353RS |                  | 350 mA (R)     | SPI (S)      |

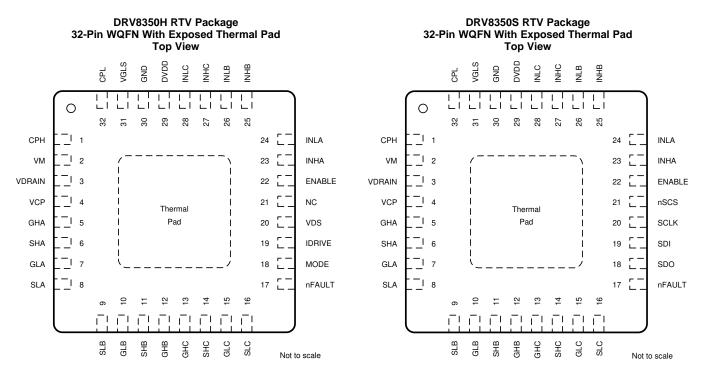

# 6 Pin Configuration and Functions

### Pin Functions—32-Pin DRV8350 Devices

|        | PIN      |          |                     |                                                                                                                                                                     |

|--------|----------|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | N        | 0.       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                         |

| NAWE   | DRV8350H | DRV8350S | 1                   |                                                                                                                                                                     |

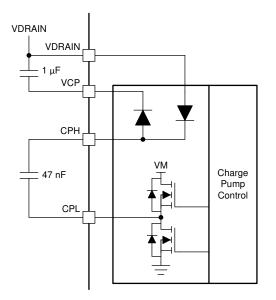

| СРН    | 1        | 1        | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                               |

| CPL    | 32       | 32       | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                               |

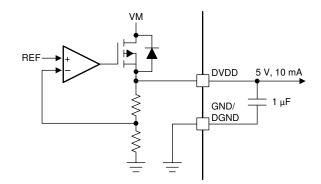

| DVDD   | 29       | 29       | PWR                 | 5-V internal regulator output. Connect a X5R or X7R, 1-µF, 6.3-V ceramic capacitor between the DVDD and GND pins. This regulator can source up to 10 mA externally. |

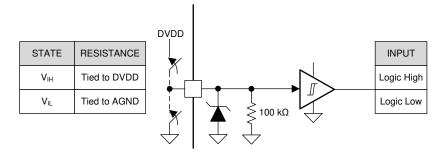

| ENABLE | 22       | 22       | I                   | Gate driver enable. When this pin is logic low the device goes to a low power sleep mode. An 8 to 40-µs pulse can be used to reset fault conditions.                |

| GHA    | 5        | 5        | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                    |

| GHB    | 12       | 12       | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                    |

| GHC    | 13       | 13       | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                    |

| GLA    | 7        | 7        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                      |

| GLB    | 10       | 10       | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                      |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain

### TEXAS INSTRUMENTS

www.ti.com.cn

## Pin Functions—32-Pin DRV8350 Devices (continued)

| PIN    |          |          |                     |                                                                                                                                                                                                                                   |

|--------|----------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.      |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                       |

| NAME   | DRV8350H | DRV8350S |                     |                                                                                                                                                                                                                                   |

| GLC    | 15       | 15       | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                    |

| GND    | 30       | 30       | PWR                 | Device primary ground. Connect to system ground.                                                                                                                                                                                  |

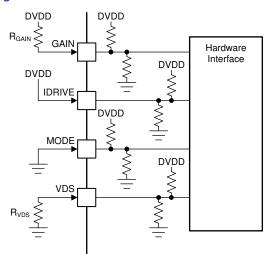

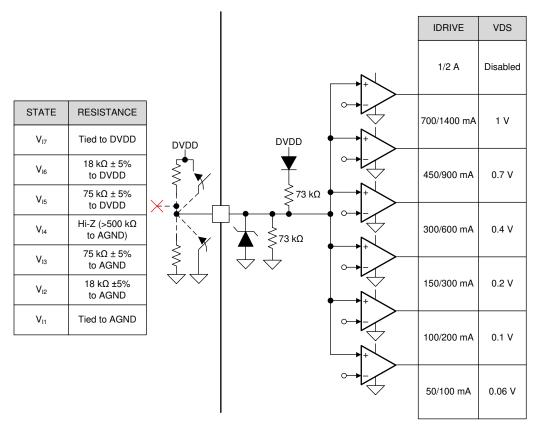

| IDRIVE | 19       | —        | I                   | Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                                   |

| INHA   | 23       | 23       | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                                   |

| INHB   | 25       | 25       | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                                   |

| INHC   | 27       | 27       | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                                   |

| INLA   | 24       | 24       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                                     |

| INLB   | 26       | 26       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                                     |

| INLC   | 28       | 28       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                                     |

| MODE   | 18       | _        | I                   | PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                                                                              |

| NC     | 21       | _        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                                              |

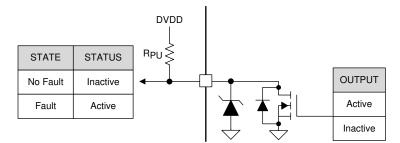

| nFAULT | 17       | 17       | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                                                                           |

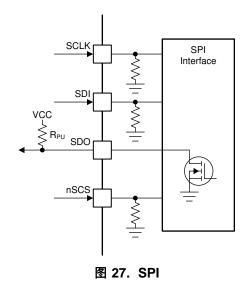

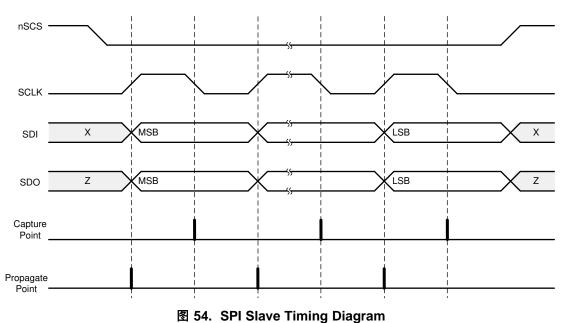

| nSCS   | _        | 21       | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                               |

| SCLK   | _        | 20       | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                                             |

| SDI    | _        | 19       | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                                          |

| SDO    | _        | 18       | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                                        |

| SHA    | 6        | 6        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SHB    | 11       | 11       | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SHC    | 14       | 14       | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SLA    | 8        | 8        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                                         |

| SLB    | 9        | 9        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                                         |

| SLC    | 16       | 16       | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                                         |

| VCP    | 4        | 4        | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VCP and VDRAIN pins.                                                                                                                           |

| VDRAIN | 3        | 3        | I                   | High-side MOSFET drain sense input and charge pump reference. Connect to the common point of the MOSFET drains.                                                                                                                   |

| VDS    | 20       | _        | I                   | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                                      |

| VGLS   | 31       | 31       | PWR                 | 11-V internal regulator output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VGLS and GND pins.                                                                                                                 |

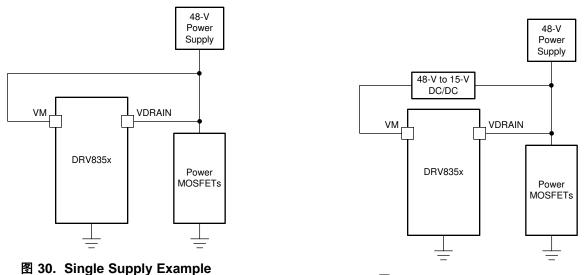

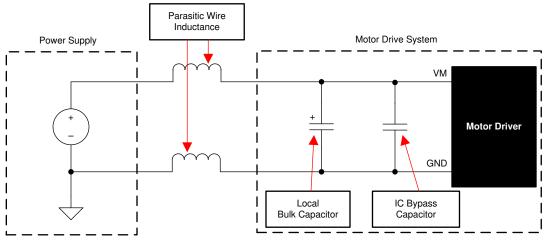

| VM     | 2        | 2        | PWR                 | Gate driver power supply input. Connect to either VDRAIN or separate gate driver supply voltage. Connect a X5R or X7R, 0.1-µF, VM-rated ceramic and greater then or equal to 10-uF local capacitance between the VM and GND pins. |

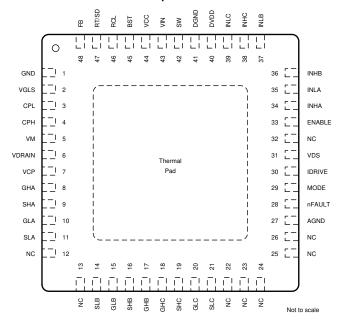

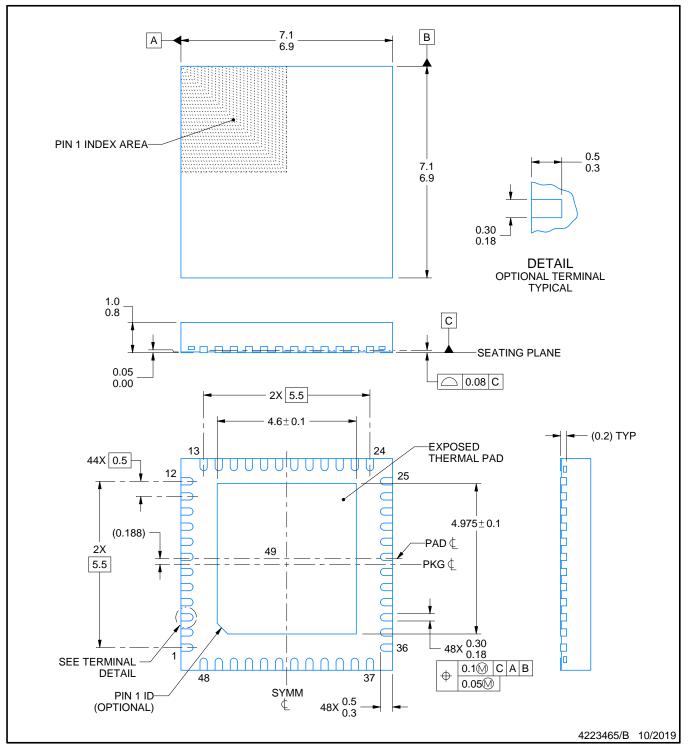

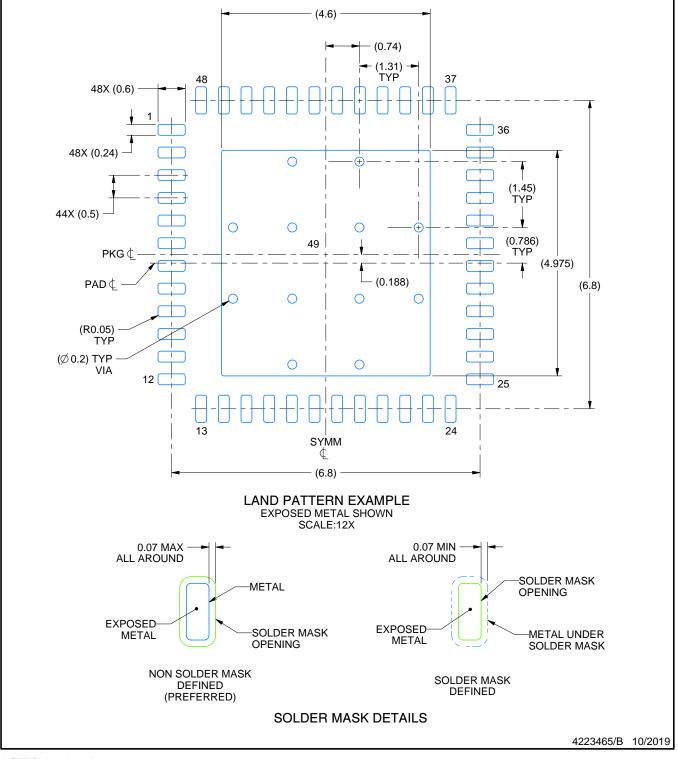

#### DRV8350RH RGZ Package 48-Pin VQFN With Exposed Thermal Pad Top View

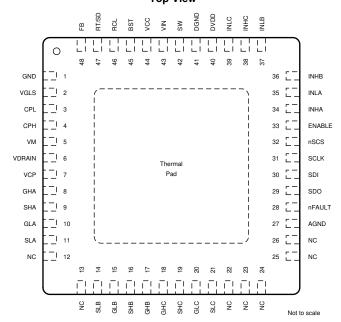

#### DRV8350RS RGZ Package 48-Pin VQFN With Exposed Thermal Pad Top View

## DRV8350, DRV8350R DRV8353, DRV8353R

ZHCSIN3A - AUGUST 2018 - REVISED JUNE 2019

### Pin Functions—48-Pin DRV8350R Devices

|            | PIN       |           | +                   |                                                                                                                                                                                                                   |

|------------|-----------|-----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       |           | NO.       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                       |

|            | DRV8350RH | DRV8350RS |                     |                                                                                                                                                                                                                   |

|            | 27        | 27        | PWR                 | Device analog ground. Connect to system ground.                                                                                                                                                                   |

| BST        | 45        | 45        | PWR                 | Buck regulator bootstrap input. Connect a X5R or X7R, 0.01-µF, 16-V, capacitor between the BST and SW pins.                                                                                                       |

| СРН        | 4         | 4         | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                                                                             |

| CPL        | 3         | 3         | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                                                                             |

| DGND       | 41        | 41        | PWR                 | Device digital ground. Connect to system ground.                                                                                                                                                                  |

| DVDD       | 40        | 40        | PWR                 | 5-V internal regulator output. Connect a X5R or X7R, 1-μF, 6.3-V ceramic capacitor between the DVDD and DGND pins. Thi regulator can source up to 10 mA externally.                                               |

| ENABLE     | 33        | 33        | I                   | Gate driver enable. When this pin is logic low the device goes to a low power sleep mode. An 8 to 40-µs low pulse can be used to reset fault conditions.                                                          |

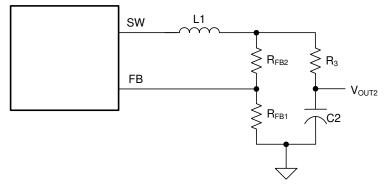

| ⁼В         | 48        | 48        | I                   | Buck feedback input. A resistor divider from the buck post inductor output to this pin sets the buck output voltage.                                                                                              |

| GHA        | 8         | 8         | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                  |

| GHB        | 17        | 17        | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                  |

| GHC        | 18        | 18        | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                  |

| GLA        | 10        | 10        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                    |

| GLB        | 15        | 15        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                    |

| GLC        | 20        | 20        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                    |

| GND        | 1         | 1         | PWR                 | Device primary ground. Connect to system ground.                                                                                                                                                                  |

| DRIVE      | 30        | _         | I                   | Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                   |

| NHA        | 34        | 34        | 1                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                   |

| NHB        | 36        | 36        | 1                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                   |

| NHC        | 38        | 38        |                     | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                   |

| NLA        | 35        | 35        |                     | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                     |

| NLB        | 35        | 35        |                     | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                     |

|            |           |           |                     |                                                                                                                                                                                                                   |

| NLC        | 39        | 39        | 1                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                     |

| MODE       | 29        |           | 1                   | PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                                                              |

| NC         | 12        | 12        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 13        | 13        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 22        | 22        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 23        | 23        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 24        | 24        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 25        | 25        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 26        | 26        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| NC         | 32        | —         | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |

| hFAULT     | 28        | 28        | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                                                           |

| nSCS       | _         | 32        | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                               |

| RCL        | 46        | 46        | I.                  | Current limit off time set input. Connect a resistor between RCL and GND.                                                                                                                                         |

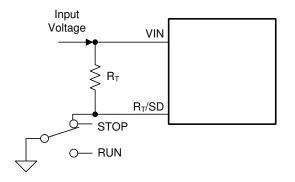

| RT/SD      | 47        | 47        | 1                   | On time set and remote shutdown input. Connect a resistor between RT/SD and VIN.                                                                                                                                  |

| SCLK       | —         | 31        | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                             |

| SDI        | —         | 30        | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                          |

| SDO        | _         | 29        | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                        |

| SHA        | 9         | 9         | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                       |

| SHB        | 16        | 16        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                       |

| SHC        | 19        | 19        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                       |

| SLA        | 11        | 11        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                         |

| SLB        | 14        | 14        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                         |

| SLC        | 21        | 21        | 1                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                         |

| SW         | 42        | 42        | 0                   | Buck switch node. Connect this pin to an inductor, diode, and the CB bootstrap capacitor.                                                                                                                         |

| VCC        | 42        | 44        | PWR                 | <ul> <li>7-V internal regulator output. Gate supply for buck switch. Connect a X5R or X7R, 0.47-µF, 16-V ceramic capacitor between the VCC and GND pins.</li> </ul>                                               |

| VCP        | 7         | 7         | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VCP and VDRAIN pins.                                                                                                           |

| VDRAIN     | 6         | 6         |                     | High-side MOSFET drain sense input and charge pump reference. Connect to the common point of the MOSFET drains.                                                                                                   |

| VDRAIN     |           | 0         |                     |                                                                                                                                                                                                                   |

| 000<br>000 | 31<br>2   | 2         | I<br>PWR            | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.<br>11-V internal regulator output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VGLS and GND pins. |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain

DRV8350, DRV8350R DRV8353, DRV8353R ZHCSIN3A – AUGUST 2018 – REVISED JUNE 2019

www.ti.com.cn

INSTRUMENTS

**FEXAS**

#### Pin Functions—48-Pin DRV8350R Devices (continued)

|      | PIN       |           |                     | DESCRIPTION                                                                                                                                                                                                                       |

|------|-----------|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | N         | 0.        | TYPE <sup>(1)</sup> |                                                                                                                                                                                                                                   |

| NAME | DRV8350RH | DRV8350RS |                     |                                                                                                                                                                                                                                   |

| VIN  | 43        | 43        | PWR                 | Buck regulator power supply input. Place an X5R or X7R, VM-rated ceramic capacitor between the VIN and GND pins.                                                                                                                  |

| VM   | 5         | 5         | PWR                 | Gate driver power supply input. Connect to either VDRAIN or separate gate driver supply voltage. Connect a X5R or X7R, 0.1-µF, VM-rated ceramic and greater then or equal to 10-uF local capacitance between the VM and GND pins. |

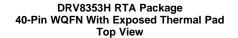

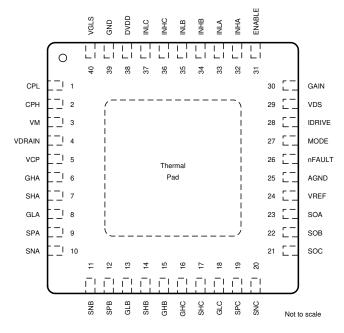

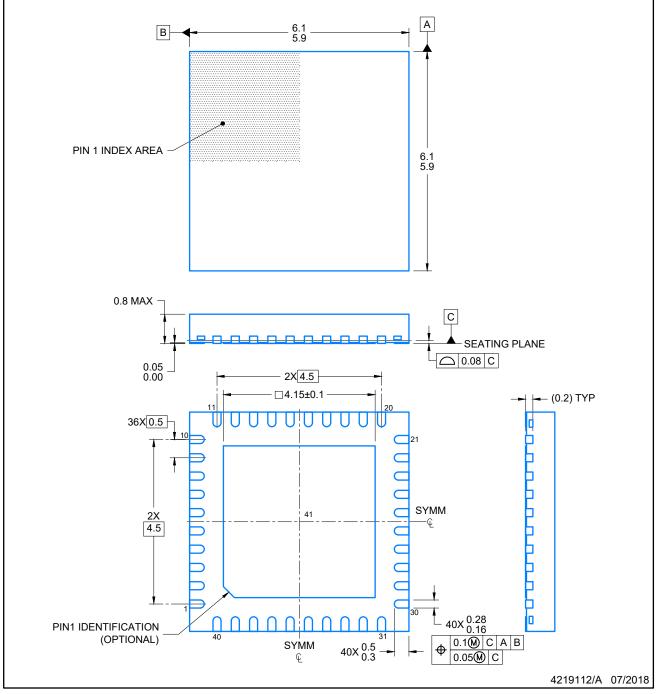

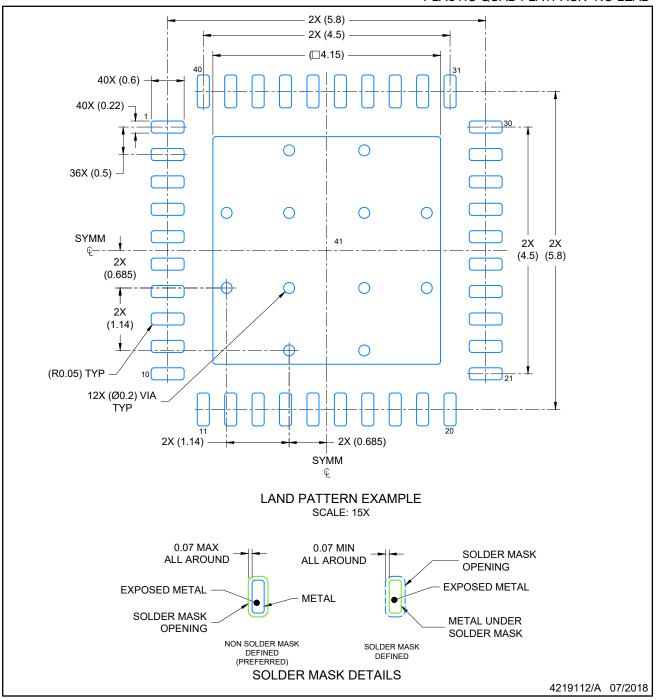

#### Pin Functions—40-Pin DRV8353 Devices

|        | PIN      |    |                     |                                                                                                                                                                     |

|--------|----------|----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.      |    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                         |

| NAME   | DRV8353H |    |                     |                                                                                                                                                                     |

| AGND   | 25       | 25 | PWR                 | Device analog ground. Connect to system ground.                                                                                                                     |

| СРН    | 2        | 2  | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                               |

| CPL    | 1        | 1  | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                               |

| DVDD   | 38       | 38 | PWR                 | 5-V internal regulator output. Connect a X5R or X7R, 1-µF, 6.3-V ceramic capacitor between the DVDD and GND pins. This regulator can source up to 10 mA externally. |

| ENABLE | 31       | 31 | I                   | Gate driver enable. When this pin is logic low the device goes to a low power sleep mode. An 8 to 40-µs low pulse can be used to reset fault conditions.            |

| GAIN   | 30       | _  | I                   | Amplifier gain setting. The pin is a 4 level input pin set by an external resistor.                                                                                 |

| GND    | 39       | 39 | PWR                 | Device power ground. Connect to system ground.                                                                                                                      |

| GHA    | 6        | 6  | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                    |

| GHB    | 15       | 15 | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                    |

| GHC    | 16       | 16 | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                    |

| GLA    | 8        | 8  | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                      |

| GLB    | 13       | 13 | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                      |

| GLC    | 18       | 18 | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                      |

| IDRIVE | 28       | _  | I                   | Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                     |

| INHA   | 32       | 32 | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                     |

| INHB   | 34       | 34 | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                     |

| INHC   | 36       | 36 | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                     |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain

# Pin Functions—40-Pin DRV8353 Devices (continued)

|        | PIN      |          |                     |                                                                                                                                                                                                                                   |

|--------|----------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.      |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                       |

| NAME   | DRV8353H | DRV8353S |                     |                                                                                                                                                                                                                                   |

| INLA   | 33       | 33       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                                     |

| INLB   | 35       | 35       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                                     |

| INLC   | 37       | 37       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                                     |

| MODE   | 27       | _        | I                   | PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                                                                              |

| nFAULT | 26       | 26       | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                                                                           |

| nSCS   | _        | 30       | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                               |

| SCLK   | —        | 29       | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                                             |

| SDI    | —        | 28       | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                                          |

| SDO    | —        | 27       | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                                        |

| SHA    | 7        | 7        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SHB    | 14       | 14       | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SHC    | 17       | 17       | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SNA    | 10       | 10       | I                   | Shunt amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                     |

| SNB    | 11       | 11       | I                   | Shunt amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                     |

| SNC    | 20       | 20       | I                   | Shunt amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                     |

| SOA    | 23       | 23       | 0                   | Shunt amplifier output.                                                                                                                                                                                                           |

| SOB    | 22       | 22       | 0                   | Shunt amplifier output.                                                                                                                                                                                                           |

| SOC    | 21       | 21       | 0                   | Shunt amplifier output.                                                                                                                                                                                                           |

| SPA    | 9        | 9        | I                   | Low-side source sense and shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                         |

| SPB    | 12       | 12       | I                   | Low-side source sense and shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                         |

| SPC    | 19       | 19       | I                   | Low-side source sense and shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                         |

| VCP    | 5        | 5        | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VCP and VDRAIN pins.                                                                                                                           |

| VDRAIN | 4        | 4        | I                   | High-side MOSFET drain sense input and charge pump reference. Connect to the common point of the MOSFET drains.                                                                                                                   |

| VDS    | 29       | _        | I                   | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                                      |

| VGLS   | 40       | 40       | PWR                 | 11-V internal regulator output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VGLS and GND pins.                                                                                                                 |

| VM     | 3        | 3        | PWR                 | Gate driver power supply input. Connect to either VDRAIN or separate gate driver supply voltage. Connect a X5R or X7R, 0.1-µF, VM-rated ceramic and greater then or equal to 10-uF local capacitance between the VM and GND pins. |

| VREF   | 24       | 24       | PWR                 | Shunt amplifier power supply input and reference. Connect a X5R or X7R, 0.1-µF, 6.3-V ceramic capacitor between the VREF and AGND pins.                                                                                           |

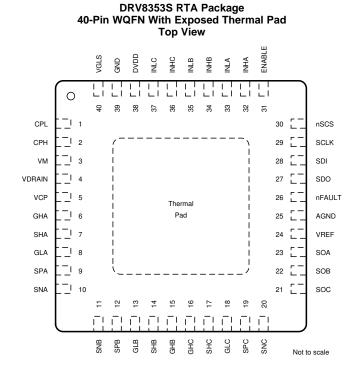

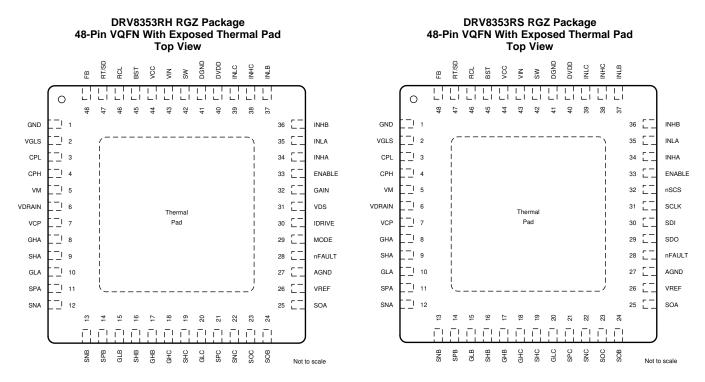

#### Pin Functions—48-Pin DRV8353R Devices

|        | PIN       |           |                     |                                                                                                                                                                      |  |

|--------|-----------|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO.       |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                          |  |

|        | DRV8353RH | DRV8353RS |                     |                                                                                                                                                                      |  |

| AGND   | 27        | 27        | PWR                 | Device analog ground. Connect to system ground.                                                                                                                      |  |

| BST    | 45        | 45        | PWR                 | Buck regulator bootstrap input. Connect a X5R or X7R, 0.01-µF, 16-V, capacitor between the BST and SW pins.                                                          |  |

| CPH    | 4         | 4         | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                                |  |

| CPL    | 3         | 3         | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VDRAIN-rated ceramic capacitor between the CPH and CPL pins.                                                |  |

| DGND   | 41        | 41        | PWR                 | Device ground. Connect to system ground.                                                                                                                             |  |

| DVDD   | 40        | 40        | PWR                 | 5-V internal regulator output. Connect a X5R or X7R, 1-μF, 6.3-V ceramic capacitor between the DVDD and DGND pins. This regulator can source up to 10 mA externally. |  |

| ENABLE | 33        | 33        | I                   | Gate driver enable. When this pin is logic low the device goes to a low power sleep mode. An 8 to 40-µs low pulse can be used to reset fault conditions.             |  |

| FB     | 48        | 48        | I                   | Buck feedback input. A resistor divider from the buck post inductor output to this pin sets the buck output voltage.                                                 |  |

| GAIN   | 32        | —         | I                   | Amplifier gain setting. The pin is a 4 level input pin set by an external resistor.                                                                                  |  |

| GND    | 1         | 1         | PWR                 | Device power ground. Connect to system ground.                                                                                                                       |  |

| GHA    | 8         | 8         | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                     |  |

| GHB    | 17        | 17        | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                     |  |

| GHC    | 18        | 18        | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                     |  |

| GLA    | 10        | 10        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                       |  |

| GLB    | 15        | 15        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                       |  |

| GLC    | 20        | 20        | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                       |  |

| IDRIVE | 30        | —         | I                   | Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                      |  |

| INHA   | 34        | 34        | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                      |  |

| INHB   | 36        | 36        | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                      |  |

| INHC   | 38        | 38        | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                      |  |

| INLA   | 35        | 35        | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                        |  |

| INLB   | 37        | 37        | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                        |  |

| INLC   | 39        | 39        | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                        |  |

| MODE   | 29        |           | I                   | PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                 |  |

| nFAULT | 28        | 28        | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                              |  |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain

# Pin Functions—48-Pin DRV8353R Devices (continued)

|        | PIN       |           |                     |                                                                                                                                                                                                                                   |

|--------|-----------|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.       |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                       |

|        | DRV8353RH | DRV8353RS |                     |                                                                                                                                                                                                                                   |

| nSCS   | —         | 32        | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                               |

| RCL    | 46        | 46        | I                   | Current limit off time set input. Connect a resistor between RCL and GND.                                                                                                                                                         |

| RT/SD  | 47        | 47        | I                   | On time set and remote shutdown input. Connect a resistor between RT/SD and VIN.                                                                                                                                                  |

| SCLK   | —         | 31        | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                                             |

| SDI    | —         | 30        | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                                          |

| SDO    | —         | 29        | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                                        |

| SHA    | 9         | 9         | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SHB    | 16        | 16        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SHC    | 19        | 19        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                       |

| SNA    | 12        | 12        | I                   | Shunt amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                     |

| SNB    | 13        | 13        | I                   | Shunt amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                     |

| SNC    | 22        | 22        | I                   | Shunt amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                     |

| SOA    | 25        | 25        | 0                   | Shunt amplifier output.                                                                                                                                                                                                           |

| SOB    | 24        | 24        | 0                   | Shunt amplifier output.                                                                                                                                                                                                           |

| SOC    | 23        | 23        | 0                   | Shunt amplifier output.                                                                                                                                                                                                           |

| SPA    | 11        | 11        | I                   | Low-side source sense and shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                         |

| SPB    | 14        | 14        | I                   | Low-side source sense and shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                         |

| SPC    | 21        | 21        | I                   | Low-side source sense and shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                         |

| SW     | 42        | 42        | 0                   | Buck switch node. Connect this pin to an inductor, diode, and the CB bootstrap capacitor.                                                                                                                                         |

| VCC    | 44        | 44        | PWR                 | 7-V internal regulator output. Gate supply for buck switch. Connect a X5R or X7R, 0.47-µF, 16-V ceramic capacitor between the VCC and GND pins.                                                                                   |

| VCP    | 7         | 7         | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VCP and VDRAIN pins.                                                                                                                           |

| VDRAIN | 6         | 6         | I                   | High-side MOSFET drain sense input and charge pump reference. Connect to the common point of the MOSFET drains.                                                                                                                   |

| VDS    | 31        | _         | I                   | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                                      |

| VGLS   | 2         | 2         | PWR                 | 11-V internal regulator output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the VGLS and GND pins.                                                                                                                 |

| VIN    | 43        | 43        | PWR                 | Buck regulator power supply input. Place an X5R or X7R, VM-rated ceramic capacitor between the VIN and BGND pins.                                                                                                                 |

| VM     | 5         | 5         | PWR                 | Gate driver power supply input. Connect to either VDRAIN or separate gate driver supply voltage. Connect a X5R or X7R, 0.1-µF, VM-rated ceramic and greater then or equal to 10-uF local capacitance between the VM and GND pins. |

| VREF   | 26        | 26        | PWR                 | Shunt amplifier power supply input and reference. Connect a X5R or X7R, 0.1-µF, 6.3-V ceramic capacitor between the VREF and AGND pins.                                                                                           |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

at  $T_A = -40^{\circ}$ C to +125°C (unless otherwise noted)<sup>(1)</sup>

|                                                                                                 | MIN                | MAX                      | UNIT |

|-------------------------------------------------------------------------------------------------|--------------------|--------------------------|------|

| GATE DRIVER                                                                                     |                    |                          |      |

| Power supply pin voltage (VM)                                                                   | -0.3               | 80                       | V    |

| Voltage differential between ground pins (AGND, BGND, DGND, PGND)                               | -0.3               | 0.3                      | V    |

| MOSFET drain sense pin voltage (VDRAIN)                                                         | -0.3               | 102                      | V    |

| MOSFET drain sense pin voltage slew rate (VDRAIN)                                               | 0                  | 2                        | V/µs |

| Charge pump pin voltage (CPH, VCP)                                                              | -0.3               | V <sub>VDRAIN</sub> + 16 | V    |

| Charge-pump negative-switching pin voltage (CPL)                                                | -0.3               | V <sub>VDRAIN</sub>      | V    |

| Low-side gate drive regulator pin voltage (VGLS)                                                | -0.3               | 18                       | V    |

| Internal logic regulator pin voltage (DVDD)                                                     | -0.3               | 5.75                     | V    |

| Digital pin voltage (ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nFAULT, nSCS, SCLK, SDI, SDO, VDS) | -0.3               | 5.75                     | V    |

| Continuous high-side gate drive pin voltage (GHx)                                               | -5 <sup>(2)</sup>  | V <sub>VCP</sub> + 0.3   | V    |

| Transient 200-ns high-side gate drive pin voltage (GHx)                                         | -10                | V <sub>VCP</sub> + 0.3   | V    |

| High-side gate drive pin voltage with respect to SHx (GHx)                                      | -0.3               | 16                       | V    |

| Continuous high-side source sense pin voltage (SHx)                                             | -5 <sup>(2)</sup>  | 102                      | V    |

| Continuous high-side source sense pin voltage (SHx)                                             | -5 <sup>(2)</sup>  | V <sub>VDRAIN</sub> + 5  | V    |

| Transient 200-ns high-side source sense pin voltage (SHx)                                       | -10                | V <sub>VDRAIN</sub> + 10 | V    |

| Continuous low-side gate drive pin voltage (GLx)                                                | -1.0               | $V_{VGLS} + 0.3$         | V    |

| Transient 200-ns low-side gate drive pin voltage (GLx)                                          | -5.0               | $V_{VGLS} + 0.3$         | V    |

| Gate drive pin source current (GHx, GLx)                                                        | Internally limited | Internally limited       | А    |

| Gate drive pin sink current (GHx, GLx)                                                          | Internally limited | Internally limited       | А    |

| Continuous low-side source sense pin voltage (SLx)                                              | -1                 | 1                        | V    |

| Transient 200-ns low-side source sense pin voltage (SLx)                                        | -5                 | 5                        | V    |

| Continuous shunt amplifier input pin voltage (SNx, SPx)                                         | -1                 | 1                        | V    |

| Transient 200-ns shunt amplifier input pin voltage (SNx, SPx)                                   | -5                 | 5                        | V    |

| Reference input pin voltage (VREF)                                                              | -0.3               | 5.75                     | V    |

| Shunt amplifier output pin voltage (SOx)                                                        | -0.3               | $V_{VREF}$ + 0.3         | V    |

| BUCK REGULATOR                                                                                  |                    |                          |      |

| Power supply pin voltage (VIN)                                                                  | -0.3               | 100                      | V    |

| Bootstrap pin voltage (BST)                                                                     | -0.3               | 114                      | V    |

| Bootstrap pin voltage with respect to SW (BST)                                                  | -0.3               | 14                       | V    |

| Bootstrap pin voltage with respect to VCC (BST)                                                 | -0.3               | 100                      | V    |

| Switching node pin voltage (SW)                                                                 | -1                 | V <sub>VIN</sub>         | V    |

| Internal regulator pin voltage (VCC)                                                            | -0.3               | 14                       | V    |

| Input pin voltage (FB, RCL, RT/SD)                                                              | -0.3               | 7                        | V    |

| DRV835x                                                                                         |                    |                          |      |

| Ambient temperature, T <sub>A</sub>                                                             | -40                | 125                      | °C   |

| Junction temperature, T <sub>J</sub>                                                            | -40                | 150                      | °C   |

| Storage temperature, T <sub>stg</sub>                                                           | -65                | 150                      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) VDRAIN pin voltage with respect to high-side gate pin (GHx) and phase node pin voltage (SHx) should be limited to 102 V maximum. This will limit the GHx and SHx pin negative voltage capability when VDRAIN is greater than 92 V.

www.ti.com.cn

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| M                  | Electrostatia discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

## 7.3 Recommended Operating Conditions

at  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  (unless otherwise noted)

|                      |                                                                              | MIN | MAX                | UNIT |

|----------------------|------------------------------------------------------------------------------|-----|--------------------|------|

| GATE DRIVE           | ER                                                                           |     |                    |      |

| V <sub>VM</sub>      | Gate driver power supply voltage (VM)                                        | 9   | 75                 | V    |

| V <sub>VDRAIN</sub>  | Charge pump reference and drain voltage sense (VDRAIN)                       | 7   | 100                | V    |

| VI                   | Input voltage (ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nSCS, SCLK, SDI, VDS) | 0   | 5.5                | V    |

| f <sub>PWM</sub>     | Applied PWM signal (INHx, INLx)                                              | 0   | 200 <sup>(1)</sup> | kHz  |

| t <sub>SH</sub>      | Switch-node slew rate range (SHx)                                            | 0   | 2                  | V/ns |

| I <sub>GATE_HS</sub> | High-side average gate-drive current (GHx)                                   | 0   | 25 <sup>(1)</sup>  | mA   |

| I <sub>GATE_LS</sub> | Low-side average gate-drive current (GLx)                                    | 0   | 25 <sup>(1)</sup>  | mA   |

| I <sub>DVDD</sub>    | External load current (DVDD)                                                 | 0   | 10 <sup>(1)</sup>  | mA   |

| V <sub>VREF</sub>    | Reference voltage input (VREF)                                               | 3   | 5.5                | V    |

| I <sub>SO</sub>      | Shunt amplifier output current (SOx)                                         | 0   | 5                  | mA   |

| V <sub>OD</sub>      | Open drain pullup voltage (nFAULT, SDO)                                      | 0   | 5.5                | V    |

| I <sub>OD</sub>      | Open drain output current (nFAULT, SDO)                                      | 0   | 5                  | mA   |

| BUCK REGU            | JLATOR                                                                       |     |                    |      |

| V <sub>VIN</sub>     | Power supply voltage (VIN)                                                   | 6   | 95                 | V    |

| DRV835x              |                                                                              |     |                    |      |

| T <sub>A</sub>       | Operating ambient temperature                                                | -40 | 125                | °C   |

| TJ                   | Operating junction temperature                                               | -40 | 150                | °C   |

(1) Power dissipation and thermal limits must be observed.

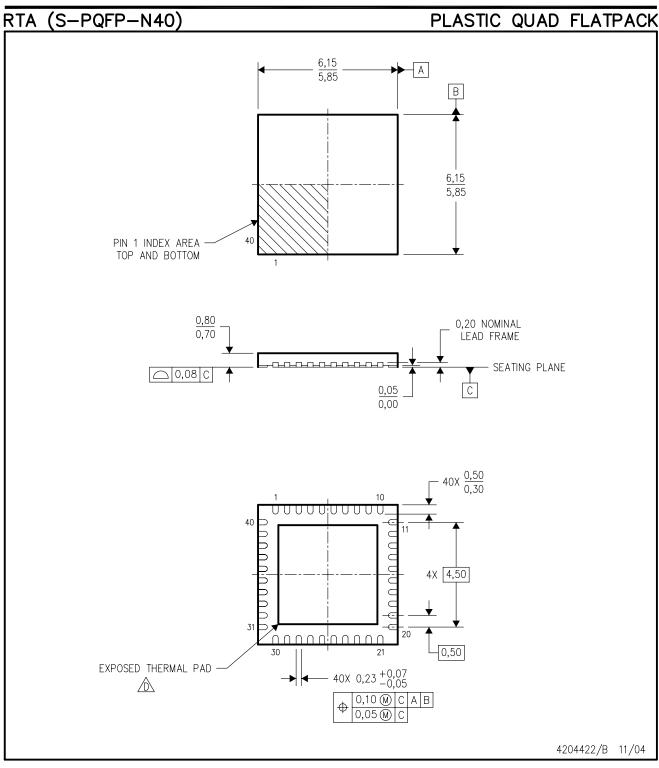

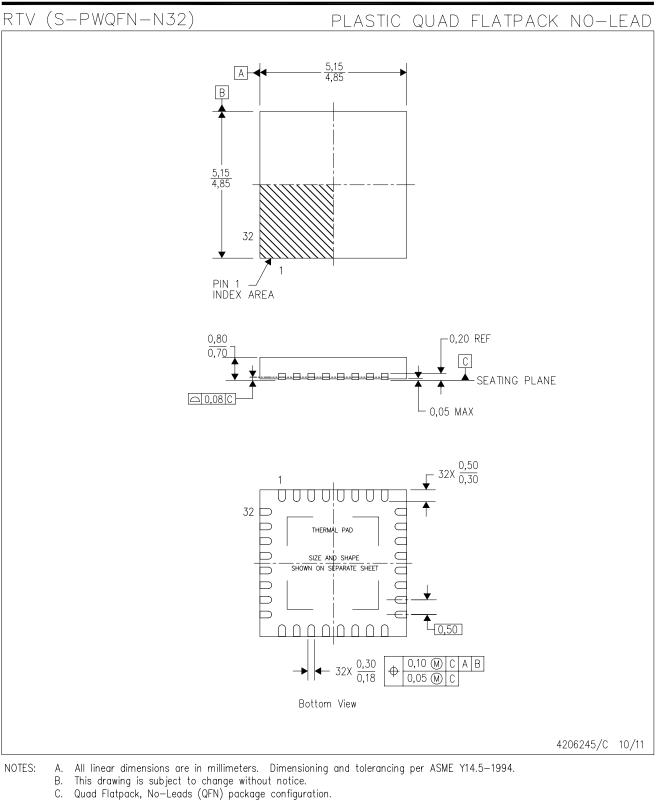

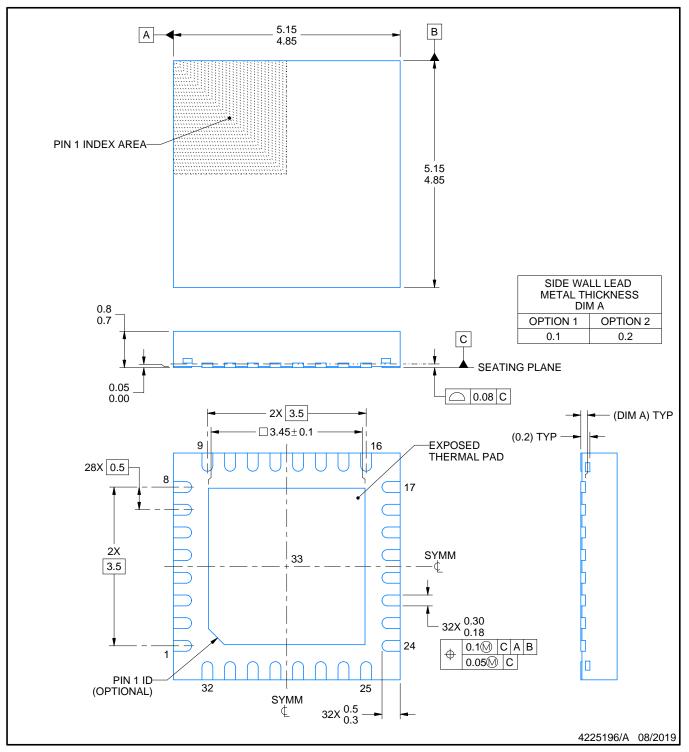

## 7.4 Thermal Information

|                       |                                              | DRV8350    | DRV8353    | DRV835xR   |      |

|-----------------------|----------------------------------------------|------------|------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTV (WQFN) | RTA (WQFN) | RGZ (VQFN) | UNIT |

|                       |                                              | 32 PINS    | 40 PINS    | 48 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 29.2       | 26.1       | 24.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 15.2       | 13.1       | 12.0       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.2        | 8.4        | 7.1        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.1        | 0.1        | 0.1        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 9.2        | 8.4        | 7.1        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.2        | 1.1        | 0.8        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

TEXAS INSTRUMENTS

www.ti.com.cn

# 7.5 Electrical Characteristics

at  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{VM} = 9$  to 75 V,  $V_{VDRAIN} = 9$  to 100 V,  $V_{VIN} = 48$  V (unless otherwise noted)

|                                    | PARAMETER                             | TEST CONDITIONS                                                               | MIN  | TYP      | MAX   | UNIT |

|------------------------------------|---------------------------------------|-------------------------------------------------------------------------------|------|----------|-------|------|

| POWER SU                           | IPPLIES (DVDD, VCP, VGLS, VM)         |                                                                               |      |          |       |      |

| I <sub>VM</sub>                    | VM operating supply current           | V <sub>VM</sub> = V <sub>VDRAIN</sub> = 48 V, ENABLE = 3.3 V, INHx/INLx = 0 V |      | 8.5      | 13    | mA   |

| IVDRAIN                            | VDRAIN operating supply current       | V <sub>VM</sub> = V <sub>VDRAIN</sub> = 48 V, ENABLE = 3.3 V, INHx/INLx = 0 V |      | 1.9      | 4     | mA   |

|                                    |                                       | ENABLE = 0 V, $V_{VM}$ = $V_{VDRAIN}$ = 48 V, $T_A$ = 25°C                    |      | 20       | 40    |      |

| SLEEP                              | Sleep mode supply current             | ENABLE = 0 V, $V_{VM}$ = $V_{VDRAIN}$ = 48 V, $T_A$ = 125°C                   |      |          | 100   | μA   |

| t <sub>RST</sub>                   | Reset pulse time                      | ENABLE = 0 V period to reset faults                                           | 5    |          | 40    | μs   |

| t <sub>WAKE</sub>                  | Turnon time                           | $V_{VM} > V_{UVLO}$ , ENABLE = 3.3 V to outputs ready                         |      |          | 1     | ms   |

| t <sub>SLEEP</sub>                 | Turnoff time                          | ENABLE = 0 V to device sleep mode                                             |      |          | 1     | ms   |

| V <sub>DVDD</sub>                  | DVDD regulator voltage                | $I_{\text{DVDD}} = 0 \text{ to } 10 \text{ mA}$                               | 4.75 | 5        | 5.25  | V    |

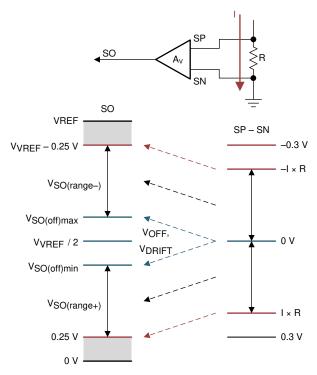

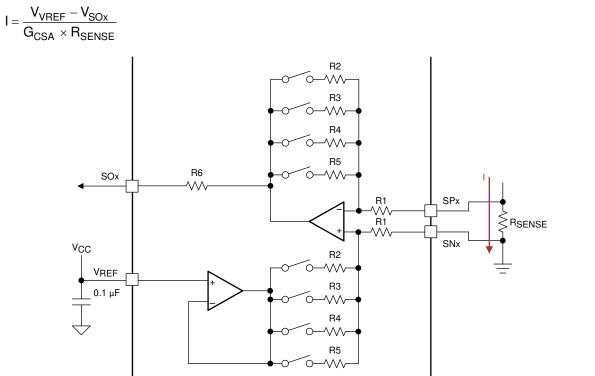

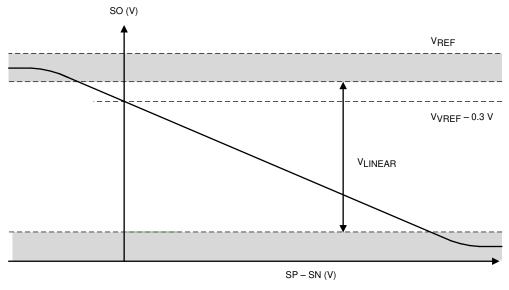

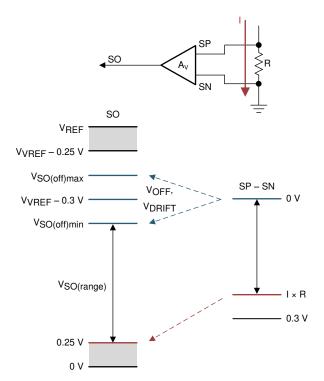

|                                    |                                       | $V_{VM} = 15 \text{ V}, \text{ I}_{VCP} = 0 \text{ to } 25 \text{ mA}$        | 9    | 10.5     | 12    |      |