LM3242

ZHCSAP9E -OCTOBER 2011-REVISED AUGUST 2015

# LM3242 具有自动旁路功能的 6MHz、750mA 微型可调降压 DC-DC 转换器、适用于 RF 功率放大器

## 1 特性

- 由单节锂离子电池提供 2.7V 至 5.5V 的输入工作电压

- 6MHz(典型值)脉宽调制 (PWM)开关频率

- 0.4V 至 3.6V 可调输出电压

- 750mA 最大负载性能 (旁路模式下可达 1A)

- 高效率(3.9 V<sub>IN</sub>, 3.3 V<sub>OUT</sub>, 500mA 时的典型效率为 95%)

- 自动 ECO/PWM/BP 模式切换

- 电流过载保护

- 热过载保护

- 软启动功能

- 0805 (2012) 外壳尺寸内的小型芯片电感器

## 2 应用

- 电池供电类 3G/4G RF PA

- 电池供电类射频 (RF) 器件

- 手持无线电

- RF 个人计算机 (PC) 卡

## 3 说明

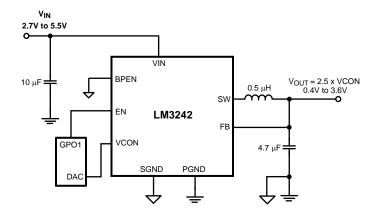

LM3242 是一款 DC-DC 转换器,针对由单节锂离子电池供电的 RF 功率放大器 (PA) 进行了优化。此外,该器件也可用于其他应用。 该器件可将 2.7V 至 5.5V 范围内的输入电压降至介于 0.4V 至 3.6V 之间的可调节输出电压。输出电压可通过控制 RF PA 功率级和效率的 VCON 模拟输入进行设置。

LM3242 具有 5 种工作模式。 在 PWM 模式下,该器件以

6MHz(典型值)固定频率运行,因此可在驱动中等到重负载时最大限度地抑制 RF 干扰。 轻负载时,器件自动进入 ECO 模式并以减少的开关频率运行。 在 ECO 模式下,静态电流被减少并延长了电池使用寿命。 该器件在关断模式下处于关闭状态,电池流耗降至 0.1μA(典型值)。 在低电量旁路模式下,压降降至 50mV(典型值)以下。 此部件还特有一个睡眠模式。

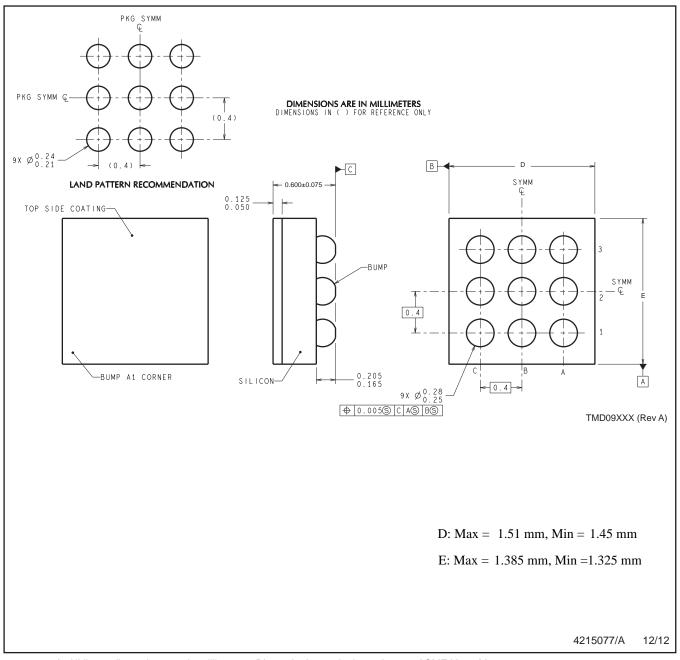

LM3242 采用 9 焊锡凸点无引线芯片级球栅阵列 (DSBGA) 封装。 高开关频率 (6MHz) 允许仅使用三个 微型表面贴装组件,包括一个电感和两个陶瓷电容。

器件信息<sup>(1)</sup>

| 部件号    | 封装        | 封装尺寸(最大值)        |

|--------|-----------|------------------|

| LM3242 | DSBGA (9) | 1.51mm × 1.385mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

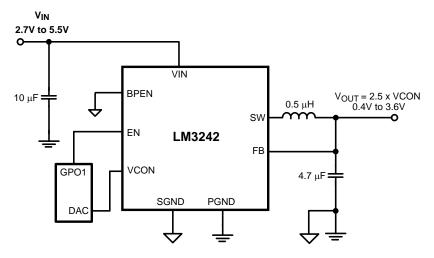

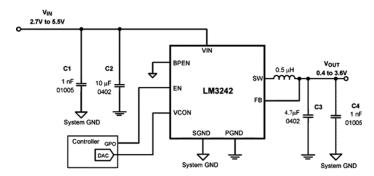

#### 典型应用

Changes from Revision C (March 2013) to Revision D

**Page**

|                            |                                                                                 | 目录                                                                        |                    |                             |      |

|----------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----------------------------|------|

| 1<br>2<br>3<br>4<br>5<br>6 | 特性                                                                              | 1<br>1<br>2<br>3<br>4<br>4<br>4<br>4<br>4<br>5<br>6<br>6<br>7<br>11<br>11 | 8<br>9<br>10<br>11 | 7.4 Device Functional Modes |      |

| È: Ż                       | 多订历史记录<br>公前版本的页码可能与当前版本有所不同。<br>ges from Revision D (March 2013) to Revision E |                                                                           |                    |                             | Page |

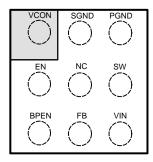

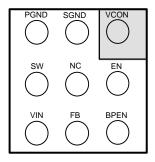

# 5 Pin Configuration and Functions

## YFQ Package 9-Pin DSBGA Top View (left); Bottom View (right)

## **Pin Functions**

|        | PIN  | TVDE | DESCRIPTION                                                                                                                                                                                                                   |

|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME | TYPE | DESCRIPTION                                                                                                                                                                                                                   |

| A1     | VCON | A/I  | Voltage control analog input. VCON controls $V_{OUT}$ in PWM and ECO modes. VCON may also be used to force bypass condition by setting VCON > $V_{IN}/2.5$ .                                                                  |

| A2     | SGND | G    | Signal ground for analog and control circuitry.                                                                                                                                                                               |

| A3     | PGND | G    | Power ground for the power MOSFETs and gate drive circuitry                                                                                                                                                                   |

| B1     | EN   | D/I  | Enable Input. Set this digital input high for normal operation. For shutdown, set low. Do not leave EN pin floating.                                                                                                          |

| B2     | NC   | _    | Do not connect to PGND directly — Internally connected to SGND.                                                                                                                                                               |

| В3     | SW   | P/O  | Switching node connection to the internal PFET switch and NFET synchronous rectifier. Connect to an inductor with a saturation current rating that exceeds the maximum Switch Peak Current Limit specification of the LM3242. |

| C1     | BPEN | D/I  | Bypass Enable input. Set this digital input high to force bypass operation. For normal operation with automatic bypass, set low or connect to ground. Do not leave this pin floating.                                         |

| C2     | FB   | А    | Feedback analog input and bypass FET output. Connect to the output at the output filter capacitor.                                                                                                                            |

| C3     | VIN  | P/I  | Voltage supply input for SMPS converter.                                                                                                                                                                                      |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                              | MIN          | MAX                             | UNIT |  |

|----------------------------------------------|--------------|---------------------------------|------|--|

| VIN to SGND                                  | -0.2         | 6                               | V    |  |

| PGND to SGND                                 | -0.2         | 0.2                             | V    |  |

| EN, VCON, BPEN                               | (SGND - 0.2) | $(V_{IN} + 0.2) \text{ w/ 6 V}$ | V    |  |

| SW, FB                                       | (PGND – 0.2) | (V <sub>IN</sub> + 0.2)         | V    |  |

| Continuous power dissipation <sup>(2)</sup>  | Interna      | Internally limited              |      |  |

| Maximum lead temperature (soldering, 10 sec) |              | 260                             | °C   |  |

| Junction temperature, T <sub>J-MAX</sub>     |              | 150                             | °C   |  |

| Storage temperature, T <sub>stg</sub>        | <b>−</b> 65  | 150                             | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                                                        |                                                                     | VALUE | UNIT |

|--------------------|--------------------------------------------------------|---------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000                                                               |       |      |

| V <sub>(ESD)</sub> | V <sub>(ESD)</sub> Electrostatic discharge             | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1250 | V    |

|                    |                                                        | Machine model                                                       | ±200  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

| over operating need an temperature range (united currentles needs) |     |         |      |

|--------------------------------------------------------------------|-----|---------|------|

|                                                                    | MIN | NOM MAX | UNIT |

| Input voltage                                                      | 2.7 | 5.5     | V    |

| Recommended load current                                           | 0   | 750     | mA   |

| PWM mode                                                           | 0   | 750     | mA   |

| Bypass mode                                                        | 0   | 1000    | mA   |

| Junction temperature, T <sub>J</sub>                               | -30 | 125     | °C   |

| Ambient temperature, T <sub>A</sub> <sup>(2)</sup>                 | -30 | 90      | °C   |

<sup>(1)</sup> All voltages are with respect to the potential at the GND pins.

#### 6.4 Thermal Information

|                                                         | LM3242      |      |

|---------------------------------------------------------|-------------|------|

| THERMAL METRIC <sup>(1)</sup>                           | YFQ (DSBGA) | UNIT |

|                                                         | 9 PINS      |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 85          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typical) and disengages at T<sub>J</sub> = 125°C (typical).

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

## 6.5 Electrical Characteristics

All typical limits in are for  $T_A = T_J = 25$ °C; all minimum and maximum limits apply over the full operating ambient temperature range (-30°C  $\le T_A = T_J \le +90$ °C). Unless otherwise noted, all specifications apply to the 典型应用 with  $V_{IN} = EN = 3.6$  V, and

|                        | PARAMETER                                 | TEST CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNIT |

|------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{FB,MIN}$           | Feedback voltage at minimum setting       | PWM mode, VCON = 0.16 V <sup>(1)</sup>                                                                  | 0.38 | 0.4  | 0.42 | V    |

| $V_{FB,MAX}$           | Feedback voltage at maximum setting       | PWM mode, VCON = 1.44 V, V <sub>IN</sub> = 4 V                                                          | 3.55 | 3.6  | 3.65 | V    |

| I <sub>SHDN</sub>      | Shutdown supply current                   | EN = SW = VCON = FB = BPEN = NC = 0 V <sup>(2)</sup>                                                    |      | 0.1  | 1    | μΑ   |

| $I_{Q}$ PWM            | PWM mode quiescent<br>current             | PWM mode, No switching VCON = 0.13 V, FB = 1 V <sup>(3)</sup>                                           |      | 650  | 795  | μΑ   |

| I <sub>Q</sub> _SLEEP  | Low-power SLEEP mode                      | EN = VIN, BPEN = NC = 0 V, SW = TriState<br>VCON < 0.08 V <sup>(3)</sup>                                |      | 60   | 80   | μΑ   |

| I <sub>Q</sub> _ECO    | ECO mode Quiescent current                | ECO mode, No switching VCON = 0.8 V, FB = 2.05 V <sup>(3)</sup>                                         |      | 60   | 80   | μΑ   |

| R <sub>DSON (P)</sub>  | Pin-pin resistance for PFET               | $V_{IN} = V_{GS} = 3.6 \text{ V}, I_{SW} = 200 \text{ mA}$                                              |      | 170  | 260  | mΩ   |

| R <sub>DSON (N)</sub>  | Pin-pin resistance for NFET               | $VIN = V_{GS} = 3.6 \text{ V}, I_{SW} = -200 \text{ mA}$                                                |      | 110  | 200  | mΩ   |

| R <sub>DSON (BP)</sub> | Pin-Pin resistance for BPFET              | $V_{IN} = V_{GS} = 3.1 \text{ V}, I_{SW} = -200 \text{ mA}$                                             |      | 80   | 110  | mΩ   |

| I <sub>LIM P</sub>     | PFET switch peak current limit            | See <sup>(4)</sup>                                                                                      | 1300 | 1450 | 1600 | mA   |

| I <sub>LIM BP</sub>    | BPFET switch peak current limit           | V <sub>FB</sub> = V <sub>IN</sub> - 1 V <sup>(4)</sup>                                                  | 310  | 400  |      | mA   |

| Fosc                   | Internal oscillator frequency             |                                                                                                         | 5.7  | 6    | 6.3  | MHz  |

| V <sub>IH</sub>        | EN, BPEN logic high input threshold       |                                                                                                         | 1.2  |      |      | V    |

| V <sub>IL</sub>        | EN, BPEN logic low input threshold        |                                                                                                         |      |      | 0.4  | V    |

| Gain                   | VCON to V <sub>OUT</sub> gain             | 0.16 V ≤ VCON ≤ 1.44 V <sup>(5)</sup>                                                                   |      | 2.5  |      | V/V  |

| I <sub>VCON</sub>      | VCON pin leakage current                  | VCON = 1 V                                                                                              |      |      | ±1   | μΑ   |

| $V_{BP,NEG}$           | Auto bypass detection negative threshold  | $VCON = 1.2 V (V_{OUT-SET} = 3 V)$<br>$V_{IN} = 3.2 V, R_L = 6 Ω, I_{OUT} = 500 mA^{(6)}$               | 165  | 200  | 235  | mV   |

| V <sub>BP,POS</sub>    | Auto bypass detection positive threshold  | $VCON = 1.2 V (V_{OUT-SET} = 3 V)$<br>$V_{IN} = 3.25 V, R_L = 6 \Omega, I_{OUT} = 500 \text{ mA}^{(7)}$ | 215  | 250  | 285  | mV   |

| I <sub>BP,SLEW</sub>   | Auto bypass I <sub>OUT</sub> slew current | BPEN = High, Forced bypass                                                                              |      | 1600 |      | mA   |

- All 0.4-V V<sub>OUT</sub> specifications are at steady-state only.

- Shutdown current includes leakage current of PFET.

- IQ specified here is when the part is not switching under test mode conditions. For operating quiescent current at no load, refer to (3)Typical Characteristics.

- Current limit is built-in, fixed, and not adjustable.

- Care must be taken to keep the VCON pin voltage less than the VIN pin voltage as this can place the part into a manufacturing test mode.

- Entering Bypass mode  $V_{IN}$  is compared to the programmed output voltage (2.5 x VCON). When  $V_{IN}$  (2.5 x VCON) falls below  $V_{BP,NEG}$ longer than  $T_{BP,NEG}$ , the Bypass FET turns on, and the switching FET turns on. Bypass mode is exited when  $V_{IN}$  – (2.5 × VCON) exceeds  $V_{BP,POS}$  longer than  $T_{BP,POS}$ , and PWM mode resumes. The hysteresis for

- the bypass detection threshold V<sub>BP,POS</sub> V<sub>BP,NEG</sub> is always positive and will be approximately 50 mV.

## 6.6 System Characteristics

The following spec table entries are ensured by design providing the component values in the #2 m are used. These parameters are not ensured by production testing. Minimum and Maximum values apply over the full operating ambient temperature range (-30°C ≤  $T_A$  ≤ +90°C) and over the  $V_{IN}$  range = 2.7 V to 5.5 V unless otherwise specified. L = 0.5 μH, DCR =  $50 m\Omega$ ,  $C_{IN}$  =  $10 \mu$ F, 6.3 V, 0603 (1608),  $C_{OUT}$  =  $4.7 \mu$ F, 6.3 V, 0402.

|                                              | PARAMETER                             | TEST CONDITIONS                                                                                                                                              | MIN  | TYP | MAX | UNIT |

|----------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| D                                            | Maximum duty cycle                    |                                                                                                                                                              | 100% |     |     |      |

| R <sub>BP</sub>                              | Bypass mode resistance <sup>(1)</sup> | $V_{IN} = V_{GS} = 3.1 \text{ V}, I_{OUT} = -500 \text{ mA}$ VCON > 1.16 V                                                                                   |      | 75  |     | mΩ   |

|                                              | Marian and a second                   | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$<br>$2.5 \times \text{VCON} \le \text{V}_{\text{IN}} - 285 \text{ mV}$                             | 750  |     |     |      |

| I <sub>OUT</sub>                             | Maximum output current capability     | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$<br>$2.5 \times \text{VCON} \ge \text{V}_{\text{IN}} - 165 \text{ mV}$ , Bypass mode               | 1000 |     |     | mA   |

| C <sub>VCON</sub>                            | VCON input capacitance                | VCON = 1 V, Test frequency = 100 KHz                                                                                                                         |      | < 1 |     | pF   |

| V <sub>OUT</sub> VCON range 0.16 V to 1.44 V |                                       | 0 m \ < 1                                                                                                                                                    | -3%  |     | 3%  |      |

|                                              |                                       | 0 mA ≤ I <sub>OUT</sub> ≤ 750 mA <sup>(2)</sup>                                                                                                              | -50  |     | 50  | mV   |

|                                              |                                       | $V_{IN}$ = 3.6 V, $V_{OUT}$ = 0.8 V<br>$I_{OUT}$ = 10 mA, ECO mode                                                                                           |      | 75% |     |      |

| η Efficiency                                 |                                       | $V_{IN}$ = 3.6 V, $V_{OUT}$ = 1.8 V $I_{OUT}$ = 200 mA, PWM mode                                                                                             |      | 90% |     |      |

|                                              |                                       | $V_{IN}$ = 3.9 V, $V_{OUT}$ = 3.3 V $I_{OUT}$ = 500 mA, PWM mode                                                                                             |      | 95% |     |      |

| LINE TR                                      | Line transient response               | $V_{IN}=3.6~V$ to 4.2 V, $T_R=T_F=10~\mu s,$ $I_{OUT}=100~mA,~V_{OUT}=0.8 V$                                                                                 |      | 50  |     | mVpk |

| LOAD <sub>TR</sub>                           | Load transient response               | $V_{IN} = 3.1 \text{ V}/3.6 \text{ V}/4.5 \text{ V}, V_{OUT} = 0.8 \text{ V}, \\ I_{OUT} = 50 \text{ mA to } 150 \text{ mA} \\ T_R = T_F = 0.1  \mu\text{s}$ |      | 50  |     | mVpk |

<sup>(1)</sup> Total resistance in Bypass mode. Total includes the Bypass FET resistance in parallel with the PWM switch path resistance (PFET resistance and series inductor parasistic resistance.)

## 6.7 Timing Requirements

|                      |                                                                                                                                                                                                                                | MIN | NOM | MAX               | UNIT |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------|------|

| T                    | $V_{OUT}$ rise time, VCON change to 90% $V_{IN}$ = 3.7 V, $V_{OUT}$ = 1.4 V to 3.4 V 0.1 μs < VCON_T <sub>R</sub> < 1 μs, R <sub>L</sub> = 12 Ω                                                                                |     | 9   |                   | μs   |

| T <sub>VCON_TR</sub> | $V_{OUT}$ fall time VCON change to 10% $V_{IN}$ = 3.7 V, $V_{OUT}$ = 3.4 V to 1.4 V 0.1 $\mu$ s < VCON_T <sub>F</sub> < 1 $\mu$ s, $R_L$ = 12 $\Omega$                                                                         |     | 9   |                   | μs   |

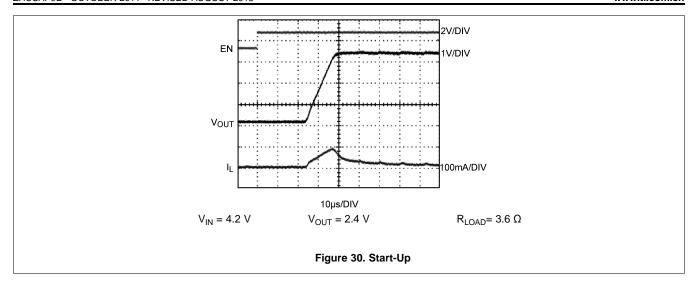

| T <sub>ON</sub>      | Turnon time (time for output to reach 95% final value after Enable low-to-high transition)<br>EN = Low-to-High, V <sub>IN</sub> = 4.2 V, V <sub>OUT</sub> = 3.4 V<br>I <sub>OUT</sub> = < 1 mA, C <sub>OUT</sub> = 4.7 $\mu$ F |     |     | 50 <sup>(1)</sup> | μs   |

| T <sub>BP, NEG</sub> | Auto bypass detect negative threshold delay time (2)                                                                                                                                                                           |     | 10  |                   | μs   |

| T <sub>BP, POS</sub> | Auto bypass detect positive threshold delay time (3)                                                                                                                                                                           | · · | 0.1 |                   | μs   |

<sup>(1)</sup> This parameter is not production-limit tested.

<sup>(2)</sup> Linearity limits are ±3% or ±50 mV, whichever is larger. V<sub>OUT</sub> is monotonic in nature with respect to VCON input.

<sup>(2)</sup> Entering Bypass mode V<sub>IN</sub> is compared to the programmed output voltage (2.5 x VCON). When V<sub>IN</sub> − (2.5 x VCON) falls below V<sub>BP,NEG</sub> longer than T<sub>BP,NEG</sub>, the Bypass FET turns on, and the switching FET turns on.

<sup>(3)</sup> Bypass mode is exited when V<sub>IN</sub> - (2.5 x VCON) exceeds V<sub>BP,POS</sub> longer than T<sub>BP,POS</sub>, and PWM mode resumes. The hysteresis for the bypass detection threshold V<sub>BP,POS</sub> - V<sub>BP,NEG</sub> is always be positive and will be approximately 50 mV.

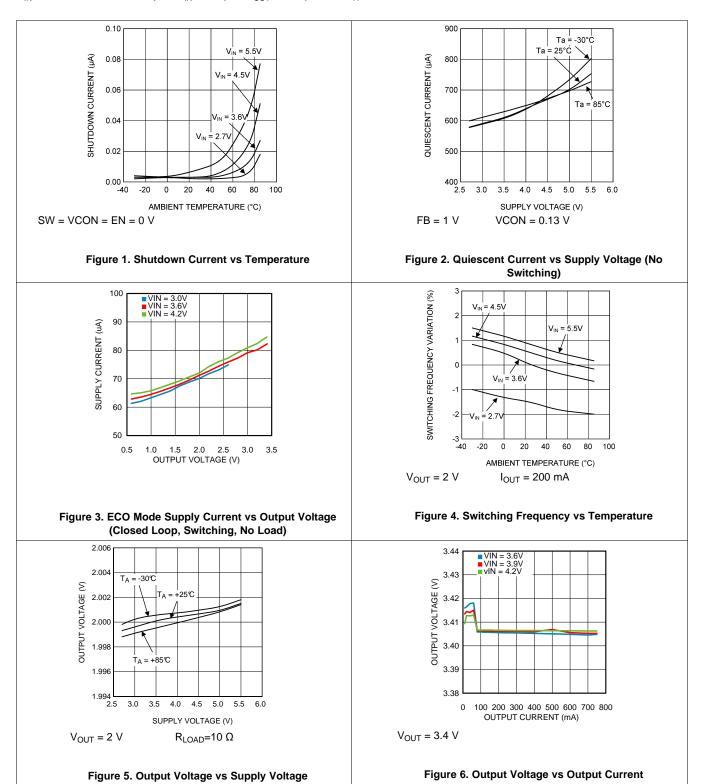

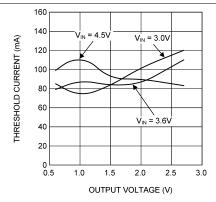

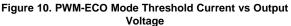

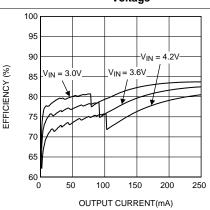

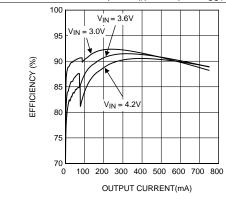

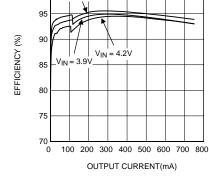

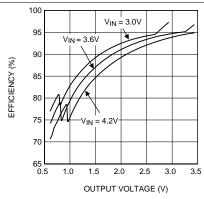

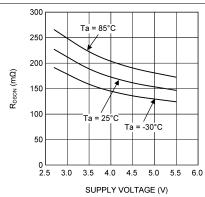

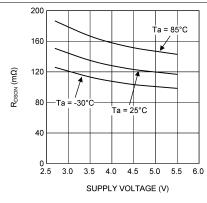

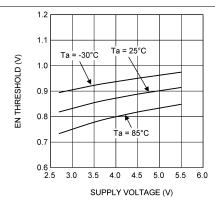

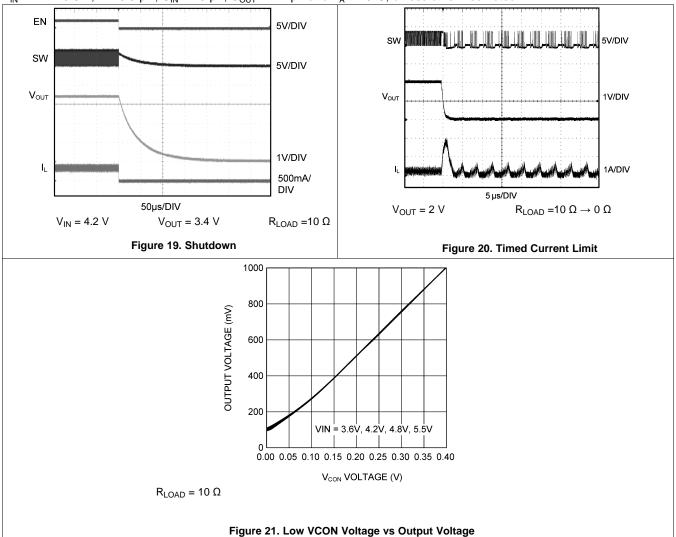

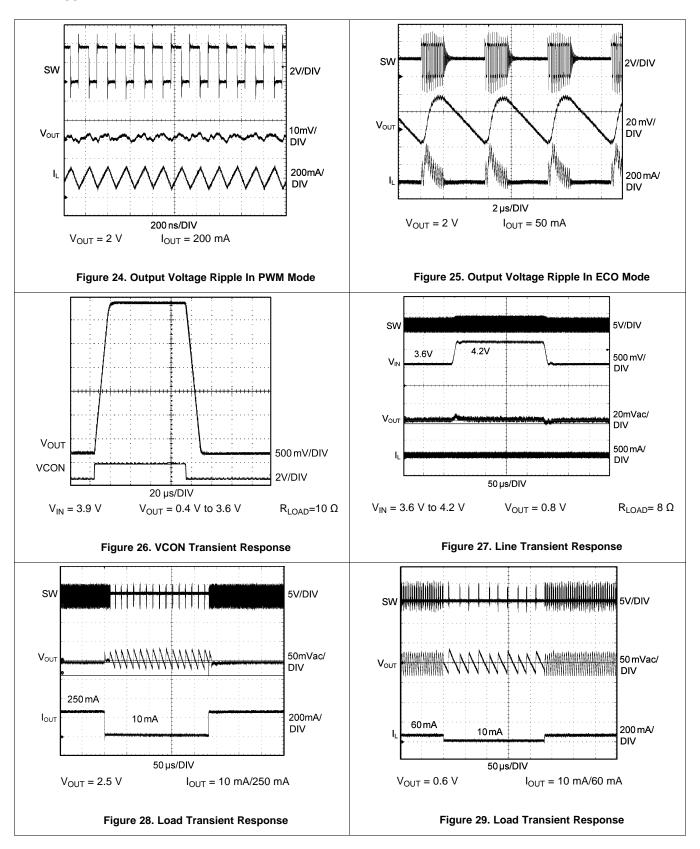

# 6.8 Typical Characteristics

$V_{IN}$  = EN = 3.6 V, L = 0.5  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 4.7  $\mu$ F and  $T_A$  = 25°C, unless otherwise noted.

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

$V_{IN}$  = EN = 3.6 V, L = 0.5  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 4.7  $\mu$ F and  $T_A$  = 25°C, unless otherwise noted.

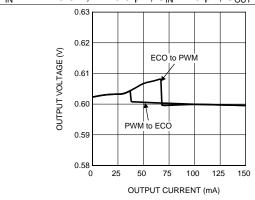

$V_{OUT} = 0.6 V$

2.02 ECO to PWM

2.01

2.00

1.99

1.98

2.5 50 75 100 125 150

OUTPUT CURRENT (mA)

$V_{OUT} = 2 V$

THRESHOLD CURRENT (mA)

160

140

120

100

80

60

40

20

1.0

1.5

Figure 7. Output Voltage vs Output Current

Figure 9. ECO-PWM Mode Threshold Current vs Output Voltage

2.0

OUTPUT VOLTAGE (V)

2.5

Figure 8. Output Voltage vs Output Current

$J_{IN} = 3.0 \text{V}$

3.0

Figure 11. Closed-Loop Current Limit vs Temperature

$V_{OUT} = 0.8 V$

Figure 12. Efficiency vs Output Current

# **Typical Characteristics (continued)**

$V_{IN}$  = EN = 3.6 V, L = 0.5  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 4.7  $\mu$ F and  $T_A$  = 25°C, unless otherwise noted.

$V_{OUT} = 2 V$

$V_{OUT} = 3.3 V$

Figure 13. Efficiency vs Output Current

$R_{LOAD} = 10 \Omega$

Figure 14. Efficiency vs Output Current

Figure 15. Efficiency vs Output Voltage

Figure 17. NFET R<sub>DSON</sub> vs Supply Voltage

Figure 16. PFET  $R_{DSON}$  vs Supply Voltage

Figure 18. EN High Threshold vs Supply Voltage

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

$V_{IN}$  = EN = 3.6 V, L = 0.5  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 4.7  $\mu$ F and  $T_A$  = 25°C, unless otherwise noted.

# 7 Detailed Description

#### 7.1 Overview

The LM3242 is a simple, step-down DC-DC converter optimized for powering RF power amplifiers (PAs) in mobile phones, portable communicators, and similar battery-powered RF devices. It is designed to allow the RF PA to operate at maximum efficiency over a wide range of power levels from a single Li-Ion battery cell. It is based on a voltage-mode buck architecture, with synchronous rectification for high efficiency. The device is designed for a maximum load capability of 750 mA in PWM mode. Maximum load range may vary from this depending on input voltage, output voltage, and the inductor chosen.

There are five modes of operation depending on the current required: PWM (Pulse Width Modulation), ECO (ECOnomy), BP (Bypass), Sleep, and Shutdown. (See Table 1.) The LM3242 operates in PWM mode at higher load current conditions. Lighter loads cause the device to automatically switch into ECO mode. Shutdown mode turns the device off and reduces battery consumption to 0.1 µA (typical).

DC PWM mode output voltage precision is  $\pm 2\%$  for 3.6 V<sub>OUT</sub>. Efficiency is typically around 95% (typical) for a 500-mA load with 3.3-V output, 3.9-V input. The output voltage is dynamically programmable from 0.4 V to 3.6 V by adjusting the voltage on the control pin (VCON) without the need for external feedback resistors. This ensures longer battery life by being able to change the PA supply voltage dynamically depending on its transmitting power.

Additional features include current overload protection and thermal overload shutdown.

The LM3242 is constructed using a chip-scale 9-bump DSBGA package. This package offers the smallest possible size, for space-critical applications such as cell phones, where board area is an important design consideration. Use of a high switching frequency (6 MHz, typical) reduces the size of external components. As shown in the Typical Application Circuit, only three external power components are required for implementation. Use of a DSBGA package requires special design considerations for implementation. (See *DSBGA Package Assembly and Use.*) Its fine bump-pitch requires careful board design and precision assembly equipment. Use of this package is best suited for opaque-case applications, where its edges are not subject to high-intensity ambient red or infrared light. Also, the system controller must set EN low during power-up and other low supply voltage conditions. (See *Shutdown Mode.*)

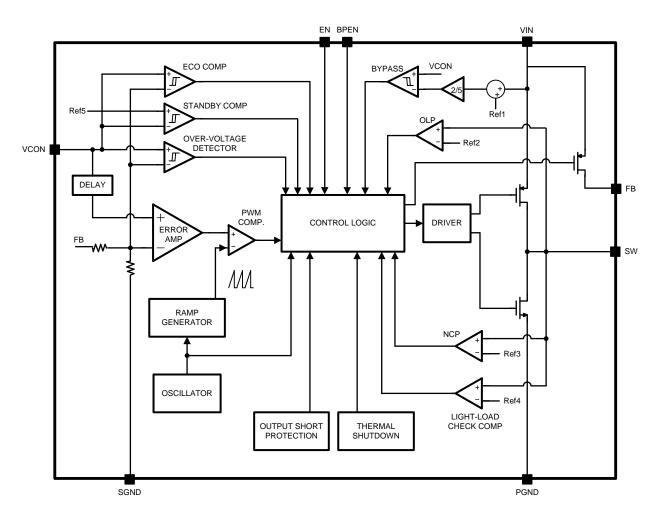

## 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Circuit Operation

Referring to the  $\# Z \cap R$  and Functional Block Diagram, the LM3242 operates as follows. During the first part of each switching cycle, the control block in the LM3242 turns on the internal top-side PFET switch. This allows current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of around  $(V_{IN}^- V_{OUT})$  / L, by storing energy in a magnetic field. During the second part of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the bottom-side NFET synchronous rectifier on. In response, the inductor's magnetic field collapses, generating a voltage that forces current from ground through the synchronous rectifier to the output filter capacitor and load. As the stored energy is transferred back into the circuit and depleted, the inductor current ramps down with a slope around  $V_{OUT}$  / L. The output filter capacitor stores charge when the inductor current is high, and releases it when low, smoothing the voltage across the load.

The output voltage is regulated by modulating the PFET switch on time to control the average current sent to the load. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at SW to a low-pass filter formed by the inductor and output filter capacitor. The output voltage is equal to the average voltage at the SW pin.

## **Feature Description (continued)**

## 7.3.2 Internal Synchronous Rectification

While in PWM mode, the LM3242 uses an internal NFET as a synchronous rectifier to reduce rectifier forward voltage drop and associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relatively low compared to the voltage drop across an ordinary rectifier diode.

With medium and heavy loads, the NFET synchronous rectifier is turned on during the inductor current down slope in the second part of each cycle. The synchronous rectifier is turned off prior to the next cycle. The NFET is designed to conduct through its intrinsic body diode during transient intervals before it turns on, eliminating the need for an external diode.

## 7.3.3 Current Limiting

The current limit feature allows the LM3242 to protect itself and external components during overload conditions. In PWM mode, the cycle-by-cycle current limit is a 1450 mA (typical). If an excessive load pulls the output voltage down to less than 0.3V (typical), the NFET synchronous rectifier is disabled and the current limit is reduced to 530 mA (typical). Moreover, when the output voltage becomes less than 0.15V (typical), the switching frequency decreases to 3 MHz, thereby preventing excess current and thermal stress.

## 7.3.4 Dynamically Adjustable Output Voltage

The LM3242 features dynamically adjustable output voltage to eliminate the need for external feedback resistors. The output can be set from 0.4 V to 3.6 V by changing the voltage on the analog VCON pin. This feature is useful in PA applications where peak power is needed only when the handset is far away from the base station or when data is being transmitted. In other instances the transmitting power can be reduced. Hence the supply voltage to the PA can be reduced, promoting longer battery life. See Setting The Output Voltage in Application and Implementation for further details. The LM3242 moves into pulse-skipping mode when duty cycle is over approximately 92% or less than approximately 15% and the output voltage ripple increases slightly.

#### 7.3.5 Thermal Overload Protection

The LM3242 has a thermal overload protection function that operates to protect itself from short-term misuse and overload conditions. When the junction temperature exceeds around 150°C, the device inhibits operation. Both the PFET and the NFET are turned off. When the temperature drops below 125°C, normal operation resumes. Prolonged operation in thermal overload conditions may damage the device and is considered bad practice.

## 7.3.6 Soft Start

The LM3242 has a soft-start circuit that limits in-rush current during start-up. During start-up the switch current limit is increased in steps. Soft start is activated if EN goes from low to high after V<sub>IN</sub> reaches 2.7V.

## 7.4 Device Functional Modes

**Table 1. Description Of Modes**

| MODE                         | EN | BPEN | VCON                                      | I <sub>OUT</sub> |

|------------------------------|----|------|-------------------------------------------|------------------|

| Shutdown                     | 0  | X    | X                                         | X                |

| Sleep                        | 1  | 0    | < 80 mV                                   | X                |

| Pulse Width Modulation (PWM) | 1  | 0    | . 120                                     | > 100 mA         |

| Economy (ECO)                | 1  | 0    | > 130 mV, < (V <sub>IN</sub> - 0.2 V)/2.5 | < 50 mA          |

| Bypass (BP)                  | 1  | 0    | > (V <sub>IN</sub> - 0.2 V)/2.5           | X                |

|                              | 1  | 1    | X                                         | X                |

## 7.4.1 PWM Mode Operation

While in PWM mode operation, the converter operates as a voltage-mode controller with input voltage feedforward. This allows the converter to achieve excellent load and line regulation. The DC gain of the power stage is proportional to the input voltage. To eliminate this dependence, feed forward inversely proportional to the input voltage is introduced. While in PWM mode, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control power to the load. At the beginning of each clock cycle the PFET switch is turned on and the inductor current ramps up until the comparator trips and the control logic turns off the switch. The current limit comparator can also turn off the switch in case the current limit of the PFET is exceeded. Then the NFET switch is turned on and the inductor current ramps down. The next cycle is initiated by the clock turning off the NFET and turning on the PFET.

## 7.4.2 Bypass Mode Operation

The LM3242 contains an internal BPFET switch for bypassing the PWM DC-DC converter during Bypass mode. In Bypass mode, this BPFET is turned on to power the PA directly from the battery for maximum RF output power. When the part operates in the Bypass mode, the output voltage is the input voltage less the voltage drop across the resistance of the BPFET in parallel with the PFET + Switch Inductor. Bypass mode is more efficient than operating in PWM mode at 100% duty cycle because the combined resistance is significantly less than the series resistance of the PWM PFET and inductor. This translates into higher voltage available on the output in Bypass mode, for a given battery voltage. The part can be set to bypass mode by sending BPEN pin high. This is called Forced Bypass Mode and it remains in bypass mode until BPEN pin goes low. Alternatively the part can go into Bypass mode automatically. This is called Auto-Bypass mode or Automatic Bypass mode. The bypass switch turns on when the difference between the input voltage and programmed output voltage is less than 200 mV (typical) for longer than 10 μs (typical). The bypass switch turns off when the input voltage is higher than the programmed output voltage by 250 mV (typical) for longer than 0.1 μs (typical). This method is very system resource friendly in that the Bypass PFET is turned on automatically when the input voltage gets close to the output voltage, a typical scenario of a discharging battery. It is also turned off automatically when the input voltage rises, a typical scenario when connecting a charger. When V<sub>OLIT</sub> < 300 mV, BPEN is ignored.

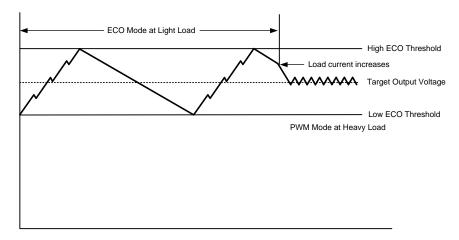

## 7.4.3 ECO Mode Operation

At very light loads (50 mA to 100 mA), the LM3242 enters ECO mode operation with reduced switching frequency and supply current to maintain high efficiency. During ECO mode operation, the LM3242 positions the output voltage slightly higher (7 mV typical) than the normal output voltage during PWM mode operation, allowing additional headroom for voltage drop during a load transient from light to heavy load.

Figure 22. Operation In ECO Mode and Transfer to PWM Mode

## 7.4.4 Sleep Mode Operation

When VCON is less than 80 mV in 10  $\mu$ s, the LM3242 goes into SLEEP mode — the SW pin is in Tri-state (floating), which operates like ECO mode with no switching. The LM3242 device returns to normal operation immediately when VCON  $\geq$  130 mV in PWM mode or ECO mode, depending on load detection.

#### 7.4.5 Shutdown Mode

Setting the EN digital pin low (< 0.4 V) places the LM3242 in Shutdown mode (0.1  $\mu$ A typical). During shutdown, the PFET switch, the NFET synchronous rectifier, reference voltage source, control and bias circuitry of the LM3242 are turned off. Setting EN high (> 1.2 V) enables normal operation. EN must be set low to turn off the LM3242 during power-up and undervoltage conditions when the power supply is less than the 2.7V minimum operating voltage. The LM3242 has an undervoltage lock-out (UVLO) comparator to turn the power device off in the case the input voltage or battery voltage is too low. The typical UVLO threshold is around 2 V for lock and 2.1 V for release.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

## 8.1.1 Setting The Output Voltage

The LM3242 features a pin-controlled adjustable output voltage to eliminate the need for external feedback resistors. It can be programmed for an output voltage from 0.4 V to 3.6 V by setting the voltage on the VCON pin, as in Equation 1:

$$V_{OUT} = 2.5 \times VCON$$

(1)

When VCON is between 0.16 V and 1.44 V, the output voltage will follow proportionally by 2.5 times of VCON.

If VCON is less than 0.16 V ( $V_{OUT} = 0.4$  V), the output voltage may not be well regulated. Refer to Figure 21 for more detail. This curve exhibits the characteristics of a typical part, and the performance cannot be ensured as there could be a part-to-part variation for output voltages less than 0.4 V. For  $V_{OUT}$  lower than 0.4 V, the converter might suffer from larger output ripple voltage and higher current limit operation.

#### 8.1.2 FB

Typically the FB pin is connected to V<sub>OUT</sub> for regulating the output voltage maximum of 3.6 V.

# 8.2 Typical Application

Figure 23. LM3242 Typical Application

# **Typical Application (continued)**

## 8.2.1 Design Requirements

For typical step-down DC-DC applications, use the parameters listed in Table 2.

**Table 2. Design Parameters**

| DESIGN PARAMETER       | EXAMPLE VALUE   |  |

|------------------------|-----------------|--|

| Minimum input voltage  | 2.7 V           |  |

| Minimum output voltage | 0.4 V           |  |

| Output current         | 0 to 750 mA     |  |

| Switching frequency    | 6 MHz (typical) |  |

## 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Inductor Selection

There are two main considerations when choosing an inductor; the inductor must not saturate, and the inductor current ripple is small enough to achieve the desired output voltage ripple. Different manufacturers follow different saturation current rating specifications, so attention must be given to details. Saturation current ratings are typically specified at 25°C so ratings over the ambient temperature of application should be requested from manufacturer.

Minimum value of inductance to ensure good performance is  $0.3~\mu H$  at bias current ( $I_{LIM}$  (typical)) over the ambient temperature range. Shielded inductors radiate less noise and are preferred. There are two methods to choose the inductor saturation current rating:

#### 8.2.2.1.1 Method 1

The saturation current must be greater than the sum of the maximum load current and the worst-case averageto-peak inductor current. This can be written as:

$$\begin{split} I_{SAT} > I_{OUT\_MAX} + I_{RIPPLE} \\ \text{where} \\ I_{RIPPLE} = \left( \frac{V_{IN} - V_{OUT}}{2 \text{ x L}} \right) x \left( \frac{V_{OUT}}{V_{IN}} \right) x \left( \frac{1}{f} \right) \end{split}$$

#### where

- I<sub>RIPPLE</sub>: average-to-peak inductor current

- I<sub>OUT MAX</sub>: maximum load current (750 mA)

- V<sub>IN</sub>: maximum input voltage in application

- L minimum inductor value including worst-case tolerances (30% drop can be considered for Method 1)

- F: minimum switching frequency (5.7 MHz)

- V<sub>OUT</sub>: output voltage (2)

#### 8.2.2.1.2 Method 2

A more conservative and recommended approach is to choose an inductor that can handle the maximum current limit of 1600 mA.

The resistance of the inductor must be less than approximately 0.1  $\Omega$  for good efficiency. Table 3 lists suggested inductors and suppliers.

**Table 3. Suggested Inductors**

| MODEL         | SIZE (W × L × H) (mm) | VENDOR      |

|---------------|-----------------------|-------------|

| MIPSZ2012D0R5 | 2 × 1.2 × 1           | FDK         |

| LQM21PNR54MG0 | 2 × 1.25 × 0.9        | Murata      |

| LQM2MPNR47NG0 | 2 × 1.6 × 0.9         | Murata      |

| CIG21LR47M    | 2 × 1.25 × 1          | Samsung     |

| CKP2012NR47M  | 2 × 1.25 × 1          | Taiyo Yuden |

## 8.2.2.2 Capacitor Selection

The LM3242 is designed for use with ceramic capacitors for its input and output filters. Use a  $10-\mu F$  ceramic capacitor for input and a sum total of  $4.7-\mu F$  ceramic capacitors for the output. They must maintain at least 50% capacitance at DC bias and temperature conditions. Ceramic capacitors types such as X5R, X7R, and B are recommended for both filters. These provide an optimal balance between small size, cost, reliability and performance for cell phones and similar applications. Table 4 lists some suggested part numbers and suppliers. DC bias characteristics of the capacitors must be considered when selecting the voltage rating and case size of the capacitor. If it is necessary to choose a 0603 (1608) size capacitor for  $V_{IN}$  and 0402 (1005) size capacitor for  $V_{OUT}$ , the operation of the LM3242 must be carefully evaluated on the system board. Use of a  $2.2-\mu F$  capacitor in conjunction with multiple  $0.47~\mu F$  or  $1~\mu F$  capacitors in parallel may also be considered when connecting to power amplifier devices that require local decoupling.

**Table 4. Suggested Capacitors and Their Suppliers**

|             |                 | • •               |         |

|-------------|-----------------|-------------------|---------|

| CAPACITANCE | MODEL           | SIZE (W × L) (mm) | VENDOR  |

| 2.2 µF      | GRM155R60J225M  | 1 × 0.5           | Murata  |

| 2.2 µF      | C1005X5R0J225M  | 1 × 0.5           | TDK     |

| 2.2 µF      | CL05A225MQ5NSNC | 1 × 0.5           | Samsung |

| 4.7 µF      | C1608JB0J475M   | 1.6 × 0.8         | TDK     |

| 4.7 µF      | C1005X5R0J475M  | 1 × 0.5           | TDK     |

| 4.7 µF      | CL05A475MQ5NRNC | 1 × 0.5           | Samsung |

| 10 μF       | C1608X5R0J106M  | 1.6 × 0.8         | TDK     |

| 10 μF       | GRM155R60J106M  | 1 × 0.5           | Murata  |

| 10 μF       | CL05A106MQ5NUNC | 1 × 0.5           | Samsung |

The input filter capacitor supplies AC current drawn by the PFET switch of the LM3242 in the first part of each cycle and reduces the voltage ripple imposed on the input power source. The output filter capacitor absorbs the AC inductor current, helps maintain a steady output voltage during transient load changes and reduces output voltage ripple. These capacitors must be selected with sufficient capacitance and sufficiently low Equivalent Series Resistance (ESR) to perform these functions. The ESR of the filter capacitors is generally a major factor in voltage ripple.

## 8.2.3 Application Curves

# 9 Power Supply Recommendations

The LM3242 device is designed to operate from an input voltage supply range between 2.7 V and 5.5 V. This input supply must be well regulated.

# 10 Layout

## 10.1 Layout Guidelines

PC board layout is critical to successfully designing a DC-DC converter into a product. As much as a 20-dB improvement in RX noise floor can be achieved by carefully following recommended layout practices. A properly planned board layout optimizes the performance of a DC-DC converter and minimizes effects on surrounding circuitry while also addressing manufacturing issues that can have adverse impacts on board quality and final product yield.

#### 10.1.1 PCB Considerations

Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss in the traces. Erroneous signals could be sent to the DC-DC converter device, resulting in poor regulation or instability. Poor layout can also result in re-flow problems leading to poor solder joints between the DSBGA package and board pads. Poor solder joints can result in erratic or degraded performance of the converter.

## 10.1.1.1 Energy Efficiency

Minimize resistive losses by using wide traces between the power components and doubling up traces on multiple layers when possible.

#### 10.1.1.2 EMI

By its very nature, any switching converter generates electrical noise, and the circuit board designer's challenge is to minimize, contain, or attenuate such switcher-generated noise. A high-frequency switching converter, such as the LM3242, switches Ampere level currents within nanoseconds, and the traces interconnecting the associated components can act as radiating antennas. The following guidelines are offered to help to ensure that EMI is maintained within tolerable levels.

To minimize radiated noise:

- Place the LM3242 switcher, its input capacitor, and output filter inductor and capacitor close together, and make the interconnecting traces as short as possible.

- Arrange the components so that the switching current loops curl in the same direction. During the first half of

each cycle, current flows from the input filter capacitor, through the internal PFET of the LM3242 and the

inductor, to the output filter capacitor, then back through ground, forming a current loop. In the second half of

each cycle, current is pulled up from ground, through the internal synchronous NFET of the LM3242 by the

inductor, to the output filter capacitor and then back through ground, forming a second current loop. Routing

these loops so the current curls in the same direction prevents magnetic field reversal between the two halfcycles and reduces radiated noise.

- Make the current loop area(s) as small as possible.

To minimize ground-plane noise:

Reduce the amount of switching current that circulates through the ground plane: Connect the ground bumps

of the LM3242 and its input filter capacitor together using generous component-side copper fill as a pseudoground plane. Then connect this copper fill to the system ground-plane (if one is used) with multiple vias.

These multiple vias help to minimize ground bounce at the LM3242 by giving it a low-impedance ground

connection.

To minimize coupling to the DC-DC converter's own voltage feedback trace:

Route noise sensitive traces, such as the voltage feedback path, as directly as possible from the switcher FB

pad to the VOUT pad of the output capacitor, but keep it away from noisy traces between the power

components.

To decouple common power supply lines, series impedances may be used to strategically isolate circuits:

- Take advantage of the inherent inductance of circuit traces to reduce coupling among function blocks, by way

of the power supply traces.

- Use star connection for separately routing VBATT to PVIN and VBATT PA.

- Inserting a single ferrite bead in-line with a power supply trace may offer a favorable tradeoff in terms of board area, by allowing the use of fewer bypass capacitors.

## **Layout Guidelines (continued)**

## 10.1.2 Manufacturing Considerations

The LM3242 package employs a 9-pin (3 mm  $\times$  3 mm) array of 250 micron solder balls, with a 0.4-mm pad pitch. A few simple design rules go a long way to ensuring a good layout.

- Pad size must be  $0.225 \pm 0.02$  mm. Solder mask opening must be  $0.325 \pm 0.02$  mm.

- As a thermal relief, connect to each pad with 7 mil wide, 7 mil long traces, and incrementally increase each

trace to its optimal width. Symmetry is important to ensure the solder bumps re-flow evenly (refer to TI

Application Note AN-1112 DSBGA Wafer Level Chip Scale Package (SNVA009).

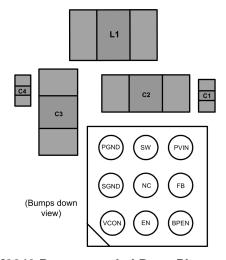

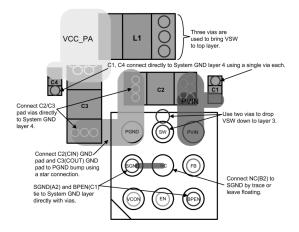

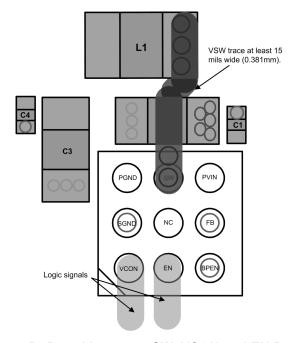

#### 10.1.3 LM3242 Evaluation Board

The following figures are drawn from a 4-layer board design, with notes added to highlight specific details of the DC-DC switching converter section.

Figure 31. Simplified LM3242 RF Evaluation Board Schematic

- 1. Bulk Input Capacitor C2 must be placed closer to LM3242 than C1.

- 2. Add a 1nF (C1) on input of LM3242 for high frequency filtering.

- 3. Bulk Output Capacitor C3 must be placed closer to LM3242 than C4.

- 4. Add a 1nF (C4) on output of LM3242 for high frequency filtering.

- 5. Connect both GND terminals of C1 and C4 directly to System GND layer of phone board.

- 6. Connect bumps SGND (A2), NC (B2), BPEN (C1) directly to System GND.

- 7. Use 0402 caps for both C2 and C3 due to better high frequency filtering characteristics over 0603 capacitors.

- 8. TI has seen some improvement in high frequency filtering for small bypass caps (C1 and C4) when they are connected to System GND instead of same ground as PGND. These capacitors must be 01005 case size for minimum footprint and best high frequency characteristics.

Figure 32. LM3242 Recommended Parts Placement (Top View)

## **Layout Guidelines (continued)**

## 10.1.3.1 Component Placement

## PVIN

1. Use a star connection from PVIN to LM3242 and PVIN to PA VBATT connection ( $V_{CC1}$ ). Do not daisy-chain PVIN connection to LM3242 circuit and then to PA device PVIN connection.

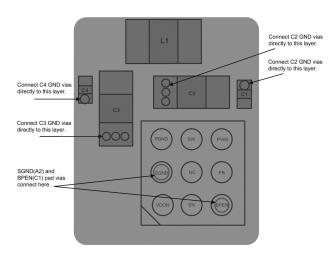

#### TOP LAYER

- 1. Place a via in LM3242 SGND(A2), BPEN(C1) pads to drop and connect directly to System GND Layer 4.

- 2. Place two vias at LM3242 SW solder bump to drop VSW trace to Layer 3.

- 3. Connect C2 and C3 capacitor GND pads to PGND bump on LM3242 using a star connection. Place vias in C2 and C3 GND pads that connect directly to System GND Layer 4.

- 4. Add 01005/0201 capacitor footprints (C1, C4) to input/output of LM3242 for improved high frequency filtering. C1 and C4 GND pads connect directly to System GND Layer 4.

- 5. Place three vias at L1 inductor pad to bring up VSW trace from Layer 3 to top Layer.

#### LAYER 2

- 1. Make FB trace at least 10 mils (0.254 mm) wide.

- 2. Isolate FB trace away from noisy nodes and connect directly to C3 output capacitor. Place a via in LM3242 SGND(A2), BPEN(C1) pads to drop and connect directly to System GND Layer 4.

#### LAYER 3

- 1. Make VSW trace at least 15 mils (0.381 mm) wide.

- LAYER 4 (System GND

- 1. Connect C2 and C3 PGND vias to this layer.

- 2. Connect C1 and C4 GND vias to this layer.

- 3. Connect LM3242 SGND(A2), BPEN(C1), NC(B2) pad vias to this layer.

## 10.2 Layout Examples

Figure 33. Board Layer 1 – PVIN and PGND Routing

# **Layout Examples (continued)**

Figure 34. Board Layer 2 – FB and PVIN Routing

Figure 35. Board Layer 3 - SW, VCON and EN Routing

## **Layout Examples (continued)**

Figure 36. Board Layer 4 - System GND Plane

## 10.3 DSBGA Package Assembly and Use

Use of the DSBGA package requires specialized board layout, precision mounting and careful re-flow techniques, as detailed in Texas Instruments Application Note 1112. Refer to the section *Surface Mount Assembly Considerations*. For best results in assembly, alignment ordinals on the PC board must be used to facilitate placement of the device. The pad style used with DSBGA package must be the NSMD (non-solder mask defined) type. This means that the solder-mask opening is larger than the pad size. This prevents a lip that otherwise forms if the solder-mask and pad overlap, from holding the device off the surface of the board and interfering with mounting. See SNVA009 for specific instructions how to do this.

The 9-bump package used for LM3242 has 250-micron solder balls and requires 0.225-mm pads for mounting on the circuit board. The trace to each pad must enter the pad with a 90°angle to prevent debris from being caught in deep corners. Initially, the trace to each pad must be 7 mil wide, for a section approximately 7 mil long, as a thermal relief. Then each trace must neck up or down to its optimal width. The important criterion is symmetry. This ensures the solder bumps on the LM3242 re-flow evenly and that the device solders level to the board. In particular, special attention must be paid to the pads for bumps A3 and C3. Because VIN and GND are typically connected to large copper planes, inadequate thermal reliefs can result in late or inadequate re-flow of these bumps.

The DSBGA package is optimized for the smallest possible size in applications with red or infrared opaque cases. Because the DSBGA package lacks the plastic encapsulation characteristic of larger devices, it is vulnerable to light. Backside metallization and/or epoxy coating, along with front-side shading by the printed circuit board, reduce this sensitivity. However, the package has exposed die edges. In particular, DSBGA devices are sensitive to light, in the red and infrared range, shining on the package's exposed die edges.

Adding a 10-nF capacitor between VCON and ground is recommended for non-standard ESD events or environments and manufacturing processes. It prevents unexpected output voltage drift.

## 11 器件和文档支持

## 11.1 器件支持

## 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

## 11.2 文档支持

#### 11.2.1 相关文档

更多信息,请参见以下文档:

德州仪器 (TI) 应用手册 AN-1112 《DSBGA 晶圆级芯片规模封装》(文献编号: SNVA009)。

#### 11.3 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 要获得这份数据表的浏览器版本,请查阅左侧的导航栏。

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| LM3242TME/NOPB   | ACTIVE | DSBGA        | YFQ                | 9    | 250            | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -30 to 90    | SN                      | Samples |

| LM3242TMX/NOPB   | ACTIVE | DSBGA        | YFQ                | 9    | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -30 to 90    | SN                      | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

www.ti.com 21-Oct-2021

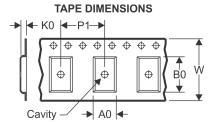

# TAPE AND REEL INFORMATION

| _ |    |                                                           |

|---|----|-----------------------------------------------------------|

|   |    | Dimension designed to accommodate the component width     |

|   | В0 | Dimension designed to accommodate the component length    |

|   | K0 | Dimension designed to accommodate the component thickness |

|   | W  | Overall width of the carrier tape                         |

| ı | P1 | Pitch between successive cavity centers                   |

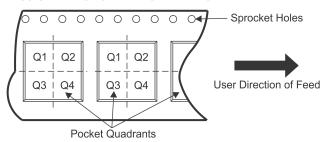

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3242TME/NOPB | DSBGA           | YFQ                | 9 | 250  | 178.0                    | 8.4                      | 1.57       | 1.57       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3242TMX/NOPB | DSBGA           | YFQ                | 9 | 3000 | 178.0                    | 8.4                      | 1.57       | 1.57       | 0.76       | 4.0        | 8.0       | Q1               |

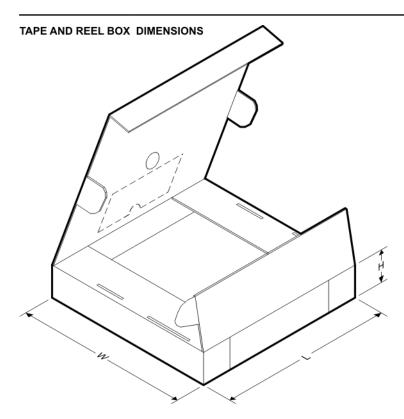

www.ti.com 21-Oct-2021

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM3242TME/NOPB | DSBGA        | YFQ             | 9    | 250  | 208.0       | 191.0      | 35.0        |

| LM3242TMX/NOPB | DSBGA        | YFQ             | 9    | 3000 | 208.0       | 191.0      | 35.0        |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司