ZHCSBI2-JANUARY 2013

# 4MHz,高电流闪光发光二极管 (LED) 驱动器

查询样品: LM3565

## 特性

- 高效同步升压转换器

- 以高达 930mA 的电流驱动器 2 个串联的 LED

- 针对硬件使能闪光的外部选通脉冲引脚

- 针对硬件使能电筒的外部 Torch 引脚

- 专用传输中断引脚

- 针对 LED 电压和输入电压监视的 8 位模数转换器 (ADC)

- 自动二极管电流回落

- 闪光和辅助模式中的脉宽调制 (PWM) 控制

- 故障检测和报告

- 400kHz I<sup>2</sup>C 兼容接口

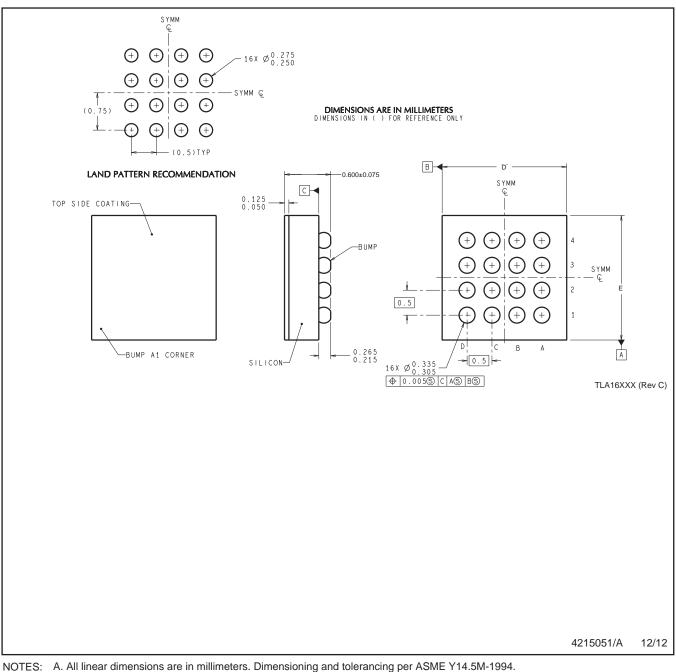

- 16 焊锡凸点, 1.990mm x 1.990mm x 0.6mm 芯 片级球栅阵列 (DSBGA) 封装 (YZR0016AAA)

## 应用范围

• 可拍照手机 LED 闪光灯

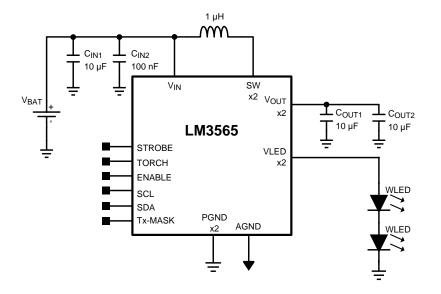

#### 典型应用电路

#### 说明

LM3565 是一款 4MHz 定频、电流模式同步升压转换器,此转换器被设计成以 930mA 的电流驱动两个串联闪光 LED。一个高压电流源使得 LED 能够被端接至接地层,从而免除了对于返回至集成电路 (IC) 的额外返回迹线的需要。

一个专用选通脉冲引脚提供了一个直接接口来触发闪光 事件,与此同时,一个外部 Torch 引脚提供了一个在 恒定电流模式中启用 LED 的额外方法。LM3565 能够 根据测得的输入电压来自适应地提升传送至 LED 的最 大闪光电平。

LM3565 上提供从过压保护到输出短路检测的多重保护特性。

LM3565 具有四个可选电感器电流限值,以帮助用户选择一个适合于此设计的电感器。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Ā

## LM3565

Г

#### ZHCSBI2-JANUARY 2013

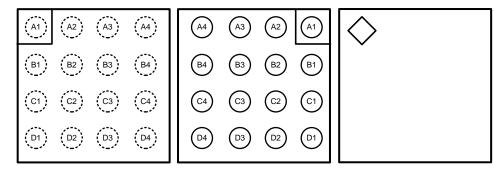

## **CONNECTION DIAGRAM**

TOP VIEW (BUMPS FACE DOWN)

Т

BOTTOM VIEW (BUMPS FACE UP) PIN A1 LOCATION

#### **PIN FUNCTIONS**

|     | PIN     | INPUT/OUTPUT | DESCRIPTION                                                                                                                                  |

|-----|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME    | (I/O)        | DESCRIPTION                                                                                                                                  |

| A1  | PGND    |              | Power GND.                                                                                                                                   |

| A2  | PGND    |              | Power GND.                                                                                                                                   |

| A3  | VIN     | I            | Input voltage pin of the device. Connect input bypass capacitor very close to this pin.                                                      |

| A4  | ENABLE  | I            | Chip Enable. High = Standby, Low = Shutdown.                                                                                                 |

| B1  | SW1     | I            | Inductor connection.                                                                                                                         |

| B2  | SW2     | I            | Inductor connection.                                                                                                                         |

| B3  | TORCH   | I            | Hardware Torch Enable Pin.                                                                                                                   |

| B4  | TX-MASK | I            | Hardware Transmit Interrupt Pin.                                                                                                             |

| C1  | VOUT1   | 0            | Boost output. Connect output bypass capacitor very close to this pin.                                                                        |

| C2  | VOUT2   | 0            | Boost output. Tie to VOUT1.                                                                                                                  |

| C3  | STROBE  | I            | Strobe signal input pin to synchronize flash pulse in I <sup>2</sup> C-compatible mode. This signal usually comes from the camera processor. |

| C4  | SDA     | I/O          | Serial Data Pin for I <sup>2</sup> C-compatible Interface.                                                                                   |

| D1  | LEDOUT1 | I/O          | LED Current Source Output.                                                                                                                   |

| D2  | LEDOUT2 | I/O          | LED Current Source Output. Tie to LEDOUT1.                                                                                                   |

| D3  | AGND    |              | A/D Ground Pin.                                                                                                                              |

| D4  | SCL     | I            | Serial Clock Pin for I <sup>2</sup> C-compatible Interface.                                                                                  |

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

|                    |                                                     | VAL        | UE                              | UNIT |  |

|--------------------|-----------------------------------------------------|------------|---------------------------------|------|--|

|                    |                                                     | MIN MAX    |                                 | UNIT |  |

|                    | VIN                                                 | -0.3       | +6                              | V    |  |

|                    | TORCH, TX-MASK, STROBE, ENABLE, SDA, SCL            | -0.3       | (V <sub>IN</sub> +0.3V)<br>+6.0 | V    |  |

|                    | VOUT1, VOUT2, LEDOUT1, LEDOUT2, SW1, SW2            |            | +10                             | V    |  |

|                    | Continuous power dissipation <sup>(3)</sup>         | Internally | Limited                         |      |  |

| T <sub>J-MAX</sub> | Junction temperature                                |            | +150                            | °C   |  |

|                    | Storage temperature range                           | -55        | +150                            | °C   |  |

|                    | Maximum lead temperature (soldering) <sup>(4)</sup> | i.         |                                 |      |  |

|                    | ESD rating, Human Body Model                        |            | +2.5                            | kV   |  |

Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability..

All voltages are with respect to the potential at the GND pin.

(2) All voltages are with respect to the potential at the GND pill.

(3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typ.) and disengages at T<sub>J</sub> = 115°C (typ). Thermal shutdown is specified by design.

(4) For detailed soldering specifications and information, refer to Texas Instruments Application Note: AN-1112: DSBGA Wafer Level Chip Scale Package for Recommended Soldering Profiles.

### **RECOMMENDED OPERATING CONDITIONS**<sup>(1)(2)</sup>

|                |                                                       | MIN  | NOM | MAX   | UNIT |

|----------------|-------------------------------------------------------|------|-----|-------|------|

|                | Input voltage range                                   | +2.5 |     | +5.5  | V    |

|                | Output voltage range                                  | +5.5 |     | +8.5  | V    |

| $T_{J}$        | Junction temperature range                            | -30  |     | +125  | °C   |

| T <sub>A</sub> | Ambient temperature range <sup>(3)</sup>              | -30  |     | +85   | °C   |

| THER           | MAL PROPERTIES                                        |      |     |       |      |

| $\theta_{JA}$  | Thermal resistance junction-to-ambient <sup>(4)</sup> |      |     | +62.2 | °C/W |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages are with respect to the potential at the GND pin.

- (3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

- (4) Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 102 mm x 76 mm x 1.6 mm with a 2x1 array of thermal vias. The ground plane on the board is 50 mm x 50 mm. Thickness of copper layers are 36 μm/18 μm/18 μm/3 μm (1.5 oz/1 oz/1 oz/1.5 oz). Ambient temperature in simulation is 22°C, still air. Power dissipation is 1.2W.

## **ELECTRICAL CHARACTERISTICS**

Limits in standard typeface are for  $T_A = +25^{\circ}$ C. Limits in **boldface type** apply over the full operating ambient temperature range ( $-30^{\circ}$ C  $\leq T_A \leq 85^{\circ}$ C). Unless otherwise specified: 2.7V  $\leq V_{IN} \leq 4.4$ V. <sup>(1)(2)</sup>

| PARAMETER             |                                                                                   | TEST C                                            | MIN                                  | TYP          | MAX  | UNIT         |      |

|-----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------|--------------|------|--------------|------|

| CURRENT               | AND VOLTAGE SPECIFICATIONS                                                        |                                                   |                                      |              |      |              |      |

| I <sub>LED-OUT</sub>  | LED Current accuracy                                                              | V <sub>OUT</sub> =7.5V<br>V <sub>LED</sub> = 7.2V | 60 mA ≤ IL <sub>ED</sub> ≤<br>930 mA | (–5%)        |      | (+5%)        |      |

| V <sub>CSH</sub>      | Current source headroom voltage                                                   |                                                   |                                      |              | 300  | 350          | mV   |

| V <sub>OVP</sub>      | Over-voltage protection range                                                     | Trip Point (Rising                                | )                                    | 9.0          | 9.5  | 10.0         | V    |

| I <sub>SD</sub>       | Shutdown current                                                                  |                                                   |                                      |              |      | 1            | μA   |

| I <sub>SB</sub>       | Standby current                                                                   |                                                   |                                      |              |      | 1            | μA   |

| l <sub>Q</sub>        | Operating quiescent current                                                       | Part switching                                    |                                      |              | 10   |              | mA   |

| UVLO                  | Under-voltage lock out                                                            | Falling V <sub>IN</sub>                           |                                      | 2.3          | 2.4  | 2.5          | V    |

| UVLO <sub>HYST</sub>  | UVLO Hysteresis                                                                   | Rising VIN                                        |                                      | 50           | 100  | 150          | mV   |

|                       |                                                                                   | CL Reg value = 0                                  | 00                                   | 2.07         | 2.3  | 2.53         |      |

|                       |                                                                                   | CL Reg value = 0                                  | )1                                   | 2.34         | 2.6  | 2.86         |      |

| I <sub>LIM</sub>      | Peak current limit                                                                | CL Reg value = 1                                  | 2.61                                 | 2.9          | 3.19 | A            |      |

|                       |                                                                                   | CL Reg value = 1                                  | <b>2.97</b> 3                        | 3.3          | 3.63 |              |      |

| R <sub>DSON_N</sub>   | NFET pin-to-pin Resistance                                                        |                                                   |                                      |              | 88   |              | mΩ   |

| R <sub>DSON P</sub>   | PFET pin-to-pin Resistance                                                        |                                                   |                                      |              | 110  |              | mΩ   |

| OSCILLAT              | OR AND TIMING SPECIFICATIONS (NON-I <sup>2</sup>                                  | C-COMPATIBLE II                                   | NTERFACE TIMING)                     | I            | 1    | 1            |      |

| f <sub>SW</sub>       | Switching frequency                                                               |                                                   |                                      | 3.8<br>(–5%) | 4.0  | 4.2<br>(+5%) | MHz  |

| t <sub>R-STEP</sub>   | LED current ramp up and down                                                      |                                                   |                                      |              | 20   |              | µsec |

| t <sub>RU</sub>       | Current ramp up time                                                              | From end of Com<br>Fullscale                      | imand to I <sub>LED</sub> =          |              | 1.4  |              | msec |

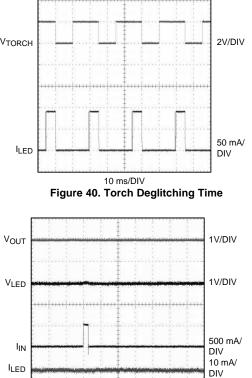

| t <sub>TORCH-DG</sub> | Torch deglitching time                                                            |                                                   |                                      | 6.3          | 9    | 11.7         | msec |

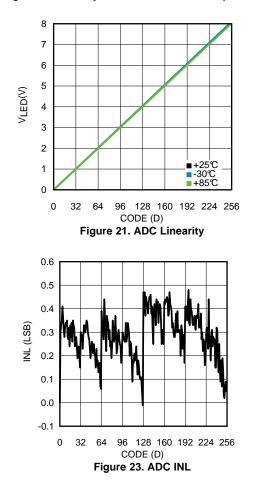

| ANALOG-T              | O-DIGITAL (A/D) CONVERTER SPECIFICAT                                              | IONS                                              |                                      | I            | 1    | 1            |      |

| ADCRES                | A/D Resolution                                                                    | Average step size                                 | 9                                    |              | 31.4 | 50           | mV   |

| VOFF                  | Offset error                                                                      |                                                   |                                      |              |      | 1            | Bits |

| GE                    | Gain error                                                                        | $V_{LED} = 8 V$                                   |                                      | (–2%)        |      | (+2%)        |      |

| CONTROL               | INTERFACE VOLTAGE SPECIFICATIONS                                                  | •                                                 |                                      |              | ł    | +            |      |

| V <sub>IL</sub>       | Low-level threshold voltage (SCL SDA,<br>ENABLE, TX-MASK, TORCH)                  |                                                   |                                      |              |      | 0.54         | V    |

| V <sub>IH</sub>       | High-level threshold voltage (SCL SDA,<br>ENABLE, TX-MASK, TORCH, STROBE<br>1.8V) |                                                   |                                      | 1.26         |      |              | V    |

| V <sub>OL</sub>       | Low-level output threshold limit (SDA)                                            | $I_{LOAD} = 3 \text{ mA}$                         |                                      |              |      | 0.4          | V    |

| V <sub>IL</sub>       | Low-level threshold voltage (STROBE 1.2V)                                         |                                                   |                                      |              |      | 0.36         | V    |

| V <sub>IH</sub>       | High-level threshold voltage (STROBE 1.2V)                                        |                                                   |                                      | 0.84         |      |              | V    |

(1) Min and Max limits are specified by design, test, or statistical analysis. Typical (Typ) numbers are **not** verified, but do represent the most likely norm. Unless otherwise specified, conditions for Typical specifications are:  $V_{IN} = 3.6V$  and  $T_A = 25^{\circ}C$ .

(2) Switching disabled.

#### ZHCSBI2-JANUARY 2013

## **ELECTRICAL CHARACTERISTICS (continued)**

Limits in standard typeface are for  $T_A = +25^{\circ}$ C. Limits in **boldface type** apply over the full operating ambient temperature range ( $-30^{\circ}$ C  $\leq T_A \leq 85^{\circ}$ C). Unless otherwise specified: 2.7V  $\leq V_{IN} \leq 4.4$ V. <sup>(1)(2)</sup>

|                        | PARAMETER                                      | TEST CONDITIONS                | MIN                       | TYP | MAX | UNIT |  |

|------------------------|------------------------------------------------|--------------------------------|---------------------------|-----|-----|------|--|

| CONTROL                | CONTROL INTERFACE TIMING SPECIFICATIONS        |                                |                           |     |     |      |  |

| T <sub>I2C-Start</sub> | I <sup>2</sup> C-Compatible Logic startup time | I <sup>2</sup> C/EN going high |                           | 250 | 500 | µsec |  |

| f <sub>SCL</sub>       | SCL clock frequency                            |                                |                           |     | 400 | kHz  |  |

| t <sub>LOW</sub>       | Low period of SCL clock                        |                                | 1.3                       |     |     | µsec |  |

| t <sub>HIGH</sub>      | High period of SCL clock                       |                                | 0.6                       |     |     | µsec |  |

| t <sub>HD-STA</sub>    | Hold time (repeated) START condition           |                                | 0.6                       |     |     | µsec |  |

| t <sub>SU-STA</sub>    | Setup time for a repeated START condition      |                                | 0.6                       |     |     | µsec |  |

| t <sub>HD-DAT</sub>    | Data hold time                                 |                                | 0                         |     |     | µsec |  |

| t <sub>SU-DAT</sub>    | Data setup time                                |                                | 100                       |     |     | nsec |  |

| t <sub>R</sub>         | Rise time for SCL and SDA                      |                                |                           |     | 300 | nsec |  |

| t <sub>F</sub>         | Fall time for SCL and SDA                      |                                |                           |     | 300 | nsec |  |

| t <sub>su-sто</sub>    | Setup time for stop condition                  |                                | 0.6                       |     |     | µsec |  |

| t <sub>BUF</sub>       | Bus free time between stop and start condition |                                | 1.3                       |     |     | µsec |  |

| t <sub>VD-DAT</sub>    | Data valid time                                |                                |                           |     | 0.9 | µsec |  |

| t <sub>VD-ACK</sub>    | Data valid acknowledge time                    |                                |                           |     | 0.9 | µsec |  |

| C <sub>B</sub>         | Capacitive load for each bus line              |                                | 20+0.1х<br>С <sub>В</sub> |     | 400 | pF   |  |

www.ti.com.cn

STRUMENTS

EXAS

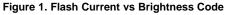

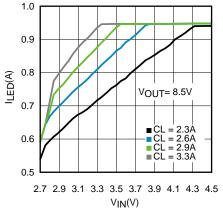

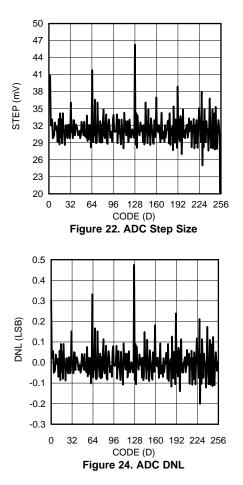

## **TYPICAL CHARACTERISTICS**

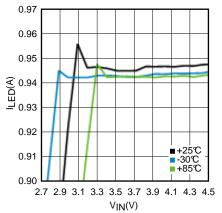

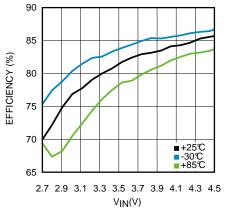

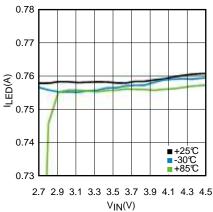

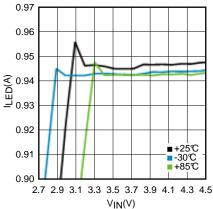

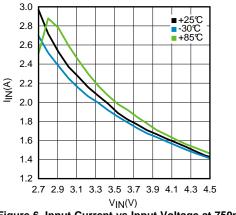

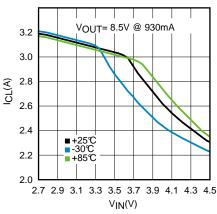

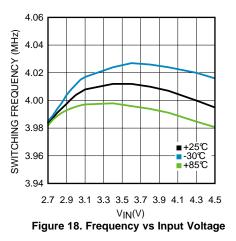

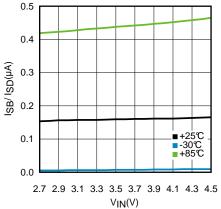

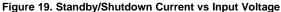

Unless otherwise specified:  $T_A = 25^{\circ}C$ ;  $V_{IN} = 3.6V$ ;  $C_{IN1} = 10 \ \mu$ F,  $C_{IN2} = 0.1 \ \mu$ F,  $C_{OUT1} = 10 \ \mu$ F,  $C_{OUT2} = 10 \ \mu$ F,  $L = 1 \ \mu$ H.

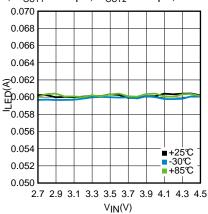

Figure 3. 930mA Flash LED Current vs Input Voltage

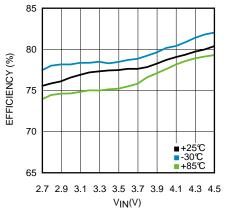

Figure 5. LED Efficiency vs Input Voltage at 930mA

Figure 2. 750mA Flash LED Current vs Input Voltage

Figure 4. LED Efficiency vs Input Voltage at 750mA

## LM3565

ZHCSBI2-JANUARY 2013

#### www.ti.com.cn

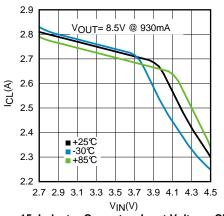

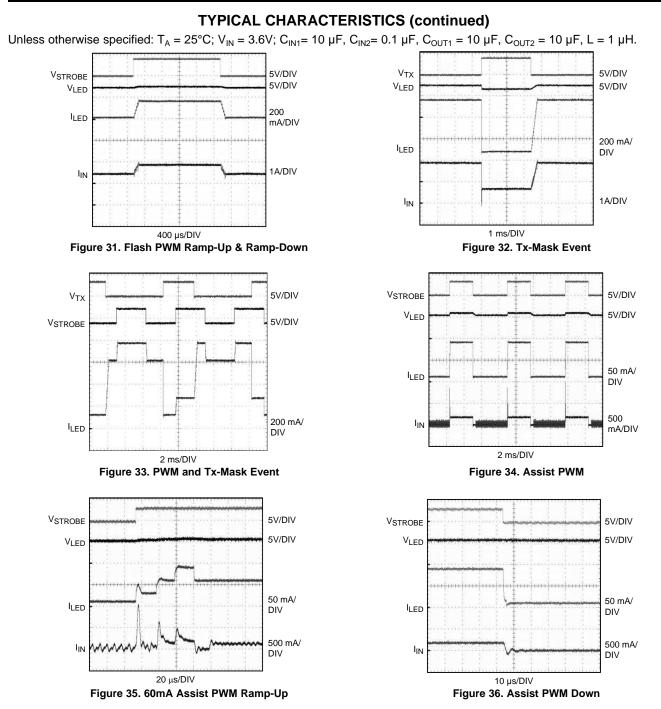

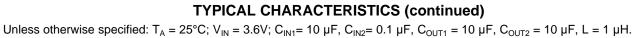

#### **TYPICAL CHARACTERISTICS (continued)**

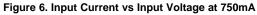

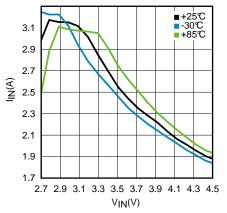

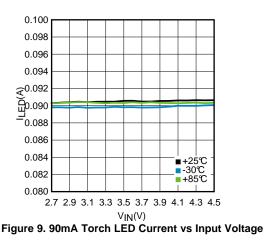

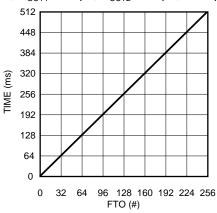

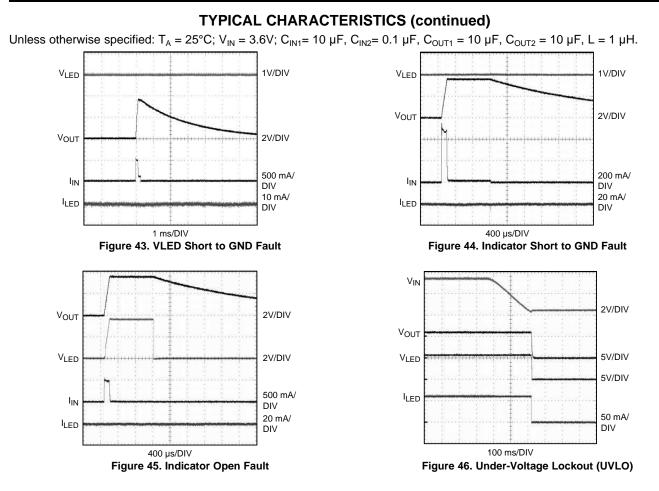

Unless otherwise specified:  $T_A = 25^{\circ}C$ ;  $V_{IN} = 3.6V$ ;  $C_{IN1} = 10 \ \mu\text{F}$ ,  $C_{IN2} = 0.1 \ \mu\text{F}$ ,  $C_{OUT1} = 10 \ \mu\text{F}$ ,  $C_{OUT2} = 10 \ \mu\text{F}$ ,  $L = 1 \ \mu\text{H}$ .

Figure 7. Input Current vs Input Voltage at 930mA

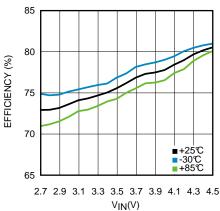

Figure 11. LED Efficiency vs Input Voltage at 90mA

Figure 8. 60mA Torch LED Current vs Input Voltage

Figure 10. LED Efficiency vs Input Voltage at 60mA

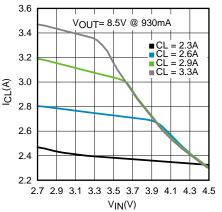

Figure 12. Inductor Current Limit vs Input Voltage

www.ti.com.cn

**STRUMENTS**

EXAS

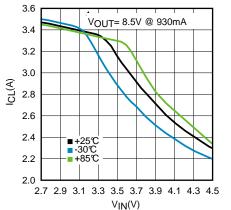

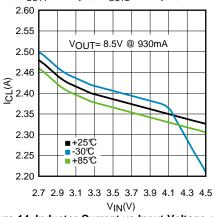

#### **TYPICAL CHARACTERISTICS (continued)**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ;  $V_{IN} = 3.6V$ ;  $C_{IN1} = 10 \ \mu$ F,  $C_{IN2} = 0.1 \ \mu$ F,  $C_{OUT1} = 10 \ \mu$ F,  $C_{OUT2} = 10 \ \mu$ F,  $L = 1 \ \mu$ H.

Figure 13. LED Current vs Input Voltage in Current Limit

Figure 15. Inductor Current vs Input Voltage, CL = 2.6A

Figure 17. Inductor Current vs Input Voltage, CL = 3.3A

Figure 14. Inductor Current vs Input Voltage, CL = 2.3A

Figure 16. Inductor Current vs Input Voltage, CL = 2.9A

## **TYPICAL CHARACTERISTICS (continued)**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ;  $V_{IN} = 3.6V$ ;  $C_{IN1} = 10 \ \mu$ F,  $C_{IN2} = 0.1 \ \mu$ F,  $C_{OUT1} = 10 \ \mu$ F,  $C_{OUT2} = 10 \ \mu$ F,  $L = 1 \ \mu$ H.

Figure 20. Flash Timeout vs Flash Timeout Code

www.ti.com.cn

STRUMENTS

EXAS

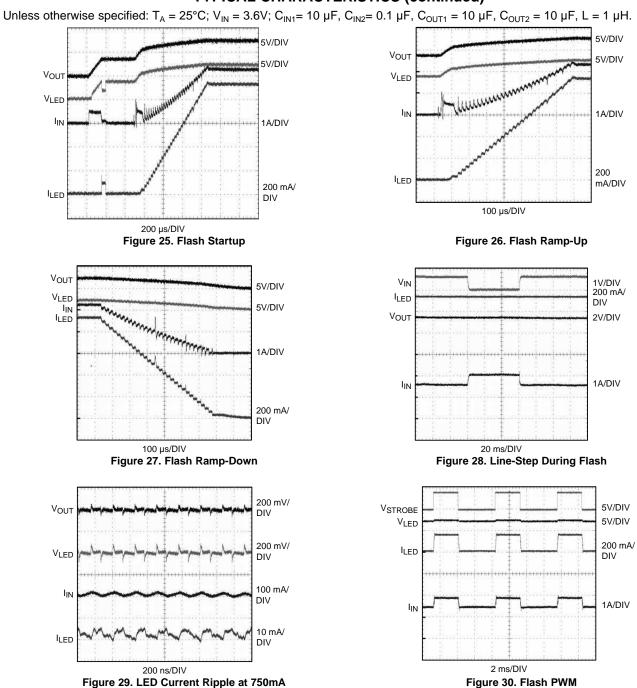

## **TYPICAL CHARACTERISTICS (continued)**

## LM3565

ZHCSBI2-JANUARY 2013

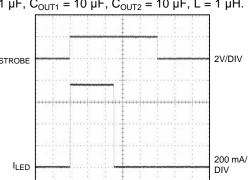

Figure 38. Level-Sensitive Strobe with Timeout

40 ms/DIV

Figure 42. VOUT Short to GND Fault

1 ms/DIV

ZHCSBI2-JANUARY 2013

VSTROBE

ILED

VSTROBE

ILED

# LM3565

ZHCSBI2-JANUARY 2013

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCSBI2-JANUARY 2013

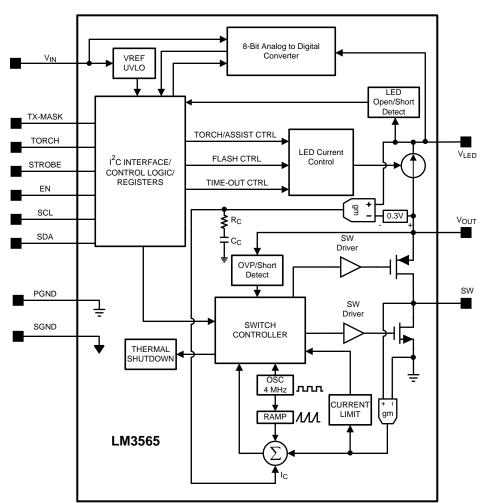

**BLOCK DIAGRAM**

## FUNCTIONAL DESCRIPTION

### **Circuit Description**

#### Overview

The LM3565 is a high-power white LED flash driver capable of delivering up to 930 mA of LED current into two series LEDs. The device incorporates a 4 MHz constant frequency, synchronous, current mode PWM boost converter, and a single high-side current source to regulate the LED current over the 2.5V to 5.5V input voltage range.

#### **Circuit Components**

#### Synchronous Boost Converter

The LM3565 operates in boost mode in LED Flash or Assist operation. In LED boost mode, the PWM converter switches and maintains at least 300 mV across the current source. This minimum headroom voltage ensures that the current sink remains in regulation.

#### **High-Side Current Source**

The High-Side current source of the LM3565 is capable of driving two LEDs in series. The flash current range is 480 mA to 930 mA in 30 mA steps with a default current equal to 750 mA.

Additionally, the high-side current source is capable of supporting two Assist/Torch current levels (continuous current) equal to 60 mA (default) or 90 mA.

#### A/D Converter

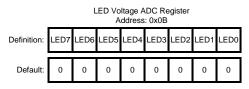

An internal 8-bit ADC can be utilized to measure the input voltage and the LED voltage during a flash or assist event. If the ADC input voltage measurement bit is set to a '1' (IV bit in register 0x09), the digitized value of the LM3565's input voltage can be read back from the Input Voltage ADC Register (0x0A). The input voltage is sampled before the start of the flash or assist event if the FON bit in register 0x09 is set to a '0' and 2ms after the LED current ramp up is completed if it is set to a '1'. The LED voltage can be read back from the LED Voltage ADC Register (0x0B) if the ADC LED voltage measurement bit is set to a '1' (LV bit in register 0x09). The LED voltage is sampled 2ms after the LED current is ramped up.

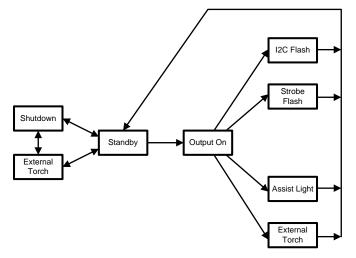

#### ENABLE Pin

The ENABLE pin on the LM3565 places the part into Shutdown Mode (low) or Standby Mode (high). In Shutdown Mode, most of the control functionality is disabled. In shutdown, it is possible to enable the part through the use of the Torch pin. In standby, the LM3565 can be controlled via the I<sup>2</sup>C-compatible interface or the Torch and Strobe pins if the part has been configured to do so. The ENABLE pin must be held low before power is applied to the LM3565.

#### SDA and SCL Pins

The SDA and SCL pins are the  $I^2$ C-compatible control interface inputs for the LM3565. SDA is the interface data input and SCL is the interface clock input.

#### STROBE Pin

The Strobe pin of the LM3565 provides an external method for initiating a flash or assist event. In most cases, the Strobe pin is connected to an imaging module so that the image capture and flash event are synchronized. The Strobe pin is only functional when the LM3565's Output Enable (OEN in 0x07) and Strobe Signal Mode (SEN in 0x06) bits are set ('1'). The Strobe pin can be configured to be an edge-sensitive or level-sensitive input by setting the Strobe Signal Usage bit (SSU in 0x06. '1' = Level, '0' = Edge). In edge-sensitive mode, a rising edge transition ('0' to '1') will start the flash event and the internal flash timer will terminate the event. In level-sensitive mode, a rising edge transition ('0' to '1') will start the flash event and a falling edge transition ('1' to '0') or the internal flash timer, which ever occurs first, will terminate the event.

Additionally, the Strobe pin can be used to pulse-width modulate (PWM) the diode current during a flash or assist event. In flash mode, by setting the PWM bit in the Strobe signaling register (PWM in register 0x06) to a '1', and toggling the Strobe pin high and low, the diode current will transition between the target flash current and a reduced current value selected in register 0x06 (SPL3-SPL0). When the Strobe pin is high ('1'), the flash current is equal to the target LED current. When the Strobe pin is low ('0'), the flash current is equal to the target LED current value, or 60 mA, whichever is higher. The diode current is ramped up and down during the transitions between the full current state and the reduced current state.

www.ti.com.cn

In assist mode, by setting the PWM bit in the Strobe signaling register (PWM in register 0x06) to a '1', and toggling the Strobe pin high and low, the diode current will transition between the target assist current and 10 mA. When the Strobe pin is high ('1'), the assist current is equal to the target LED current. When the Strobe pin is low ('0'), the assist current is equal to 10 mA. The diode current is always ramped up to 90 mA, then reduced to 60 mA if the assist target current is set to 60 mA. The transition between the full-assist current and the 10 mA current level is done in one step.

#### **TORCH Pin**

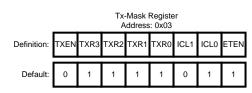

The Torch pin of the LM3565, depending on the state and configuration, allows the user to enable Torch/Assist Mode without having to write the command through the  $I^2C$  bus. In standby mode, the external torch mode bit (ETEN bit in register 0x03) must be set to a '1' to allow an external torch (default value = '1'). The torch mode current is equal to the Assist mode current level stored in register 0x02 (AS0 bit, default value = '0' or 60 mA). In shutdown mode, driving the Torch pin high will enable the LM3565 and drive the flash LEDs at 60 mA.

#### **TX-MASK** Pin

The TX-Mask pin provides the RF PA a direct method to reduce the flash current by a predetermined value stored in the TX-Mask register (0x03), to prevent a battery over-current fault. When the TX-Mask pin is set low, the normal target current is realized. When the TX-Mask pin is set high, the flash current is reduced. The flash current is not ramped during the transition from full-scale to the reduced level; the flash current is ramped when transitioning back to the full-scale value from the reduced value. As in the Fflash PWM Mode, the lowest flash current is set to 60 mA.

#### **Fault Protections**

The LM3565 has numerous internal fault protection mechanisms to help prevent damage to the LM3565 as well as the system in the event of a fault. Most fault conditions will cause the LM3565 to enter Shutdown Mode and will report a fault to the fault register (0x08) or (0x09). The faults that can be detected are as follows:

- Over-Voltage Protection (VOUT)

- Short-Circuit Protection (VOUT and VLED)

- Over-Temperature Protection

- Flash Time-Out

- TX-Mask Event

- Under-Voltage Lock-Out

- Input Low Voltage Detect

- Inductor Current Limit (not reported)

- Output Capacitor Open Protection

Figure 47. Mode Diagram

#### I<sup>2</sup>C-Compatible Interface

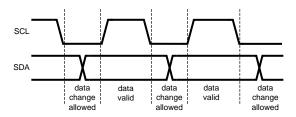

#### **Data Validity**

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when CLK is LOW.

Figure 48. Data Validity Diagram

A pull-up resistor between VIO and SDA must be greater than [ (VIO- $V_{OL}$ ) / 3mA] to meet the  $V_{OL}$  requirement on SDA. Using a larger pullup resistor results in lower switching current with slower edges, while using a smaller pull-up results in higher switching currents with faster edges.

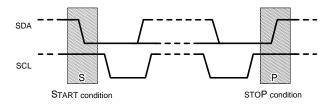

#### **Start and Stop Conditions**

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C-compatible session. A START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C-compatible master always generates START and STOP conditions. The I<sup>2</sup>C-compatible bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C-compatible master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise. The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when CLK is LOW.

Figure 49. Start and Stop Conditions

#### **Transferring Data**

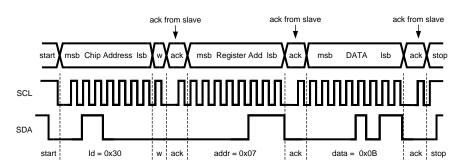

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LM3565 pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The LM3565 generates an acknowledge after each byte has been received.

After the START condition, the I<sup>2</sup>C-compatible master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3565 address is 30h. For the eighth bit, a '0' indicates a WRITE and a '1' indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

TEXAS INSTRUMENTS

www.ti.com.cn

#### ZHCSBI2-JANUARY 2013

NOTE: w = write (SDA = "0"), ack = acknowledge (SDA pulled down by the slave), id = chip address, 30h for LM3565

#### Figure 50. Write Cycle

## I<sup>2</sup>C-Compatible Chip Address

The chip address for LM3565 is 0110000, or 30hex.

| _ | MSB          |              |                        |              |              |              |              | LSB         |

|---|--------------|--------------|------------------------|--------------|--------------|--------------|--------------|-------------|

|   | ADR6<br>bit7 | ADR5<br>bit6 | ADR4<br>bit5           | ADR3<br>bit4 | ADR2<br>bit3 | ADR1<br>bit2 | ADR0<br>bit1 | R/W<br>bit0 |

| Ì | 0            | 1            | 1                      | 0            | 0            | 0            | 0            |             |

|   | •            |              | I <sup>2</sup> C Slave | Address (cł  | nip address  | s) ———       |              |             |

## Internal Registers of LM3565

#### Table 1. Summary of LM3565 Registers

| REGISTER                     | INTERNAL HEX ADDRESS | POWER ON VALUE |

|------------------------------|----------------------|----------------|

| Design Information Register  | 0x00                 | 0011 0100      |

| Version Control Register     | 0x01                 | 0000 0110      |

| Current Set Register         | 0x02                 | 0000 1001      |

| TX-Mask Register             | 0x03                 | 0111 1011      |

| Low Voltage Control Register | 0x04                 | 0100 0100      |

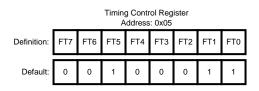

| Timing Control Register      | 0x05                 | 0010 0011      |

| Strobe Signaling Register    | 0x06                 | 1100 1000      |

| Output Mode Register         | 0x07                 | 0000 0000      |

| Fault and Info Register      | 0x08                 | 0000 0000      |

| ADC Control Register         | 0x09                 | 0000 0000      |

| Input Voltage ADC Register   | 0x0A                 | 0000 0000      |

| LED Voltage ADC Register     | 0x0B                 | 0000 0000      |

## Register Definitions (bold table values = default register settings)

|             | Design Information Register<br>Address: 0x00 |     |     |     |     |     |     |     |  |

|-------------|----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Definition: | MN3                                          | MN2 | MN1 | MN0 | MO3 | MO2 | MO1 | MO0 |  |

| Default:    | 0                                            | 0   | 1   | 1   | 0   | 1   | 0   | 0   |  |

MN3–MN0: Manufacturer ID = 0011 MO3–MO0: Model ID = 0100

|             | Version Control Register<br>Address: 0x01 |     |     |     |     |     |     |     |

|-------------|-------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Definition: | RF3                                       | RF2 | RF1 | RF0 | DR3 | DR2 | DR1 | DR0 |

| Default:    | 0                                         | 0   | 0   | 0   | 0   | 1   | 1   | 0   |

RF3–RF0: Unused DR3–DR0: Design Revision = 0110

|             |    | Current Set Register<br>Address: 0x02 |    |     |     |     |     |     |  |  |

|-------------|----|---------------------------------------|----|-----|-----|-----|-----|-----|--|--|

| Definition: | NA | NA                                    | NA | AS0 | FS3 | FS2 | FS1 | FS0 |  |  |

| Default:    | 0  | 0                                     | 0  | 0   | 1   | 0   | 0   | 1   |  |  |

AS0: Assist Current Level Bit. '0' = 60 mA, '1' = 90 mAFS3-FS0: Flash Set Current bits. Refer to Table 2 for details.

| FS3 | FS2 | FS1 | FS0 | Flash<br>Current<br>Level |  |  |  |  |

|-----|-----|-----|-----|---------------------------|--|--|--|--|

| 0   | 0   | 0   | 0   | 480 mA                    |  |  |  |  |

| 0   | 0   | 0   |     | 510 mA                    |  |  |  |  |

| 0   | 0   | 1   | 0   | 540 mA                    |  |  |  |  |

| 0   | 0   | 1   | 1   | 570 mA                    |  |  |  |  |

| 0   | 1   | 0   | 0   | 600 mA                    |  |  |  |  |

| 0   | 1   | 0   | 1   | 630 mA                    |  |  |  |  |

| 0   | 1   | 1   | 0   | 660 mA                    |  |  |  |  |

| 0   | 1   | 1   | 1   | 690 mA                    |  |  |  |  |

| 1   | 0   | 0   | 0   | 720 mA                    |  |  |  |  |

| 1   | 0   | 0   | 1   | 750 mA                    |  |  |  |  |

| 1   | 0   | 1   | 0   | 780 mA                    |  |  |  |  |

| 1   | 0   | 1   | 1   | 810 mA                    |  |  |  |  |

| 1   | 1   | 0   | 0   | 840 mA                    |  |  |  |  |

| 1   | 1   | 0   | 1   | 870 mA                    |  |  |  |  |

| 1   | 1   | 1   | 0   | 900 mA                    |  |  |  |  |

| 1   | 1   | 1   | 1   | 930 mA                    |  |  |  |  |

#### **Table 2. Flash Currents**

www.ti.com.cn

TXEN: TX-Mask Enable Bit. '0' = TX-Mask Disabled. '1' = TX-Mask Enabled. TXR3-TXR0: TX-Mask Current Reduction Bits. See TX-Mask Flash Current Reduction Levels table. ICL1-ICL0: Inductor Peak Current Limit Bits. See Peak Inductor Current Limit Levels table. ETEN: External Torch Enable Bit. '0' = External Torch Mode disabled in standby. '1' = External Torch Mode allowed/enabled in standby.

| TXR3 | TXR2 | TXR1 | TXR0 | Flash Reduction<br>Level |

|------|------|------|------|--------------------------|

| 0    | 0    | 0    | 0    | 30 mA                    |

| 0    | 0    | 0    | 1    | 60 mA                    |

| 0    | 0    | 1    | 0    | 90 mA                    |

| 0    | 0    | 1    | 1    | 120 mA                   |

| 0    | 1    | 0    | 0    | 150 mA                   |

| 0    | 1    | 0    | 1    | 180 mA                   |

| 0    | 1    | 1    | 0    | 210 mA                   |

| 0    | 1    | 1    | 1    | 240 mA                   |

| 1    | 0    | 0    | 0    | 270 mA                   |

| 1    | 0    | 0    | 1    | 300 mA                   |

| 1    | 0    | 1    | 0    | 330 mA                   |

| 1    | 0    | 1    | 1    | 360 mA                   |

| 1    | 1    | 0    | 0    | 390 mA                   |

| 1    | 1    | 0    | 1    | 420 mA                   |

| 1    | 1    | 1    | 0    | 450 mA                   |

| 1    | 1    | 1    | 1    | 480 mA                   |

#### Table 3. TX-Mask Flash Current Reduction Levels

| ICL1 | ICL0 | Peak Inductor Current Limit |

|------|------|-----------------------------|

| 0    | 0    | 2.3A                        |

| 0    | 1    | 2.6A                        |

| 1    | 0    | 2.9A                        |

| 1    | 1    | 3.3A                        |

| Low Voltage Control Register<br>Address: 0x04 |                                    |   |   |   |   |   |      |   |  |

|-----------------------------------------------|------------------------------------|---|---|---|---|---|------|---|--|

| Definition:                                   | NA LVEN LVL2 LVL1 LVL0 LVR1 LVR0 L |   |   |   |   |   | LVRS |   |  |

| Default:                                      | 0                                  | 1 | 0 | 0 | 0 | 1 | 0    | 0 |  |

LVEN: Flash Low Voltage Checking Enable Bit. '0' = Disabled, '1' = Enabled LVL2-LVL0: Flash Low Voltage Detection Level. See Table 5. LVR1-LVR0: Flash Low Voltage Current Reduction Level. See Table 5.

| LVRS: State Machine Reset Bit. | '0' = Normal operation, '1' = RESET |

|--------------------------------|-------------------------------------|

|--------------------------------|-------------------------------------|

#### Input Voltage LVL2 LVL1 LVL0 Level 3.0V 0 0 0 0 0 1 3.1V 0 1 0 3.2V 1 1 0 3.3V 1 0 0 3.4V 1 1 0 3.5V 1 1 0 3.6V 1 1 1 3.7V

## **Table 5. Flash Low Voltage Detection Levels**

#### **Table 6. Flash Low Voltage Current Reduction Values**

| ICL1 | ICL0 | Peak Inductor Current Limit |

|------|------|-----------------------------|

| 0    | 0    | 150 mA                      |

| 0    | 1    | 180 mA                      |

| 1    | 0    | 210 mA                      |

| 1    | 1    | 240 mA                      |

FT7-FT0: Flash Timeout Duration Bits.

Flash Time =  $(2 + N \times 2)$ ms, where  $0 \le N \le 255$

'0x00' = 2ms, '0x01' = 4ms, '0x02' = 6ms, . . ., '0x22' = 126ms, . . ., '0xFF' = 512 ms.

www.ti.com.cn

| Strobe Signaling Register<br>Address: 0x06 |                               |   |   |   |   |   |      |     |  |

|--------------------------------------------|-------------------------------|---|---|---|---|---|------|-----|--|

| Definition:                                | SEN SSU PWM SPL3 SPL2 SPL1 SF |   |   |   |   |   | SPL0 | SLL |  |

| Default:                                   | 1                             | 1 | 0 | 0 | 1 | 0 | 0    | 0   |  |

SEN: = Strobe Enable Bit. '0' = Disabled, '1' = Enabled SSU: Strobe Signal Usage Bit. '0' = edge-sensitive, '1' = Level Sensitive PWM: Flash PWM w/ Strobe Signal Enable bit. '0' =Disabled, '1' = Enabled SPL3-SPL0: Stobe PWM Flash Current Reduction Level. See Strobe PWM Flash Current Reduction Levels table. SLL: Strobe Logic Level Bit. '0' = 1.2V Logic, '1' = 1.8V Logic

#### Table 7. Strobe PWM Flash Current Reduction Levels

| SPL3 | SPL2 | SPL1 | SPL0 | Flash Current Level |

|------|------|------|------|---------------------|

| 0    | 0    | 0    | 0    | 30 mA               |

| 0    | 0    | 0    | 1    | 60 mA               |

| 0    | 0    | 1    | 0    | 90 mA               |

| 0    | 0    | 1    | 1    | 120 mA              |

| 0    | 1    | 0    | 0    | 150 mA              |

| 0    | 1    | 0    | 1    | 180 mA              |

| 0    | 1    | 1    | 0    | 210 mA              |

| 0    | 1    | 1    | 1    | 240 mA              |

| 1    | 0    | 0    | 0    | 270 mA              |

| 1    | 0    | 0    | 1    | 300 mA              |

| 1    | 0    | 1    | 0    | 330 mA              |

| 1    | 0    | 1    | 1    | 360 mA              |

| 1    | 1    | 0    | 0    | 390 mA              |

| 1    | 1    | 0    | 1    | 420 mA              |

| 1    | 1    | 1    | 0    | 450 mA              |

| 1    | 1    | 1    | 1    | 480 mA              |

| Output Mode Register<br>Address: 0x07 |   |   |   |   |     |   |     |     |

|---------------------------------------|---|---|---|---|-----|---|-----|-----|

| Definition:                           | x | x | x | x | OEN | x | OM1 | OM0 |

| Default:                              | 0 | 0 | 0 | 0 | 0   | 0 | 0   | 0   |

OEN: Output Enable Bit. '0' = Disabled, '1' = Enabled OM1-OM0: Output Mode Bits. See Output Modes table.

| Table 8. Output Modes |   |                |  |  |  |  |  |

|-----------------------|---|----------------|--|--|--|--|--|

| OM1 OM0 Output Mode   |   |                |  |  |  |  |  |

| 0                     | 0 | External Torch |  |  |  |  |  |

| 0                     | 1 | Do Not Use     |  |  |  |  |  |

| 1                     | 0 | Assist Light   |  |  |  |  |  |

| 1                     | 1 | Flash          |  |  |  |  |  |

#### Fault and Info Register Address: 0x08 OVP SC то тхм RFU ILV Definition: OTP UVLO 0 0 0 0 0 0 Default: 0 0

OVP: Over-Voltage Protection Fault Flag

SC: Short Circuit Fault Flag

OTP: Over Temperature Protection Flag

TO: Flash Timeout Flag TXM: TX-Mask Event Flag

ILV: Input Low Voltage Fault Flag

UVLO: Under Voltage Lock Out Fault Flag

| ADC Control<br>Address: 0x09 |    |    |     |    |     |     |     |     |  |

|------------------------------|----|----|-----|----|-----|-----|-----|-----|--|

| Definition:                  | IV | LV | FON | СО | RFU | RFU | RFU | RFU |  |

| Default:                     | 0  | 0  | 0   | 0  | 0   | 0   | 0   | 0   |  |

IV: ADC Input Voltage Measurement Enable Bit. '0' = Disabled, '1' = Enabled

LV: ADC LED Voltage Measurement Enable Bit. '0' = Disabled, '1' = Enabled

FON: Input Voltage Measurement during Flash Bit. '0' = Without Flash Current, '1' = With Flash Current CO: Open Output Capacitor Fault Bit. '0' = Normal Operation, '1' = Missing Output Capacitor

TEXAS INSTRUMENTS

ZHCSBI2-JANUARY 2013

Input Voltage ADC Register Address: 0x0A Definition: IVD7 IVD6 IVD4 IVD3 IVD2 IVD1 IVD0 IVD5 Default: 0 0 0 0 0 0 0 0

IVD7-IVD0: ADC Input Voltage Measurement Data

LED7-LED0: ADC LED Voltage Measurement Data

www.ti.com.cn

LM3565

ZHCSBI2-JANUARY 2013

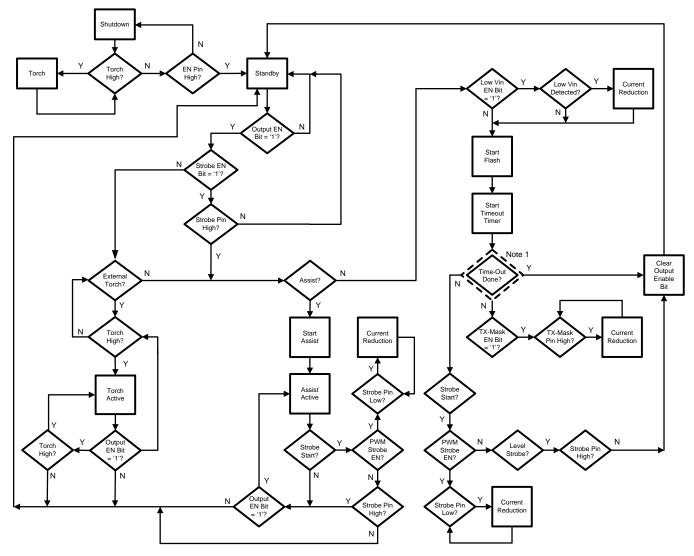

## **Control State Diagram**

Note 1: Flash time-out is always checked during flash. Flash is terminated when time-out is done.

## I<sup>2</sup>C Mode Truth Table

| OEN | OM1 | OM0 | ETEN | SEN | TORCH | STROBE | Mode           |

|-----|-----|-----|------|-----|-------|--------|----------------|

| 0   | 0   | 0   | 0    | Х   | Х     | Х      | Standby        |

| 0   | 0   | 0   | 1    | Х   | 0     | Х      | Standby        |

| 0   | 0   | 0   | 1    | Х   | 1     | Х      | Ext Torch      |

| 0   | 0   | 1   | Х    | Х   | Х     | Х      | Standby        |

| 0   | 1   | 0   | Х    | Х   | Х     | Х      | Standby        |

| 0   | 1   | 1   | Х    | Х   | Х     | Х      | Standby        |

| 1   | 0   | 0   | Х    | Х   | 0     | Х      | Standby        |

| 1   | 0   | 0   | 1    | Х   | 1     | Х      | Ext Torch      |

| 1   | 0   | 1   | Х    | 0   | Х     | Х      | RFU            |

| 1   | 1   | 0   | Х    | 0   | Х     | Х      | Assist         |

| 1   | 1   | 1   | Х    | 0   | Х     | Х      | Internal Flash |

| 1   | 0   | 0   | Х    | 1   | Х     | 0      | Standby        |

| 1   | 0   | 1   | Х    | 1   | Х     | 1      | RFU            |

| 1   | 1   | 0   | Х    | 1   | Х     | 1      | Strobe Assist  |

| 1   | 1   | 1   | Х    | 1   | Х     | 1      | Strobe Flash   |

### **APPLICATION INFORMATION**

#### **Torch or Assist (Continuous Current) Operation**

There are two different continuous current modes on the LM3565: Torch and Assist.

Torch Mode is enabled through the use of the dedicated Torch pin. The Torch pin functionality can be enabled and disabled by setting the value of the ETEN bit in the TX-Control Register (Address 0x03). ETEN = '1' allows an external Torch while ETEN = '0' does not.

The primary method to enable Assist Mode is by setting the Output Mode bits (OM1 and OM0) to '10' and setting the Output Enable bit (OEN) to a '1' in the Control Register (0x07). Assist Mode will remain active in  $I^2C$ -compatible Mode until the OEM bit is set to '0'.

The secondary Assist Mode enabling method involves using the Strobe pin. By setting the SEN bit in the Stobe Signaling Register (Address 0x06) to a '1', then setting the Output Mode bits (OM1 and OM0) to '10' and setting the Output Enable bit (OEN) to a '1' in the Control Register (0x07), the LM3565 will be configured to enable Assist Mode upon the Strobe pin transitioning state from low to high. In this configuration, Assist Mode will remain active until the OEN bit is set to '0'. Transitioning the Strobe pin from high to low does not automatically clear the OEN. In Assist Mode, the Strobe Signal Usage bit (SSU in Strobe Signaling Register 0x06) is ignored, and the Strobe pin is always set to be edge sensitive.

The LM3565 can drive two LEDs at continuous current levels of 60 mA or 90 mA. The current is set in the Current Set Register utilizing the AS0 bit (Address 0x02, AS0). Writing a '0' (default) sets the assist current to 60 mA while writing a '1' sets the assist current to 90 mA.

In Torch or Assist Mode, the LED current is ramped up to 90 mA in 30 mA steps at 20 µs intervals, then reduced to 60 mA if the assist target current is set to 60 mA. The assist current is terminated in one step.

#### Flash (Pulsed Current) Operation

A flash event using the LM3565 can be initiated though the I<sup>2</sup>C-compatible control interface, and through the use of the Strobe pin.

When using the I<sup>2</sup>C-compatible Control Mode, a flash event is initiated when the Output Mode bits (OM1 and OM0) are set to '11' and the Output Enable bit (OEN) is set to a '1' in the Control Register (0x07). In I<sup>2</sup>C-compatible Mode, the flash event will remain active as long as the OEN bit is set to a '1' and will terminate upon a time-out event. The safety timer duration can be set in 2 ms intervals ranging from 2 ms to 512 ms by writing the desired value to the FT7-FT0 bits in the Timer Register (Address 0x05, with the default timer set to 72 msec.).

The Strobe pin provides added system flexibility in that it allows an additional external device (Camera Module, GPU etc.) to trigger a flash event. To initiate a Strobe event in I<sup>2</sup>C-compatible Control Mode, the Strobe Enable (SEN) bit in the Strobe Signaling Register (0x06) must first be set to a '1', and the Output Enable (OEN) bits and Output Mode bits (OM1 and OM0) in the Control Register (Address 0x07) must be set to '1's.

Following the setting of the SEN and OEN bits, the user must choose to have an edge-sensitive or level-sensitive strobe event. Writing a '1' to the Strobe Signal Usage (SSU) bit in the Control Register (Address 0x06), the LM3565 will be configured to be level sensitive, while writing a '0' configures the part to be edge-sensitive. In both cases, the strobe flash event is started upon the Strobe pin being driven high.

In an edge-sensitive event, the flash duration will stay active until the flash duration timer lapses regardless of the state of the Strobe pin. If a level-sensitive strobe is used, the flash event will remain active as long as the Strobe pin is held high and as long as the flash duration time has not lapsed.

In Flash Mode, the LED current is ramped up and down in 30 mA steps at 20 µs intervals.

At the end of a flash event, whether initiated through the Control Register or Strobe pin, the LM3565 will force the OEN bit to a '0' and will place the LM3565 back into the Standby state.

## Fault Protections

The LM3565 has a number of fault protection mechanisms designed to not only protect the LM3565 itself, but also to reset the system. Active fault protections include:

- Over-Voltage Protection (VOUT)

- Short-Circuit Protection (VOUT and VLED)

- Over-Temperature Protection

- Flash Time-Out

- Under-Voltage Lock-Out (UVLO)

- Output Capacitor Open Protection

In the event that any of these faults occur, the LM3565 will set a flag in the appropriate Fault Register (Address 0x08 or 0x09) and place the part into standby. Normal operation cannot resume until the fault has been fixed and an I<sup>2</sup>C read of the fault register (0x08 and/or 0x09) has been completed. All faults are cleared upon reading the Fault Registers (0x08 and 0x09).

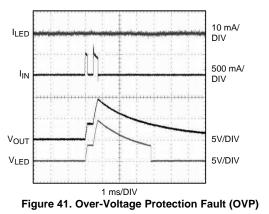

#### **Output Over-Voltage Protection (OVP)**

An OVP fault is triggered when the output voltage of the LM3565 reaches a value greater than 9.5V (typ). The OVP condition is cleared when the output voltage ( $V_{OUT}$ ) is able to operate below 9.5V. An output capacitor or an LED that have become an open circuit can cause an OVP event to occur. This fault is reported to the OVP fault bit in the Fault Register (bit7 in address 0x05).

#### **Output and LED Short Circuit Protection (SC)**

An SC fault is triggered when the output voltage (VOUT) and/or the LED voltage (VLED) does not reach 0.8V in 0.5 ms. The short circuit condition is cleared when the output (VOUT) is allowed to reach its steady state target and when the LED voltage rises above 0.8V. A shorted output capacitor or a shorted LED could cause this fault to occur. This fault is reported to the SC fault bit in the Fault Register (bit6 in address 0x08).

#### **Over-Temperature Protection (OTP)**

An OTP fault is triggered when the diode junction temperature of the LM3565 reaches an internal temperature of around 150°C. The OTP condition is cleared when the junction temperature falls below 115°C and the fault register is read. A printed circuit board (PCB) with poor thermal dissipation properties and very high ambient temperatures (greater that 85°C) could cause this fault to occur. Refer to Texas Instruments Application Note: AN-1112: DSBGA Wafer Level Chip Scale Package for more information regarding proper PCB layout. This fault is reported to the OTP fault bit in the Fault Register (bit5 in address 0x08).

#### Flash Time-Out (TO)

The TO fault will be triggered whenever a flash is initiated with a level-sensitive Strobe event controlled by a camera module and the Strobe pulse duration exceeds the selected Flash Time-out duration. This fault is reported to the TO fault bit in the Fault Register (bit4 in address 0x08). This bit only gets set when PWM Mode is disabled.

#### Under-Voltage Lock-Out (UVLO)

An Under-Voltage Lock-Out (UVLO) fault occurs when the input voltage at the LM3565 drops below 2.4V (typ). When this fault occurs, the LM3565 will be forced into Standby Mode and the UVLO bit will be set to a '1'. To exit a UVLO state, the input voltage to the LM3565 must increase by 100 mV (typ.) and the UVLO Fault bit must be cleared. This fault is reported to the UVLO fault bit in the Fault Register (bit0 in address 0x08).

#### **Output Capacitor Open Protection (CO)**

An Output Capacitor Open fault is triggered when the LM3565 detects that the capacitance at the VOUT pin has dropped below the acceptable value (typically 0.1  $\mu$ F). This fault indicates that the output capacitors are either disconnected or damaged and is reported to the Output Capacitor fault bit in the ADC Control Register (bit4 in address 0x09). Once an Output Capacitor Open fault is detected, the State Machine Reset bit (LVRS) in the Low Voltage Control register (0x04) has to bo toggled between a '1' and a '0' in order for normal operation to resume.

#### Input Low Voltage Flag (ILV)

The LM3565 has an Input Low Voltage (ILV) detection mechanism that sets the ILV flag (bit1 in address 0x08) when this feature is enabled (LVEN = 1, bit6 in address 0x04) and the input voltage is below the threshold set in the Low Voltage Control Register (LVL2-LVL0 in address 0x04). The input voltage is only monitored before the start of a flash event. This is a reporting flag bit and not a fault bit. The ILV flag bit does not halt or reset the LM3565.

#### TX-Mask Flag (TXM)

The LM3565 has a Transmit Interrupt flag bit (TXM, bit 3 in address 0x08) that gets set if the TX-Mask feature is enabled (TXEN = 1, bit7 in address 0x03) and if the TX-Mask pin is high, indicating a TX-Mask event. This is a reporting flag bit and not a fault bit. The TXM flag bit does not halt or reset the LM3565.

| Component    | Manufacturer | Value  | Part Number       | Current/Voltage Rating (Resistance) |

|--------------|--------------|--------|-------------------|-------------------------------------|

| L            | Toko         | 1µH    | 1239AS-H-1R0N     | I <sub>SAT</sub> = 3A (59 mΩ)       |

| COUT1, COUT2 | Murata       | 10 µF  | GRM21BR61C106KE15 | 16 V                                |

| CIN1         | Murata       | 10 µF  | GRM188R60J106ME47 | 6.3 V                               |

| CIN2         | Murata       | 0.1 µF | GRM155R71C104KA88 | 16 V                                |

Table 9. Application Circuit Components List

#### Inductor Current Limit

To prevent damage to the LM3565's inductor and to limit the power drawn by the LM3565 during a flash event, an Inductor Current Limit circuit is present. The LM3565 monitors the current through the inductor during the charge phase of the boost cycle. In the event that the inductor current reaches the current limit, the NFET of the converter will terminate the charge phase for that cycle. The process will repeat itself until the flash event has ended or until the input voltage increases to the point where the peak current is no longer reached. Hitting the peak inductor current limit will not disable the part. It will however limit the output power delivery to the LEDs.

The inductor current limit can be set to 2.3A, 2.6A (default), 2.9A or 3.3A depending on the values of the ICL1 and ICL0 bits in the TX-Masking Register (Address 0x03). The peak inductor current limit value can be used to help size the inductor to the appropriate saturation current level. For more information on inductor sizing, refer to the INDUCTOR SELECTION section of this datasheet.

#### **Inductor Selection**

The LM3565 is designed to use a 1µH inductor. When the device is boosting ( $V_{OUT} > V_{IN}$ ) the inductor is one of the biggest sources of efficiency loss in the circuit. Therefore, choosing an inductor with the lowest possible series resistance is important. Additionally, the saturation rating of the inductor should be greater than the maximum operating peak current of the LM3565. This prevents excess efficiency loss that can occur with inductors that operate in saturation and prevents over-heating of the inductor and possible damage. For proper inductor operation and circuit performance ensure that the inductor saturation and the peak current limit setting of the LM3565 (2.3A, 2.6A (default), 2.9A or 3.3A) is greater than  $I_{PEAK}$ .  $I_{PEAK}$  can be calculated by:

$$I_{\text{PEAK}} = \frac{I_{\text{LOAD}}}{\eta} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} + \Delta I_{\text{L}}$$

where

$$\Delta I_{L} = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{2 \times f_{SW} \times L \times V_{OUT}}$$

### **Capacitor Selection**

The LM3565 requires 3 external capacitors for proper operation ( $C_{IN} = 10 \ \mu\text{F}$  recommended (4.7  $\mu\text{F}$  min) and 2 x  $C_{OUT} = 10 \ \mu\text{F}$ ). An additional 0.1  $\mu\text{F}$  input capacitor placed right next to the VIN pin is recommended. Surface-mount multi-layer ceramic capacitors are recommended. These capacitors are small, inexpensive, and have very low equivalent series resistance (ESR <20 m $\Omega$  typ.). Tantalum capacitors, OS-CON capacitors, and aluminum electrolytic capacitors are not recommended for use with the LM3565 due to their high ESR, as compared to ceramic capacitors.

For most applications, ceramic capacitors with X7R or X5R temperature characteristic are preferred for use with the LM3565. These capacitors have tight capacitance tolerance (as good as  $\pm 10\%$ ) and hold their value over temperature (X7R:  $\pm 15\%$  over  $-55^{\circ}$ C to  $125^{\circ}$ C; X5R:  $\pm 15\%$  over  $-55^{\circ}$ C to  $85^{\circ}$ C).

Capacitors with Y5V or Z5U temperature characteristic are generally not recommended for use with the LM3565. Capacitors with these temperature characteristics typically have wide capacitance tolerance (+80%, -20%) and vary significantly over temperature (Y5V: +22%, -82% over -30°C to +85°C range; Z5U: +22%, -56% over +10°C to +85°C range). Under some conditions, a nominal 1 $\mu$ F Y5V or Z5U capacitor could have a capacitance of only 0.1  $\mu$ F. Such detrimental deviation is likely to cause Y5V and Z5U capacitors to fail to meet the minimum capacitance requirements of the LM3565.

The recommended voltage rating for the input capacitor is 10V (min = 6.3V). The recommended output capacitor voltage rating is 16V (min = 10V). The recommended value takes into account the DC bias capacitance losses, while the minimum rating takes into account the OVP trip levels.

#### Layout Considerations

The DSBGA is a chip-scale package with good thermal properties. For more detailed instructions on handling and mounting DSBGA packages, refer to Texas Instruments Application Note AN-1112.

The high switching frequencies and large peak currents make the PCB layout a critical part of the design. The proceeding steps must be followed to ensure stable operation and proper current source regulation.

- 1. Connect the inductor as close as possible to the SW pin. This reduces the inductance and resistance of the switching node which minimizes ringing and excess voltage drops.

- 2. Connect the return terminals of the input capacitor and the output capacitor as close as possible to the PGND pins and through low impedance traces.

- 3. Bypass V<sub>IN</sub> with a 10  $\mu$ F ceramic capacitor and an additional 0.1  $\mu$ F ceramic capacitor. Connect the positive terminal of this capacitor as close as possible to V<sub>IN</sub>.

- Connect C<sub>OUT</sub> as close as possible to the V<sub>OUT</sub> pin. This reduces the inductance and resistance of the output bypass node which minimizes ringing and voltage drops. This will improve efficiency and decrease the noise injected into the current sources.

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM3565TLE/NOPB   | ACTIVE        | DSBGA        | YZR                | 16   | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -30 to 85    | 3565                    | Samples |

| LM3565TLX/NOPB   | ACTIVE        | DSBGA        | YZR                | 16   | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -30 to 85    | 3565                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

10-Dec-2020

# YZR0016

B. This drawing is subject to change without notice.

#### 重要声明和免责声明

Ⅱ 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、 验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用 所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权 许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司