# **LP3923 Cellular Phone Power Management Unit**

Check for Samples: LP3923

### **FEATURES**

- Integrated Li-Ion Battery Charger with Power FET, Thermal Regulation and 28V OVP

- Six Low-Noise LDOs, Two LILO LDOs

- 3 x 300 mA

- 4 x 150 mA

- 1 x 80 mA

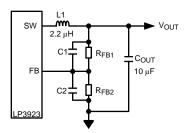

- One High Efficiency Synchronous Magnetic Buck Regulators, I<sub>OUT</sub> 700 mA

- High Efficiency PFM Mode @low lour

- Auto Mode PFM/PWM Switch

- Low Inductance 2.2 µH @ 2 MHz Clock

- I<sup>2</sup>C-compatible Interface for Controlling LDO Outputs and Charger Operation

- Thermal Shutdown with Early Warning Alarm

- Under-Voltage Lockout

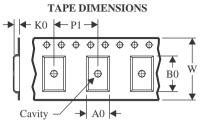

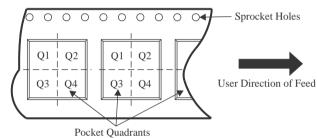

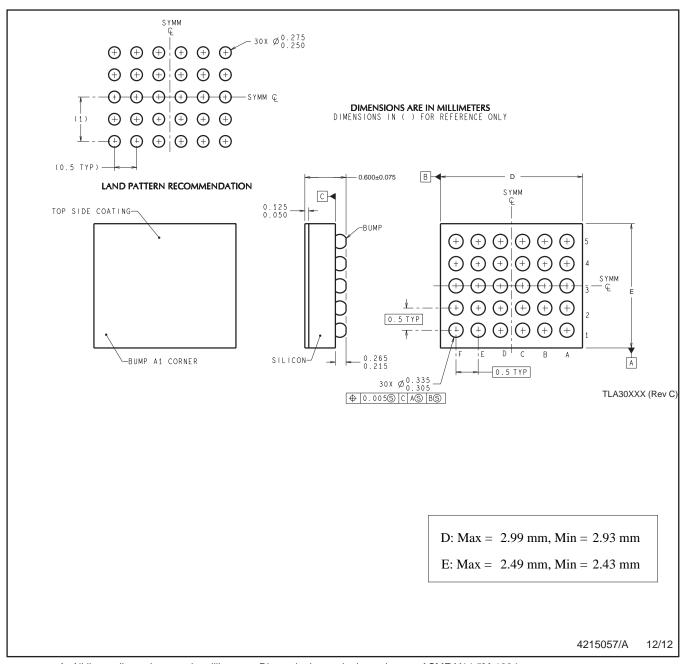

- 30-bump 3.0 x 2.5 mm DSBGA Package

### **APPLICATIONS**

Cellular Handsets

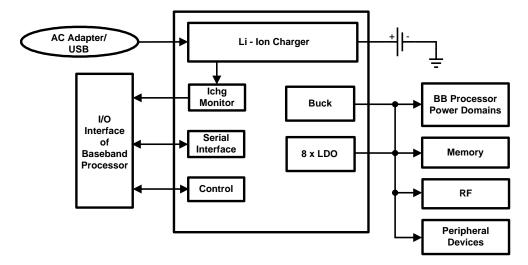

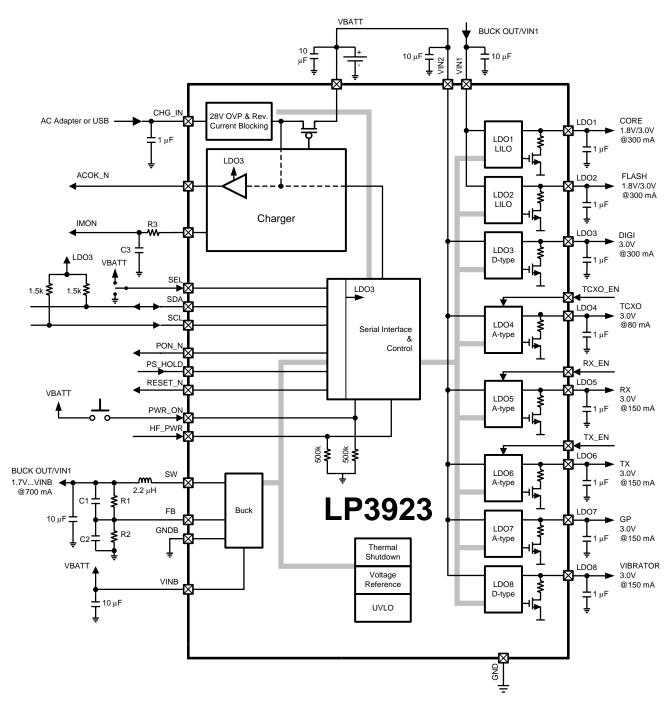

# **System Diagram**

### **KEY SPECIFICATIONS**

- 50 mA to 1200 mA Charging Current

- 3.0V to 5.5V Input Voltage Range

- 135 mV typ. Dropout Voltage @ 300 mA LDOs

- 2% (typ.) Output Voltage accuracy on LDOs

- 700 mA (typ.) Buck Regulator

### DESCRIPTION

The LP3923 is a fully Integrated Power Management Unit (PMU) designed for CDMA cellular phones.

The LP3923 PMU contains a fully integrated Li-Ion battery charger with power FET and over-voltage-protection (OVP), one Buck regulator, 8 low-noise low-dropout (LDO) voltage regulators, and a high-speed serial interface to program on/off conditions and output voltages of individual regulators, and to read status information of the PMU. Two LILO (low-input, low-output) type LDOs with separate power input provide an application option for pre-regulated high efficient power management for longer battery life.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

# **DESCRIPTION (CONTINUED)**

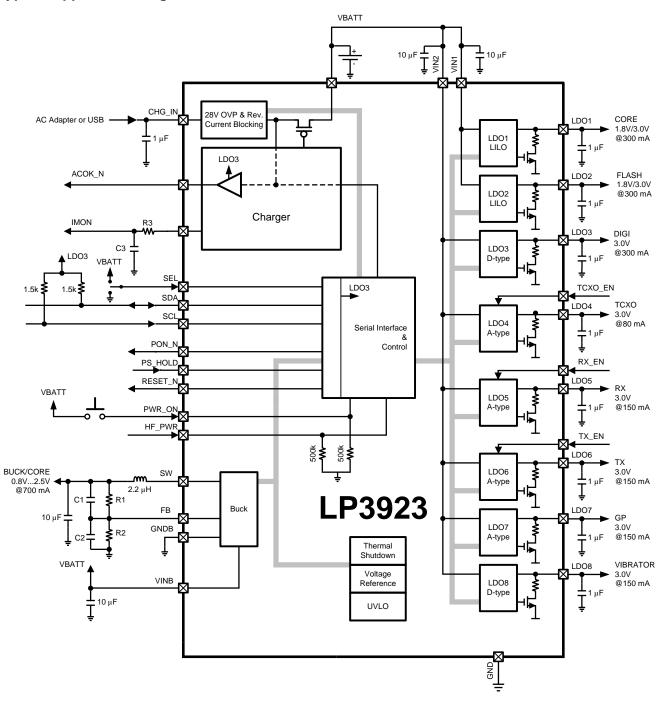

The Li-lon charger can safely charge and maintain a single cell Li-lon battery operating from an AC adapter. The charger integrates a power FET, a reverse current blocking diode, a sense resistor with current monitor output, and requires only a few external components. Charging is thermally regulated to obtain the most efficient charging rate for a given ambient temperature.

A built-in Over-Voltage Protection (OVP) circuit at the charger inputs protects the PMU from input voltages up to +28V, eliminating the need for any external protection circuitry.

Buck regulator has an automatic switch to PFM mode at low load conditions providing very good efficiency at low output currents. An external divider circuitry provides user defined buck output voltage.

A-type LDO regulators provide excellent PSRR and very low noise, 10  $\mu$ V typ., ideally suited for supplying voltage to RF and other analog sections.

# **Typical Application Diagram**

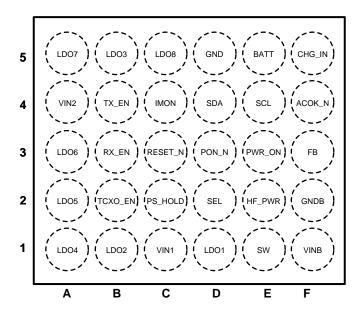

### **Device Pin Diagram**

Table 1. LP3923 PIN DESCRIPTIONS(1)

| Pin Number | Name    | Type | Description                                                                                                       |

|------------|---------|------|-------------------------------------------------------------------------------------------------------------------|

| A1         | LDO4    | Α    | LDO4 Output                                                                                                       |

| A2         | LDO5    | А    | LDO5 Output                                                                                                       |

| А3         | LDO6    | Α    | LDO6 Output                                                                                                       |

| A4         | VIN2    | Р    | Input for LDO3 -LDO8                                                                                              |

| A5         | LDO7    | А    | LDO7 Output                                                                                                       |

| B1         | LDO2    | А    | LDO2 Output                                                                                                       |

| B2         | TCXO_EN | DI   | Enable control input for LDO4. HIGH = Enable, LOW = Disable (SLEEP Mode).                                         |

| B3         | RX_EN   | DI   | Enable control input for LDO5. HIGH = Enable, LOW = Disable.                                                      |

| B4         | TX_EN   | DI   | Enable control input for LDO6. HIGH = Enable, LOW = Disable.                                                      |

| B5         | LDO3    | А    | LDO3 Output                                                                                                       |

| C1         | VIN1    | Р    | Input for LDO1 and LDO2                                                                                           |

| C2         | PS_HOLD | DI   | Power Supply Hold Input                                                                                           |

| C3         | RESET_N | DO   | Reset Output. Pin stays LOW during power up sequence                                                              |

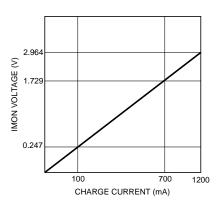

| C4         | IMON    | А    | Charging current monitor output. This pin presents an analog voltage representation of the charging current.      |

| C5         | LDO8    | А    | LDO8 Output                                                                                                       |

| D1         | LDO1    | Α    | LDO1 Output                                                                                                       |

| D2         | SEL     | DI   | LDO1 and LDO2 default voltage selection.                                                                          |

| D3         | PON_N   | DO   | State of PWR_ON inverted. Digital output referred to LDO3.                                                        |

| D4         | SDA     | DI/O | Serial Interface, Data Input/Output Open Drain output, external pull up resistor is needed, typ. 1.5 k $\Omega$ . |

| D5         | GND     | G    | IC Ground pin                                                                                                     |

| E1         | SW      | А    | Buck Output                                                                                                       |

A: Analog Pin D: Digital Pin I: Input Pin DI/O: Digital Input/Output Pin G: Ground O: Output Pin P: Power Connection

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

### Table 1. LP3923 PIN DESCRIPTIONS<sup>(1)</sup> (continued)

|    |        |    | ,                                                                                                                                                                   |

|----|--------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2 | HF_PWR | DI | Power up sequence starts when this pin is set HIGH. Internal 500 $k\Omega$ pull-down resistor.                                                                      |

| E3 | PWR_ON | DI | Power up sequence starts when this pin is set HIGH. Internal 500 k $\Omega$ pull-down resistor.                                                                     |

| E4 | SCL    | DI | Serial Interface Clock input.                                                                                                                                       |

|    |        |    | External pull up resistor is needed, typ. 1.5 k $\Omega$ .                                                                                                          |

| E5 | BATT   | Р  | Main battery connection. Used both as a power connection for current delivery to the battery and as a voltage sense connection to monitor the battery charge level. |

| F1 | VINB   | Р  | Input for Buck                                                                                                                                                      |

| F2 | GNDB   | G  | Power Ground for Buck                                                                                                                                               |

| F3 | FB     | А  | Buck Feedback pin                                                                                                                                                   |

| F4 | ACOK_N | DO | AC Adapter indicator, LOW when V <sub>CHG_IN</sub> is above its trip point                                                                                          |

| F5 | CHG_IN | Р  | DC power input to charger block from AC adapter or USB                                                                                                              |

|    |        |    |                                                                                                                                                                     |

### **Device Description**

The LP3923 Charge Management and Regulator Unit is designed to supply charger and voltage output capabilities for mobile systems, e.g. CDMA handsets. The device provides a Li-lon charging function and 8 or 9 regulated outputs. Communication with the device is via an I<sup>2</sup>C compatible serial interface that allows function control and status read-back.

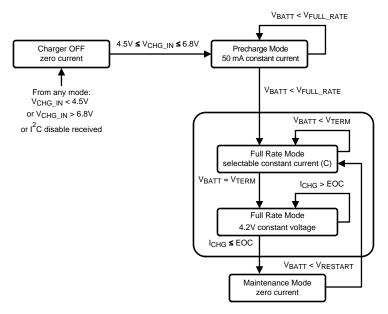

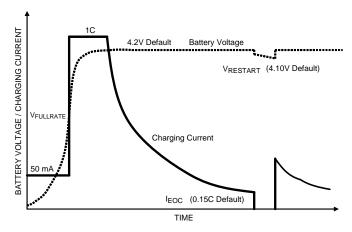

The battery charge management section provides a programmable CC/CV linear charge capability and end of charging current threshold. Following a normal charge cycle a maintenance mode utilizing programmable restart voltage levels enables the battery voltage to be maintained at the correct level. Power dissipation is thermally regulated to obtain optimum charge levels over the ambient temperature range.

### **CHARGER FEATURES**

- Pre-charge, CC, CV and Maintenance modes

- Integrated FET

- Integrated Reverse Current Blocking Diode

- Integrated Sense Resistor

- · Thermal Regulation

- Charging Current Monitor Output

- Programmable charging current 50 mA 1200 mA with 50 mA steps

- Default CC mode current 400 mA

- Pre-charging current fixed 50 mA

- Termination voltage 4.1V, 4.2V (default), 4.3V and 4.4V

- Restart level 50 mV, 100 mV (default), 150 mV and 200 mV below Termination voltage

- End of Charge 0.05C, 0.1C, 0.15C (default) and 0.2C

- Input voltage operating range 4.5 6.8V

Copyright © 2010-2013, Texas Instruments Incorporated

#### **REGULATORS**

Eight low dropout linear regulators provide programmable voltage outputs with current capabilities of 80 mA, 150 mA, and 300 mA as given in the table below. LDO1 and LDO2 are supplied either by the VBATT (SEL=GND) or by buck regulator's output (SEL=VBATT). If the supply voltage is low (supply from buck), then LDO1 and LDO2 are going to be low-input low-output (LILO) LDOs.

Buck regulator can provide 700 mA (typ.) of current. If the buck is used for supplying LDO1 and LDO2 it won't be able to supply external devices. If LDO1 and LDO2 are supplied by VBATT, then buck can be used as an output power channel for digital loading with the default output voltage value of 1.8V

Under voltage lockout oversees device start up with a preset level of 3.0V( typ.).

Draduat Folder Links, 1 Pa

# Table 2. LDOs and Buck Default Voltages (for options LP3923TL/X and LP3923TL/X-VI)

| Device | Туре | Current<br>(mA) | Enable control | Input      | Output(V)          | Startup<br>default | Input     | Output(V)          | Startup<br>default |

|--------|------|-----------------|----------------|------------|--------------------|--------------------|-----------|--------------------|--------------------|

|        |      |                 |                | SEL=BATT   |                    |                    | SEL=GND   |                    |                    |

| Buck   |      | 700             | SI             | VINB=BATT  | 2.0 <sup>(1)</sup> | ON                 | VINB=BATT | 1.8 <sup>(1)</sup> | ON                 |

| LDO1   | LILO | 300             | SI             | VIN1=VBUCK | 1.8                | ON                 | VIN1=BATT | 3                  | ON                 |

| LDO2   | LILO | 300             | SI             | VIN1=VBUCK | 1.8                | ON                 | VIN1=BATT | 3                  | ON                 |

| LDO3   | D    | 300             | -              | VIN2=BATT  | 3                  | ON                 | VIN2=BATT | 3                  | ON                 |

| LDO4   | Α    | 80              | TCXO_EN        | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

| LDO5   | Α    | 150             | RX_EN          | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

| LDO6   | А    | 150             | TX_EN          | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

| LDO7   | А    | 150             | SI             | VIN2=BATT  | 3                  | ON                 | VIN2=BATT | 3                  | ON                 |

| LDO8   | D    | 150             | SI             | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

<sup>(1)</sup> Voltage is set by the external resistors.

## Table 3. LDOs and Buck Default Voltages (for options LP3923TL/X-VB and LP3923TL/X-VC)

| Device | Туре | Current<br>(mA) | Enable control | Input      | Output(V)          | Startup<br>default | Input     | Output(V)          | Startup<br>default |

|--------|------|-----------------|----------------|------------|--------------------|--------------------|-----------|--------------------|--------------------|

|        | •    |                 | •              | SEL=BATT   | •                  |                    | SEL=GND   | ,                  |                    |

| Buck   |      | 700             | SI             | VINB=BATT  | 2.0 <sup>(1)</sup> | ON                 | VINB=BATT | 1.8 <sup>(1)</sup> | ON                 |

| LDO1   | LILO | 300             | SI             | VIN1=VBUCK | 1.8                | ON                 | VIN1=BATT | 3                  | OFF                |

| LDO2   | LILO | 300             | SI             | VIN1=VBUCK | 1.8                | ON                 | VIN1=BATT | 3                  | OFF                |

| LDO3   | D    | 300             | -              | VIN2=BATT  | 3                  | ON                 | VIN2=BATT | 3                  | ON                 |

| LDO4   | Α    | 80              | TCXO_EN        | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

| LDO5   | Α    | 150             | RX_EN          | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

| LDO6   | Α    | 150             | TX_EN          | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

| LDO7   | Α    | 150             | SI             | VIN2=BATT  | 3                  | ON                 | VIN2=BATT | 3                  | ON                 |

| LDO8   | D    | 150             | SI             | VIN2=BATT  | 3                  | OFF                | VIN2=BATT | 3                  | OFF                |

<sup>(1)</sup> Voltage is set by the external resistors.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **Absolute Maximum Ratings**(1)(2)(3)

| •                                              |                                            |

|------------------------------------------------|--------------------------------------------|

| CHG_IN (V <sub>BATT</sub> =2.8-5.5V)           | -0.3V to +28V                              |

| V <sub>BATT</sub> =VIN1-2, BATT, HF_PWR, VINB  | -0.3V to +6.0V                             |

| All other inputs                               | -0.3V to V <sub>BATT</sub> +0.3V, max 6.0V |

| Junction Temperature (T <sub>J-MAX</sub> )     | 150°C                                      |

| Storage Temperature                            | -40°C to +150°C                            |

| Max Continuous Power Dissipation (4)           | Internally Limited                         |

| P <sub>D-MAX</sub> <sup>(5)</sup>              |                                            |

| ESD <sup>(6)</sup>                             |                                            |

| BATT, VIN1, VIN2, HF_PWR, CHG_IN, PWR_ON, VINB | 8 kV HBM                                   |

- (1) All voltages are with respect to the potential at the GND pin.

- (2) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply specified performance limits. For specified performance limits and associated test conditions, see the Electrical Characteristics tables.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) Care must be exercised where high power dissipation is likely. The maximum ambient temperature may have to be derated. Maximum ambient temperature (TA-MAX) is dependant on the maximum operating junction temperature (TJ-MAX-OP), the maximum power dissipation of the device in the application (PD-MAX), and the junction to ambient thermal resistance of the package in the application (θJA). This relationship is given by the following equation: TA-MAX = TJ-MAX-OP (θJA x PD-MAX)

- (5) Internal Thermal Shutdown circuitry protects the device from permanent damage.

- (6) The human-body model is 100 pF discharged through 1.5 kΩ. The machine model is a 200 pF capacitor discharged directly into each pin, MIL-STD-883 3015.7.

# Operating Ratings<sup>(1)(2)</sup>

| _ 1                                                       |                                 |

|-----------------------------------------------------------|---------------------------------|

| CHG_IN <sup>(3)</sup>                                     | 4.5 to 6.8V                     |

| V <sub>BATT</sub> = VIN1-2, BATT, VINB                    | 3.0V to 5.5V                    |

| HF_PWR, PWR_ON                                            | 0V to 5.5V                      |

| ACOK_N, SDA, SCL, RX_EN, TX_EN, TCXO_EN, PS_HOLD, RESET_N | 0V to (V <sub>LDO</sub> + 0.3V) |

| All other pins                                            | 0V to V <sub>BATT</sub> + 0.3V) |

| Junction Temperature (T <sub>J</sub> )                    | -40°C to +125°C                 |

| Ambient Temperature (T <sub>A</sub> ) <sup>(4)</sup>      | −40°C to +85°C                  |

- (1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply specified performance limits. For specified performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pin.

- (3) Full charging current is ensured for CHG\_IN = 4.5 to 6.8V, but particularly at higher input voltages. Increased power dissipation may cause the thermal regulation to limit the current to a safe level, resulting in longer charging time.

- (4) All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

# Thermal Properties (5)

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) (Jedec Standard Thermal PCB) |        |

|---------------------------------------------------------------------------------------|--------|

| DSBGA 30                                                                              | 39°C/W |

<sup>(5)</sup> Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

#### **General Electrical Characteristics**

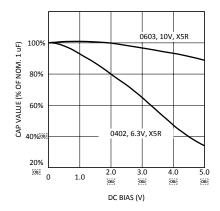

Unless otherwise noted,  $V_{IN}$  (= VIN1 = VIN2 = VINB = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$  =  $C_{VINB}$  = 10  $\mu$ F,  $C_{LDOx}$  = 1  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C.

(1) All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

# **General Electrical Characteristics (continued)**

Unless otherwise noted,  $V_{IN}$  (= VIN1 = VIN2 = VINB = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$  =  $C_{VINB}$  = 10  $\mu$ F,  $C_{LDOx}$  = 1  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C.<sup>(1)</sup>

| Symbol                  | Parameter                         | Conditions                                                                                | <b>T</b>   | Li                         | Units                      |       |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|------------|----------------------------|----------------------------|-------|

| Symbol                  | Parameter                         | Conditions                                                                                | ic circuit |                            | Max                        | Units |

| I <sub>Q(STANDBY)</sub> | Standby Supply<br>Current         | $V_{\text{IN}}$ = 3.6V, UVLO on, internal logic circuit on, all other circuits off.       | 2          |                            | 10                         | μΑ    |

| I <sub>Q(SLEEP)</sub>   | Sleep Mode<br>Current<br>@ 0 load | Buck, LDO1, LDO2, LDO3 and LDO7 enabled                                                   | 130        |                            | 400                        | μΑ    |

| POWER MONI              | TOR FUNCTIONS                     | ,                                                                                         |            |                            |                            |       |

| Battery Under           | -Voltage Lockout                  |                                                                                           |            |                            |                            |       |

| V <sub>UVLO-R</sub>     | Under Voltage<br>Lock-out Rising  | V <sub>IN</sub> Rising                                                                    | 3.00       | 2.85                       | 3.15                       | V     |

| V <sub>UVLO-F</sub>     | Under Voltage<br>Lock-out Falling | V <sub>IN</sub> Falling (LP3923-VC)                                                       | 2.80       | 2.65                       | 2.95                       | V     |

| THERMAL SH              | UTDOWN                            |                                                                                           |            |                            |                            |       |

|                         | Higher Threshold                  | See <sup>(2)</sup>                                                                        | 160        |                            |                            | °C    |

| LOGIC AND C             | ONTROL INPUTS                     |                                                                                           |            |                            |                            |       |

| V <sub>IL</sub>         | Input Low Level                   | PS_HOLD, SDA, SCL, RX_EN, TCXO_EN, TX_EN                                                  |            |                            | 0.25*<br>V <sub>LDO3</sub> | V     |

|                         |                                   | PWR_ON, HF_PWR, SEL                                                                       |            |                            | 0.25*<br>V <sub>BATT</sub> | V     |

| V <sub>IH</sub>         | Input High Level                  | PS_HOLD, SDA, SCL, RX_EN, TCXO_EN, TX_EN                                                  |            | 0.75*<br>V <sub>LDO3</sub> |                            | V     |

|                         |                                   | PWR_ON, HF_PWR, SEL                                                                       |            | 0.75*<br>V <sub>BATT</sub> |                            | V     |

| I <sub>IL</sub>         | Logic Input<br>Current            | All logic inputs except PWR_ON, HF_PWR. $0V \le V_{INPUT} \le V_{BATT}$                   |            | <b>-5</b>                  | +5                         | μA    |

| R <sub>IN</sub>         | Input Resistance                  | PWR_ON and HF_PWR Pull-Down resistance to GND <sup>(3)</sup>                              | 500        |                            |                            | kΩ    |

| LOGIC AND C             | ONTROL OUTPUTS                    |                                                                                           |            |                            |                            |       |

| V <sub>OL</sub>         | Output Low Level                  | PON_N, RESET_N, SDA, ACOK_N<br>I <sub>OUT</sub> = 2 mA                                    |            |                            | 0.25*<br>V <sub>LDO3</sub> | V     |

| V <sub>OH</sub>         | Output High<br>Level              | PON_N, RESET_N, ACOK_N I <sub>OUT</sub> = -2 mA (Not applicable to Open Drain Output SDA) |            | 0.75*<br>V <sub>LDO3</sub> |                            | V     |

<sup>(2)</sup> Ensured by design.

# LDO1, LDO2 (LILO) Electrical Characteristics

Unless otherwise noted, if SEL=GND, then  $V_{IN}$ =VIN1=BATT=3.6V, if SEL=BATT, then  $V_{IN}$ =VIN1=VBUCK, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C. (1)

| Symbol           | Parameter                 | Conditions                               | Typical | Lir | Unit |    |

|------------------|---------------------------|------------------------------------------|---------|-----|------|----|

| Symbol           | 1 arameter Conditions Tyl | Typical                                  | Min     | Max | s    |    |

| V <sub>OUT</sub> | Output Voltage Accuracy   | $I_{OUT} = 1 \text{ mA}, V_{OUT} = 3.0V$ |         | -2  | +2   | %  |

|                  |                           |                                          |         | -3  | +3   | 70 |

|                  | Default Output Voltage    | SEL = GND                                | 3.0     |     |      | V  |

|                  |                           | SEL = BATT                               | 1.8     |     |      | V  |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(3)</sup> Ensured by design.

# LDO1, LDO2 (LILO) Electrical Characteristics (continued)

Unless otherwise noted, if SEL=GND, then  $V_{IN}$ =VIN1=BATT=3.6V, if SEL=BATT, then  $V_{IN}$ =VIN1=VBUCK, GND = 0V,  $C_{V!N1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C.<sup>(1)</sup>

| Compleal               | D                                      |                                                                                         | T       | Limit |     | Unit |

|------------------------|----------------------------------------|-----------------------------------------------------------------------------------------|---------|-------|-----|------|

| Symbol                 | Parameter                              | Conditions                                                                              | Typical | Min   | Max | s    |

| I <sub>OUT</sub>       | Output Current                         | V <sub>INMIN</sub> ≤ V <sub>IN</sub> ≤ 5.5V                                             |         |       | 300 | A    |

|                        | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                   | 600     |       |     | mA   |

| $V_{DO}$               | Dropout Voltage                        | I <sub>OUT</sub> =300 mA <sup>(2)(3)</sup>                                              | 135     |       | 180 | mV   |

| ΔV <sub>OUT</sub>      | Line Regulation                        | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$<br>$I_{\text{OUT}} = 1 \text{ mA}$        | 2       |       |     | mV   |

|                        | Load Regulation                        | 1 mA ≤ I <sub>OUT</sub> ≤ 300 mA                                                        | 5       |       |     |      |

| PSRR                   | Power Supply Ripple<br>Rejection Ratio | $F = 10 \text{ kHz}, C_{OUT} = 1 \mu F, V_{OUT} = 3.0 V, I_{OUT} = 20 \text{ mA}^{(2)}$ | 60      |       |     | dB   |

| t <sub>START-UP</sub>  | Start-Up Time from Shut-<br>down       | $C_{OUT} = 1 \mu F, I_{OUT} = 300 \text{ mA}^{(2)}$                                     | 35      |       |     | μs   |

| T <sub>Transient</sub> | Start-Up Transient<br>Overshoot        | $C_{OUT} = 1 \mu F, I_{OUT} = 300 \text{ mA}^{(2)}$                                     |         |       | 30  | mV   |

<sup>(2)</sup> Ensured by design.

# LDO3 (D-Type) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$ =VIN2=BATT=3.6V, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C.<sup>(1)</sup>

| Symbol                 | Parameter                           | Conditions                                                                       | <b>T</b> | Li  |     |                   |

|------------------------|-------------------------------------|----------------------------------------------------------------------------------|----------|-----|-----|-------------------|

|                        |                                     |                                                                                  | Typical  | Min | Max | Units             |

| V <sub>OUT</sub>       | Output Voltage Accuracy             | I <sub>OUT</sub> = 1 mA, V <sub>OUT</sub> = 3.0V                                 |          | -2  | +2  | 0/                |

|                        |                                     |                                                                                  |          | -3  | +3  | %                 |

|                        | Default Output Voltage              |                                                                                  | 3.0      |     |     | V                 |

| I <sub>OUT</sub>       | Output Current                      | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$                                    |          |     | 300 | ^                 |

|                        | Output Current Limit                | V <sub>OUT</sub> = 0V                                                            | 600      |     |     | mA                |

| $V_{DO}$               | Dropout Voltage                     | I <sub>OUT</sub> = 300 mA <sup>(2)(3)</sup>                                      | 135      |     | 250 | mV                |

| ΔV <sub>OUT</sub>      | Line Regulation                     | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$<br>$I_{\text{OUT}} = 1 \text{ mA}$ | 2        |     |     | mV                |

|                        | Load Regulation                     | 1 mA ≤ I <sub>OUT</sub> ≤ 300 mA                                                 | 5        |     |     |                   |

| e <sub>N</sub>         | Output Noise Voltage                | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 1 $\mu$ F <sup>(2)</sup>    | 35       |     |     | μV <sub>RMS</sub> |

| PSRR                   | Power Supply Ripple Rejection Ratio | $F = 10 \text{ kHz}, \\ C_{OUT} = 1  \mu F, \\ I_{OUT} = 20 \text{ mA}^{(2)}$    | 60       |     |     | dB                |

| t <sub>START-UP</sub>  | Start-Up Time from Shut-down        | C <sub>OUT</sub> = 1 μF, I <sub>OUT</sub> = 300 mA <sup>(2)</sup>                | 35       |     |     | μs                |

| T <sub>Transient</sub> | Start-Up Transient Overshoot        | $C_{OUT} = 1 \mu F, I_{OUT} = 300 \text{ mA}^{(2)}$                              |          |     | 30  | mV                |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(3)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

<sup>(2)</sup> Ensured by design.

Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

# LDO4 (A-Type) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$ =VIN2=BATT=3.6V, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F, TCXO\_EN high. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C. (1)

| 0                      | B                                   | 0 1111                                                                   | <b>T</b> | Li  | I I mit m |                   |

|------------------------|-------------------------------------|--------------------------------------------------------------------------|----------|-----|-----------|-------------------|

| Symbol                 | Parameter                           | Conditions                                                               | Typical  | Min | Max       | Units             |

| V <sub>OUT</sub>       | Output Voltage Accuracy             | I <sub>OUT</sub> = 1 mA, V <sub>OUT</sub> = 3.0V                         |          | -2  | +2        | 0/                |

|                        |                                     |                                                                          |          | -3  | +3        | %                 |

|                        | Default Output Voltage              |                                                                          | 3.0      |     |           | V                 |

| I <sub>OUT</sub>       | Output Current                      | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$                            |          |     | 80        | mA                |

|                        | Output Current Limit                | V <sub>OUT</sub> = 0V                                                    | 400      |     |           |                   |

| $V_{DO}$               | Dropout Voltage                     | I <sub>OUT</sub> =80 mA <sup>(2)(3)</sup>                                | 60       |     | 85        | mV                |

| $\Delta V_{OUT}$       | Line Regulation                     | $V_{INMIN} + \leq V_{IN} \leq 5.5V$ , $I_{OUT} = 1$ mA                   | 1        |     |           | mV                |

|                        | Load Regulation                     | 1 mA ≤ I <sub>OUT</sub> ≤ 80 mA                                          | 5        |     |           | IIIV              |

| e <sub>N</sub>         | Output Noise Voltage                | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 1 µF <sup>(2)</sup> | 10       |     |           | μV <sub>RMS</sub> |

| PSRR                   | Power Supply Ripple Rejection Ratio | F = 10  kHz,<br>$C_{OUT} = 1 \mu F, I_{OUT} = 20 \text{ mA}^{(2)}$       | 75       |     |           | dB                |

| t <sub>START-UP</sub>  | Start-Up Time from Shut-down        | $C_{OUT} = 1 \mu F, I_{OUT} = 80 \text{ mA}^{(2)}$                       | 35       |     |           | μs                |

| T <sub>Transient</sub> | Start-Up Transient Overshoot        | $C_{OUT} = 1 \mu F, I_{OUT} = 80 \text{ mA}^{(2)}$                       |          |     | 30        | mV                |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Ensured by design.

### LDO5, LDO6, LDO7 (A-Type) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$ =VIN2=BATT=3.6V, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F, RX\_EN, TX\_EN high. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C. (1)

| Compleal         | Donomoton.                          | Canditiana                                                                       | Tuminal | Limit |     | l luita           |  |

|------------------|-------------------------------------|----------------------------------------------------------------------------------|---------|-------|-----|-------------------|--|

| Symbol           | Parameter                           | Conditions                                                                       | Typical | Min   | Max | Units             |  |

| V <sub>OUT</sub> | Output Voltage Accuracy             | I <sub>OUT</sub> = 1 mA, V <sub>OUT</sub> = 3.0V                                 |         | -2    | +2  | %                 |  |

|                  |                                     |                                                                                  |         | -3    | +3  | %                 |  |

|                  | Default Output Voltage              |                                                                                  | 3.0     |       |     | V                 |  |

| I <sub>OUT</sub> | Output Current                      | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$                                    |         |       | 150 | A                 |  |

|                  | Output Current Limit                | V <sub>OUT</sub> = 0V                                                            | 400     |       |     | mA                |  |

| $V_{DO}$         | Dropout Voltage                     | I <sub>OUT</sub> = 150 mA <sup>(2)(3)</sup>                                      | 100     |       | 150 | mV                |  |

| $\Delta V_{OUT}$ | Line Regulation                     | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$<br>$I_{\text{OUT}} = 1 \text{ mA}$ | 1       |       |     | mV                |  |

|                  | Load Regulation                     | 1 mA ≤ I <sub>OUT</sub> ≤ 150 mA                                                 | 5       |       |     |                   |  |

| e <sub>N</sub>   | Output Noise Voltage                | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 1 $\mu$ F <sup>(2)</sup>    | 10      |       |     | μV <sub>RMS</sub> |  |

| PSRR             | Power Supply Ripple Rejection Ratio | $F = 10 \text{ kHz}, C_{OUT} = 1 \mu F, I_{OUT} = 20 \text{ mA}^{(2)}$           | 75      |       |     | dB                |  |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Ensured by design.

<sup>(3)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

<sup>(3)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

# LDO5, LDO6, LDO7 (A-Type) Electrical Characteristics (continued)

Unless otherwise noted,  $V_{IN}$ =VIN2=BATT=3.6V, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F, RX\_EN, TX\_EN high. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C.

| Cumbal                 | Darameter                    | Conditions                                             | Tymical | Limit |     | Unito |  |

|------------------------|------------------------------|--------------------------------------------------------|---------|-------|-----|-------|--|

| Symbol                 | Parameter                    | Conditions                                             | Typical | Min   | Max | Units |  |

| t <sub>START-UP</sub>  | Start-Up Time from Shut-down | $C_{OUT} = 1 \mu F$ , $I_{OUT} = 150 \text{ mA}^{(2)}$ | 35      |       |     | μs    |  |

| T <sub>Transient</sub> | Start-Up Transient Overshoot | $C_{OUT} = 1 \mu F, I_{OUT} = 150 \text{ mA}^{(2)}$    |         |       | 30  | mV    |  |

# LDO8 (D-Type) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$ =VIN2=BATT=3.6V, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F,  $C_{LDOx}$ = 1  $\mu$ F. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT}$  +0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C.<sup>(1)</sup>

| 0                                                   | Barrantan                    | O and distance                                                       | T ! !   | Limit |     | Unita         |  |

|-----------------------------------------------------|------------------------------|----------------------------------------------------------------------|---------|-------|-----|---------------|--|

| Symbol                                              | Parameter                    | Conditions                                                           | Typical | Min   | Max | Units         |  |

| V <sub>OUT</sub>                                    | Output Voltage Accuracy      | I <sub>OUT</sub> = 1 mA, V <sub>OUT</sub> = 3.0V                     |         | -2    | +2  | - %           |  |

|                                                     |                              |                                                                      |         | -3    | +3  | 70            |  |

|                                                     | Default Output Voltage       |                                                                      | 3.0     |       |     | V             |  |

| I <sub>OUT</sub>                                    | Output Current               | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$                        |         |       | 150 | ^             |  |

|                                                     | Output Current Limit         | V <sub>OUT</sub> = 0V                                                | 400     |       |     | mA            |  |

| $V_{DO}$                                            | Dropout Voltage              | I <sub>OUT</sub> = 150 mA <sup>(2)(3)</sup>                          | 125     |       | 140 | mV            |  |

| $\Delta V_{OUT}$                                    | Line Regulation              | $V_{INMIN} \le V_{IN} \le 5.5V$ , $I_{OUT} = 1$ mA                   | 2       |       |     | \/            |  |

|                                                     | Load Regulation              | 1 mA ≤ I <sub>OUT</sub> ≤ 150 mA                                     | 5       |       |     | mV            |  |

| e <sub>N</sub>                                      | Output Noise Voltage         | 10 Hz ≤ f ≤ 100 kHz, $C_{OUT} = 1 \mu F^{(2)}$                       | 35      |       |     | $\mu V_{RMS}$ |  |

| PSRR Power Supply Ripple Rejection Ratio            |                              | $F = 10 \text{ kHz}, C_{OUT} = 1 \mu F, I_{OUT} = 20 \text{ mA}$ (2) | 60      |       |     | dB            |  |

| t <sub>START-UP</sub>                               | Start-Up Time from Shut-down | $C_{OUT} = 1 \mu F, I_{OUT} = 150 \text{ mA}^{(2)}$                  | 35      |       |     | μs            |  |

| T <sub>Transient</sub> Start-Up Transient Overshoot |                              | $C_{OUT} = 1 \mu F, I_{OUT} = 150 \text{ mA}^{(2)}$                  |         |       | 30  | mV            |  |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Ensured by design.

# **Buck Converter Electrical Characteristics**

Unless otherwise noted, VIN = VINB = 3.6V, GND = 0V,  $C_{VINB}$  = 10  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A = T_J$  = -40°C to +125°C.<sup>(1)(2)</sup>

| Cumbal               | Danamatan               | Conditions                                                                                                                                                                                          | Tim | Liı   | Units |       |

|----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|

| Symbol               | Parameter               | Conditions                                                                                                                                                                                          | Тур | Min   | Max   | Units |

| $V_{FB}$             | Feedback Voltage (BUCK) | 3.0V ≤V <sub>IN</sub> ≤ 5.5V                                                                                                                                                                        | 0.5 | 0.485 | 0.515 | V     |

| V <sub>OUT,PWM</sub> | Output Voltage          | $3.0V \le V_{\rm IN} \le 5.5V$ , $I_{\rm OUT} = 150 {\rm mA}$<br>External resistor divider<br>accuracy not considered.<br>$R_{\rm FB1} = 390 {\rm k}\Omega$ $R_{\rm FB2} = 150 {\rm k}\Omega^{(3)}$ | 1.8 | 1.746 | 1.854 | V     |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(3)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

<sup>(2)</sup> Buck output voltage accuracy depends on the accuracy of the external feedback resistors. Resistor values should be chosen for the divider network to ensure that at the desired output voltage the FB pin is at the specified value of 0.5V. See Buck Converter Application Information.

<sup>(3)</sup> Ensured by design.

# **Buck Converter Electrical Characteristics (continued)**

Unless otherwise noted, VIN = VINB = 3.6V, GND = 0V,  $C_{VINB}$  = 10  $\mu F$ . Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A = T_J = -40$ °C to +125°C. $^{(1)(2)}$

|                      |                                                                          | Com distance                                                                  | _      | Limit   |      |       |  |

|----------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------|---------|------|-------|--|

| Symbol               | Parameter                                                                | Conditions                                                                    | Тур    | Min Max |      | Units |  |

| V <sub>OUT,PFM</sub> | Output Voltage regulation in PFM mode relative to regulation in PWM mode | See <sup>(3)</sup>                                                            | 1.5    |         |      | %     |  |

| V <sub>OUT</sub>     | Line Regulation                                                          | $3.0V \le V_{IN} \le 5.5V$ , $I_{OUT} = 10$ mA                                | 0.14   |         |      | %/V   |  |

|                      | Load Regulation                                                          | 100 mA ≤ I <sub>OUT</sub> ≤ 300 mA                                            | 0.0013 |         |      | %/mA  |  |

| I <sub>LIM_PWM</sub> | Switch Peak Current Limit                                                | PWM Mode                                                                      | 1150   | 800     | 1500 | mA    |  |

| R <sub>DSON(P)</sub> | P Channel FET on<br>Resistance                                           | V <sub>IN</sub> = 3.6V<br>I <sub>DS</sub> = 100 mA                            | 310    |         |      | mΩ    |  |

| R <sub>DSON(N)</sub> | N Channel FET on<br>Resistance                                           |                                                                               | 160    |         |      | mΩ    |  |

| f <sub>OSC</sub>     | Internal Oscillator<br>Frequency                                         | PWM Mode                                                                      | 2      | 1.9     | 2.1  | MHz   |  |

| Efficiency           |                                                                          | I <sub>OUT</sub> = 5 mA, PFM Mode<br>V <sub>OUT</sub> = 1.8V <sup>(3)</sup>   | 88     |         |      | 0/    |  |

|                      |                                                                          | I <sub>OUT</sub> = 300 mA, PWM Mode<br>V <sub>OUT</sub> = 1.8V <sup>(3)</sup> | 90     |         |      | - %   |  |

| T <sub>STUP</sub>    | Start Up Time                                                            | $I_{OUT} = 0^{(3)}, V_{OUT} = 1.8V$                                           | 140    |         |      | μs    |  |

### **Charger Electrical Characteristics**

Unless otherwise noted,  $V_{CHG\_IN} = 5V$ ,  $V_{IN} = BATT = 3.6V$ ,  $C_{CHG\_IN} = 1 \mu F$ ,  $V_{BATT} = 30 \mu F$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A = T_{IJ} = -25$ °C to +85°C.  $^{(1)(2)}$

| Symbol                | Parameter                                      | Conditions                                                                                                                | Typical | Limit |       | Units |

|-----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|

|                       |                                                |                                                                                                                           |         | Min   | Max   |       |

| V <sub>CHG_IN</sub>   | AC wall adapter input voltage operating range  |                                                                                                                           |         | 4.5   | 6.8   | V     |

|                       | CHG_IN OK trip-point.                          | V <sub>CHG_IN</sub> - V <sub>BATT</sub> (Rising)                                                                          | 150     |       |       | \/    |

| V <sub>OK_CHG</sub>   |                                                | V <sub>CHG_IN</sub> - V <sub>BATT</sub> (Falling)                                                                         | 40      |       |       | mV    |

|                       | Battery charging                               | V <sub>TERM</sub> = 4.2V, I <sub>CHG</sub> = 50 mA                                                                        |         | -0.35 | +0.35 |       |

| $V_{TERM}$            | termination voltage tolerance                  | V <sub>TERM</sub> is measured at 10% of the programmed I <sub>CHG</sub> current                                           |         | -1    | +1    | %     |

| I <sub>CHG</sub>      | CHG_IN programmable full-rate charging current | $6.8V \ge V_{CHG\_IN} \ge 4.5V$<br>$V_{BATT} < V_{CHG\_IN} - V_{OK\_CHG}$<br>$V_{FULL\_RATE} < V_{BATT} < V_{TERM}^{(3)}$ |         | 50    | 1200  | mA    |

|                       | Full rate charging current tolerance           | I <sub>CHG</sub> = 400 mA                                                                                                 |         | -10   | +10   | %     |

| I <sub>PREEQUAL</sub> | Pre-charging current                           | 2.2V < V <sub>BATT</sub> < V <sub>FULL_RATE</sub>                                                                         | 50      | 30    | 70    | mA    |

| $V_{FULL\_RATE}$      | Full-rate qualification threshold              | V <sub>BATT</sub> rising, transition from pre-charging to full-rate charging                                              | 2.8     | 2.7   | 2.9   | V     |

|                       |                                                | V <sub>BATT</sub> rising, transition from pre-charging to full-rate charging (LP3923-VC)                                  | 3.0     | 2.9   | 3.1   | V     |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(2)</sup> Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

<sup>(3)</sup> Full charging current is ensured for CHG\_IN = 4.5 to 6.8V, but particularly at higher input voltages. Increased power dissipation may cause the thermal regulation to limit the current to a safe level, resulting in longer charging time.

# **Charger Electrical Characteristics (continued)**

Unless otherwise noted,  $V_{CHG\_IN} = 5V$ ,  $V_{IN} = BATT = 3.6V$ ,  $C_{CHG\_IN} = 1 \mu F$ ,  $V_{BATT} = 30 \mu F$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A = T_J = -25$ °C to +85°C.  $^{(1)(2)}$

| Symbol               | Parameter                                       | Conditions                                                      | Typical  | Limit |       | Units |

|----------------------|-------------------------------------------------|-----------------------------------------------------------------|----------|-------|-------|-------|

|                      |                                                 |                                                                 |          | Min   | Max   |       |

| I <sub>EOC</sub>     | End-of-charging current, % of full-rate current | 0.1C option selected                                            | 10       |       |       | %     |

| V <sub>RESTART</sub> | Restart threshold voltage                       | From V <sub>TERM</sub> voltage (4.2V, -100 mV options selected) | -100     | -70   | -130  | mV    |

| I <sub>MON</sub>     | I <sub>MON</sub> Voltage 1                      | I <sub>CHG</sub> = 100 mA                                       | 0.247    |       |       | V     |

|                      | I <sub>MON</sub> Voltage 2                      | I <sub>CHG</sub> = 400 mA                                       | 0.988    | 0.840 | 1.127 | V     |

| C <sub>BATT</sub>    | Capacitance on BATT                             | See <sup>(4)</sup>                                              |          | 30    | 1000  | μF    |

| T <sub>REG</sub>     | Regulated junction temperature                  | See <sup>(4)</sup>                                              | 115      |       |       | °C    |

| Detection and        | d Timing (one combined time                     | r)                                                              |          |       |       | •     |

| T <sub>POK</sub>     | Power OK deglitch time                          | V <sub>CHG</sub> > V <sub>BATT</sub> + V <sub>OK_CHG</sub>      | 30       |       |       | ms    |

| T <sub>PC_FULL</sub> | Deglitch time                                   | From pre-charging to full-rate charging                         | 210      |       |       | ms    |

| T <sub>CHG</sub>     | Charge timer                                    | Pre-charge mode                                                 | 1        |       |       |       |

|                      |                                                 |                                                                 | disabled |       |       |       |

|                      |                                                 |                                                                 | 2        |       |       | Hrs   |

|                      |                                                 | CC mode/CV mode (combined timer)                                | 5        |       |       |       |

|                      |                                                 |                                                                 | 8        |       |       |       |

| T <sub>EOC</sub>     | Deglitch time for end- of-<br>charge transition |                                                                 | 210      |       |       | ms    |

<sup>(4)</sup> Ensured by design.

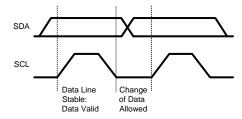

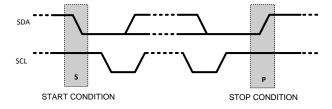

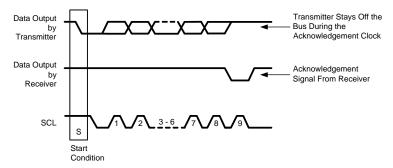

#### Serial Interface

Unless otherwise noted,  $V_{IN}$  = BATT = 3.6V, GND = 0V,  $C_{VIN1-2}$  = 10  $\mu$ F  $C_{LDOx}$  = 1  $\mu$ F and  $V_{LDO3}$  = 3.0V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_A$  =  $T_J$  = -40°C to +125°C. (1)(2)

| 0                      | Paramatan.                                                                                                 | O and distance | <b>T</b> | Limit |     | Unit |

|------------------------|------------------------------------------------------------------------------------------------------------|----------------|----------|-------|-----|------|

| Symbol                 | Parameter                                                                                                  | Conditions     | Тур      | Min   | Max | s    |

| f <sub>CLK</sub>       | Clock Frequency                                                                                            |                |          |       | 400 | kHz  |

| t <sub>BF</sub>        | Bus-Free Time between START and STOP                                                                       |                |          | 1.3   |     | μs   |

| t <sub>HOLD</sub>      | Hold Time Repeated START Condition                                                                         |                |          | 0.6   |     | μs   |

| t <sub>CLK-LP</sub>    | CLK Low Period                                                                                             |                |          | 1.3   |     | μs   |

| t <sub>CLK-HP</sub>    | CLK High Period                                                                                            |                |          | 0.6   |     | μs   |

| t <sub>SU</sub>        | Set-Up Time Repeated START Condition                                                                       |                |          | 0.6   |     | μs   |

| t <sub>DATA-HOLD</sub> | Data Hold Time                                                                                             |                |          | 50    |     | ns   |

| t <sub>DATA-SU</sub>   | Data Set-Up Time                                                                                           |                |          | 100   |     | ns   |

| t <sub>SU</sub>        | Set-Up Time for STOP Condition                                                                             |                |          | 0.6   |     | μs   |

| t <sub>TRANS</sub>     | Maximum Pulse Width of Spikes that Must Be<br>Suppressed by the Input Filter of Both DATA & CLK<br>Signals |                | 50       |       |     | ns   |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(2)</sup> Ensured by design.

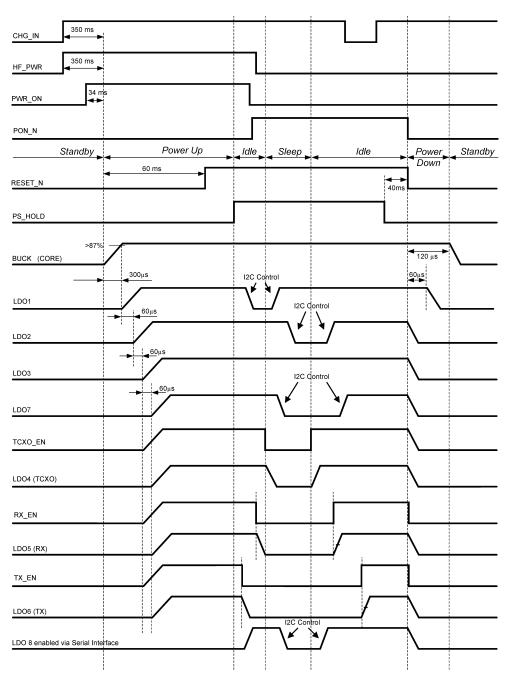

### **POWER UP AND POWER DOWN SEQUENCES**

- (1) CHG\_IN is edge sensitive and HF\_PWR is level sensitive at startup in STANDBY mode and level sensitive in POWER-ON-RESET mode.

- (2) PWR\_ON is level sensitive at startup. PS\_HOLD must be asserted before PWR\_ON goes LOW to keep PMU powered. PWR\_ON input is not monitored after PMU is powered up (PS\_HOLD asserted).

- (3) PON\_N is a direct inversion of PWR\_ON input when LDO3 is powered up (no power-on switch debouncing on PON\_N output).

- (4) The input signal which activates Power Up sequence (either PWR\_ON or CHG\_IN or HF\_PWR) must be on when PS\_HOLD is asserted.

- (5) Time delay between the PS\_HOLD going low and the start of Power Down sequence depends on PS\_HOLD\_DELAY setting (0=35ms, 1=350ms) (typ.).

Figure 1. Power Up and Power Down Timing Diagram

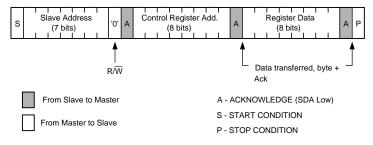

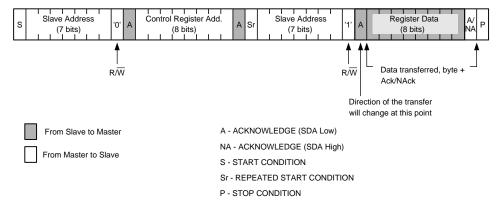

# LP3923 Serial Port Communication: Slave Address Code: 7h'7E

# Table 4. Control Registers<sup>(1)</sup>

|       | Table 4. Control Registers                                                                  |                   |                  |                |                         |                         |                   |                   |                    |

|-------|---------------------------------------------------------------------------------------------|-------------------|------------------|----------------|-------------------------|-------------------------|-------------------|-------------------|--------------------|

| Addr  | Register (Default value)*                                                                   | D7                | D6               | D5             | D4                      | D3                      | D2                | D1                | D0                 |

| 8h'00 | OP_EN1<br>(01000111)                                                                        | BUCK_<br>PWM      | EN_<br>BUCK      | Х              | X                       | EN_LDO8                 | EN_LDO7           | EN_LDO2           | EN_LDO1            |

| 8h'01 | LDO1PGM O/P<br>SEL=BATT<br>(00001100)<br>SEL=GND<br>(00011011)                              | X                 | Х                | Х              | LDO1_<br>V1_OP[4]       | LDO1_<br>V1_OP[3]       | LDO1_<br>V1_OP[2] | LDO1_<br>V1_OP[1] | LDO1_<br>V1_OP[0]  |

| 8h'02 | LDO2 Program O/P<br>SEL=BATT<br>(00001100)<br>SEL=GND<br>(00011011)                         | X                 | X                | Х              | LDO2_<br>V2_OP[4]       | LDO2_<br>V2_OP[3]       | LDO2_<br>V2_OP[2] | LDO2_<br>V2_OP[1] | LDO2_<br>V2_OP[0]  |

| 8h'03 | LDO3 PGM O/P<br>(00011011)                                                                  | X                 | X                | X              | LDO3_<br>V3_OP[4]       | LDO3_<br>V3_OP[3]       | LDO3_<br>V3_OP[2] | LDO3_<br>V3_OP[1] | LDO3_<br>V3_OP[0]  |

| 8h'04 | LDO4 PGM O/P<br>(00011011)                                                                  | X                 | Х                | X              | LDO4_<br>V4_OP[4]       | LDO4_<br>V4_OP[3]       | LDO4_<br>V4_OP[2] | LDO4_<br>V4_OP[1] | LDO4_<br>V4_OP[0]  |

| 8h'05 | LDO5 PGM O/P<br>(00011011)                                                                  | X                 | Х                | X              | LDO5_<br>V5_OP[4]       | LDO5_<br>V5_OP[3]       | LDO5_<br>V5_OP[2] | LDO5_<br>V5_OP[1] | LDO5_<br>V5_OP[0]  |

| 8h'06 | LDO6 PGM O/P<br>(00011011)                                                                  | X                 | Х                | X              | LDO6_<br>V6_OP[4]       | LDO6_<br>V6_OP[3]       | LDO6_<br>V6_OP[2] | LDO6_<br>V6_OP[1] | LDO6_<br>V6_OP[0]  |

| 8h'07 | LDO7 PGM O/P<br>(00011011)                                                                  | X                 | Х                | X              | LDO7_<br>V7_OP[4]       | LDO7_<br>V7_OP[3]       | LDO7_<br>V7_OP[2] | LDO7_<br>V7_OP[1] | LDO7_<br>V7_OP[0]  |

| 8h'08 | LDO8 PGM O/P<br>(00011011)                                                                  | X                 | Х                | X              | LDO8_<br>V8_OP[4]       | LDO8_<br>V8_OP[3]       | LDO8_<br>V8_OP[2] | LDO8_<br>V8_OP[1] | LDO8_<br>V8_OP[0]  |

| 8h'0C | Status1<br>Trig<br>PWR_ON(10000010)<br>Trig<br>HF_PWR(01000010)<br>TrigCHG_IN<br>(00100010) | PWR_ON<br>TRIG    | HF_PWR<br>TRIG   | CHG_IN<br>TRIG | x                       | TSD_H                   | TSD_L             | FF                | x                  |

| 8h'10 | CHARGER Control 1<br>(00010 001)                                                            | х                 | X                | Force_<br>EOC  | PROG_<br>CHGTIME[1<br>] | PROG_<br>CHGTIME[0<br>] | EN_EOC            | Х                 | EN_CHG             |

| 8h'11 | CHARGER Control 2<br>(00000111)                                                             | х                 | Х                | Х              | PROG_<br>ICHG[4]        | PROG_<br>ICHG[3]        | PROG_<br>ICHG[2]  | PROG_<br>ICHG[1]  | PROG_<br>ICHG[0]   |

| 8h'12 | CHARGER Control 3<br>(00011001)                                                             | Х                 | Х                | VTERM[<br>1]   | VTERM[0]                | PROG_<br>EOC[1]         | PROG_<br>EOC[0]   | PROG_<br>VSTRT[1] | PROG_<br>VSTART[0] |

| 8h'13 | CHARGER Status 1<br>(0000 0000)                                                             | BATT_<br>OVER_OUT | CHGIN_<br>OK_OUT | EOC            | TOUT_<br>FULLRATE       | TOUT_<br>PRECHG         | х                 | FULLRATE          | PRECHG             |

| 8h'14 | CHARGER Status 2<br>(00000000)                                                              | Х                 | Х                | Х              | Х                       | Х                       | Х                 | TOUT_<br>CONSTV   | BAD_BATT           |

| 8h'1C | MISC Control1<br>(0000000)                                                                  | Х                 | Х                | Х              | Х                       | Х                       | Х                 | EN_<br>APU_TSD    | PS_HOLD_<br>DELAY  |

<sup>(1)</sup> X — Not used.

**BOLD** locations are Read Only type.

NOTE: All Control registers apart from Charger Control registers (h'10 — h'12) are reset to default at the end of every Power Down sequence.

# Table 5. Register 0x00 - OP\_EN1

| BUCK_PWM | 0 - Auto mode PFM/PWM<br>1 - Buck forced PWM mode                                                                                  |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| EN_BUCK  | 0 - disable Buck<br>1 - enable Buck                                                                                                |

| EN_LDO8  | 0 - disable LDO8<br>1 - enable LDO8                                                                                                |

| EN_LDO7  | 0 - disable LDO7<br>1 - enable LDO7                                                                                                |

| EN_LDO2  | 0 - disable LDO2 on LP3923TL/X and -VI; enable on LP3923TL/X-VB<br>1 - enable LDO2 on LP3923TL/X and -VI; disable on LP3923TL/X-VB |

| EN_LDO1  | 0 - disable LDO1 on LP3923TL/X and -VI; enable on LP3923TL/X-VB<br>1 - enable LDO1 on LP3923TL/X and -VI; disable on LP3923TL/X-VB |

# Table 6. Register 0x0C (Read Only) - Status 1

| PWR_ON_TRIG | 0 - system was not powered on by PWR_ON input 1 - system was powered on by PWR_ON input                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

| HF_PWR_TRIG | 0 - system was not powered on by HF_PWR input 1 - system was powered on by HF_PWR input                                           |

| CHG_IN_TRIG | 0 - system was not powered on by connecting AC adapter 1 - system was powered on by connecting AC adapter                         |

| TSD_H       | 0 - Thermal Shutdown threshold not exceeded 1 - Thermal Shutdown threshold exceeded (cause Power Down sequence)                   |

| TSD_L       | 0 - chip temperature has not been over TSD early warning threshold 1 - chip temperature has been over TSD early warning threshold |

| FF          | 0 - Buck output voltage out of range 1 - Buck output voltage within range                                                         |

# Table 7. Register 0x13 (Read Only) - CHARGER Status 1

| BATT_OVER_OUT | 0 - battery voltage is in normal range 1- battery voltage is over critical limit                 |

|---------------|--------------------------------------------------------------------------------------------------|

| CHGIN_OK_OUT  | 0 - voltage is not connected to AC adapter input 1 - voltage is connected to AC adapter input    |

| EOC           | 0 - charging current is above EOC current level 1 - charging current is below EOC current level  |

| TOUT_FULLRATE | o - no time out occurred in Constant Current mode     time out occurred in Constant Current mode |

| TOUT_PRECHG   | 0 - no time out occurred in pre-charge mode 1 - time out occurred in pre-charge mode             |

| FULLRATE      | 0 - charger is not in CC or CV mode<br>1 - charger is in CC or CV mode                           |

| PRECHG        | 0 - charger is not in pre-charge mode<br>1 - charger is in pre-charge mode                       |

# Table 8. Register 0x14 (Read Only) - CHARGER Status 2

| TOUT_CONSTV | 0 - no time out occurred in Constant Voltage mode 1 - time out occurred in Constant Voltage mode |

|-------------|--------------------------------------------------------------------------------------------------|

| BAD_BATT    | 0 - charger has not detected a bad battery 1 - charger has detected a bad battery                |

### Table 9. Register 0x1C - MISC Control 1

| EN_APU_TSD    | 0 - do not start PMU automatically after TSD event      |

|---------------|---------------------------------------------------------|

|               | 1 - start PMU automatically after TSD event             |

| PS_HOLD_DELAY | 0 - PMU powerdown after PS_HOLD has been low for 35 ms  |

|               | 1 - PMU powerdown after PS_HOLD has been low for 350 ms |

### LDO OUTPUT VOLTAGE PROGRAMMING

The following table summarizes the supported output voltages for LP3923. Default voltages after start-up sequences have been highlighted in **bold**.

| Data Code LDO_Vx_OP[x] | LDOx [V]            | Data Code LDO_Vx_OP[x] | LDOx [V]                   |

|------------------------|---------------------|------------------------|----------------------------|

| 8h'00                  | 1.20                | 8h'10                  | 2.20                       |

| 8h'01                  | 1.25                | 8h'11                  | 2.40                       |

| 8h'02                  | 1.30                | 8h'12                  | 2.50                       |

| 8h'03                  | 1.35                | 8h'13                  | 2.60                       |

| 8h'04                  | 1.40                | 8h'14                  | 2.65                       |

| 8h'05                  | 1.45                | 8h'15                  | 2.70                       |

| 8h'06                  | 1.50                | 8h'16                  | 2.75                       |

| 8h'07                  | 1.55                | 8h'17                  | 2.80                       |

| 8h08                   | 1.60                | 8h'18                  | 2.85                       |

| 8h'09                  | 1.65                | 8h'19                  | 2.90                       |

| 8h'0A                  | 1.70                | 8h'1A                  | 2.95                       |

| 8h'0B                  | 1.75                | 8h'1B                  | <b>3.00</b> <sup>(1)</sup> |