SBVS010D – JANUARY 2000 – REVISED SEPTEMBER 2005

# DMOS 500mA Low-Dropout Regulator

# **FEATURES**

- NEW DMOS TOPOLOGY: Ultra Low Dropout Voltage: 115mV Typ at 500mA and 3.3V Output Output Capacitor NOT Required for Stability

- FAST TRANSIENT RESPONSE

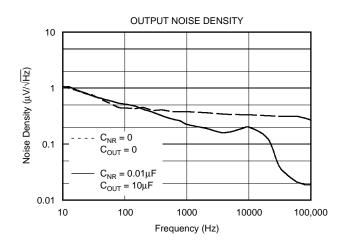

- VERY LOW NOISE: 33µVrms

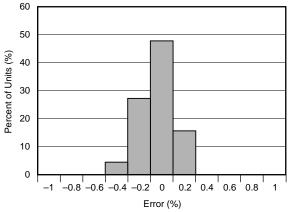

- HIGH ACCURACY: ±2% max

- HIGH EFFICIENCY:

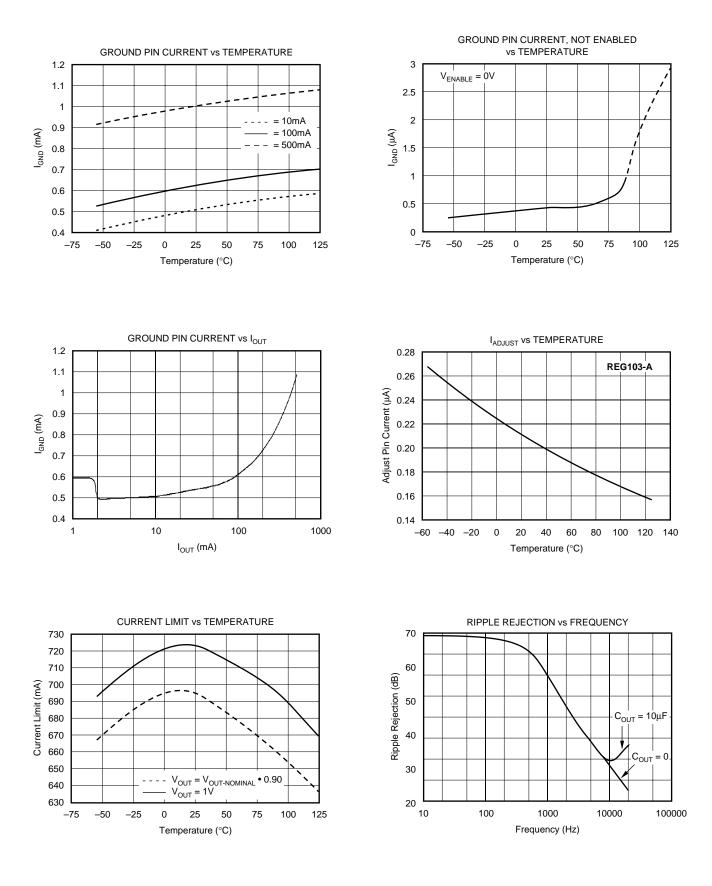

I<sub>GND</sub> = 1mA at I<sub>out</sub> = 500mA

Not Enabled: I<sub>GND</sub> = 0.5μA

- 2.5V, 2.7V, 3.0V, 3.3V, 5.0V, AND ADJUSTABLE OUTPUT VERSIONS

- FOLDBACK CURRENT LIMIT

- THERMAL PROTECTION

- OUTPUT VOLTAGE ERROR INDICATOR<sup>(1)</sup>

- SMALL SURFACE-MOUNT PACKAGES: SOT223-5, DDPAK-5, SO-8

# **APPLICATIONS**

- PORTABLE COMMUNICATION DEVICES

- BATTERY-POWERED EQUIPMENT

- PERSONAL DIGITAL ASSISTANTS

- MODEMS

- BAR-CODE SCANNERS

- BACKUP POWER SUPPLIES

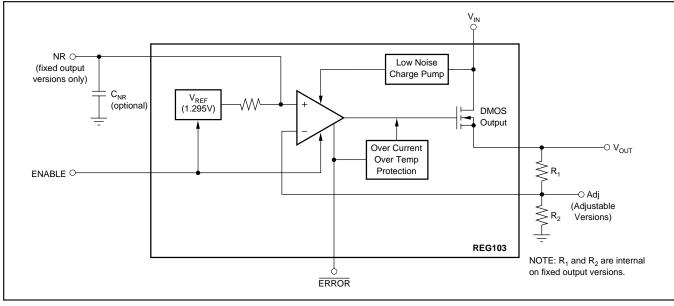

# DESCRIPTION

The REG103 is a family of low-noise, low-dropout, linear regulators with low ground pin current. Its new DMOS topology provides significant improvement over previous designs, including low-dropout voltage (only 115mV typ at full load), and better transient performance. In addition, no output capacitor is required for stability, unlike conventional low-dropout regulators that are difficult to compensate and require expensive low ESR capacitors greater than 1 $\mu$ F.

Typical ground pin current is only 1mA (at  $I_{OUT} = 500$ mA) and drops to 0.5µA in *not enabled* mode. Unlike regulators with PNP pass devices, quiescent current remains relatively constant over load variations and under dropout conditions.

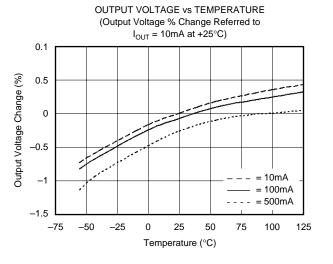

The REG103 has very low output noise (typically  $33\mu$ Vrms for V<sub>OUT</sub> = 3.3V with C<sub>NR</sub> = 0.01 $\mu$ F), making it ideal for use in portable communications equipment. On-chip trimming results in high output voltage accuracy. Accuracy is maintained over temperature, line, and load variations. Key parameters are tested over the specified temperature range (-40°C to +85°C).

The SO-8 version of the REG103 has an ERROR pin that provides a *power good* flag, indicating the regulator is in regulation. The REG103 is well protected—internal circuitry provides a current limit that protects the load from damage. Thermal protection circuitry keeps the chip from being damaged by excessive temperature. In addition to the SO-8 package, the REG103 is also available in the DDPAK and the SOT223-5.

NOTE: (1) SO-8 Package Only. (2) Optional.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Supply Input Voltage, V <sub>IN</sub>          | –0.3V to 16V             |

|------------------------------------------------|--------------------------|

| Enable Input Voltage, V <sub>EN</sub>          | –0.3V to V <sub>IN</sub> |

| Feedback Voltage, V <sub>FB</sub>              | –0.3V to 6.0V            |

| NR Pin Voltage, V <sub>NR</sub>                | –0.3V to 6.0V            |

| Error Flag Output                              | –0.3V to 6V              |

| Error Flag Current                             | 2mA                      |

| Output Short-Circuit Duration                  | Indefinite               |

| Operating Temperature Range                    | –55°C to +125°C          |

| Storage Temperature Range                      | –65°C to +150°C          |

| Junction Temperature                           | –55°C to +150°C          |

| Lead Temperature (soldering, 3s, SO-8, SOT, ar | nd DDPAK) +240°C         |

| ESD Rating: HBM (V <sub>OUT</sub> to GND)      | 1.5kV                    |

| HBM (All other pins)                           | 2kV                      |

| CDM                                            | 500V                     |

|                                                |                          |

NOTE: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability.

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT           | V <sub>OUT</sub>                                                         |

|-------------------|--------------------------------------------------------------------------|

| REG103xx-yyyy/zzz | XX is package designator.                                                |

|                   | YYYY is typical output voltage (5 = 5.0V, 2.85 = 2.85V, A = Adjustable). |

|                   | ZZZ is package quantity.                                                 |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

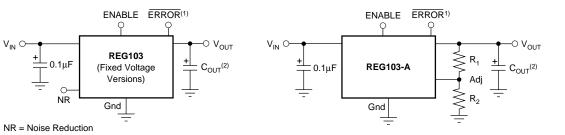

#### PIN CONFIGURATIONS

# **ELECTRICAL CHARACTERISTICS**

### Boldface limits apply over the specified temperature range, $T_J = -40^{\circ}C$ to $+85^{\circ}C$ .

At  $T_J = +25^{\circ}C$ ,  $V_{IN} = V_{OUT} + 1V$  ( $V_{OUT} = 3.0V$  for REG103-A),  $V_{ENABLE} = 2V$ ,  $I_{OUT} = 10$ mA,  $C_{NR} = 0.01\mu$ F, and  $C_{OUT} = 0.1\mu$ F<sup>(1)</sup>, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                    |                                                                                   |                                                                                                                                                       | RE                                                             |                                                                            |                                        |                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|--------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                          |                                                                                   | CONDITION                                                                                                                                             | MIN                                                            | TYP                                                                        | MAX                                    | UNITS                                      |

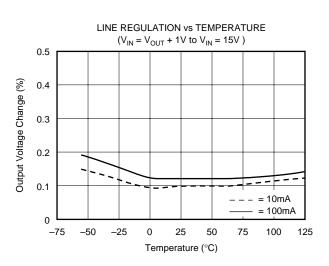

| OUTPUT VOLTAGE           Output Voltage Range           REG103-2.5           REG103-2.7           REG103-3.0           REG103-5           REG103-5           REG103-A           Reference Voltage           Adjust Pin Current           Accuracy           T = -40°C to +85°C           vs Temperature           vs Line and Load | V <sub>out</sub><br>V <sub>ref</sub><br>I <sub>adj</sub><br>dV <sub>out</sub> /dT | <b>T</b> <sub>J</sub> = − <b>40°C to +85°C</b><br>I <sub>OUT</sub> = 10mA to 500mA, V <sub>IN</sub> = (V <sub>OUT</sub> + 0.7V) to 15V                | V <sub>REF</sub>                                               | 2.5<br>2.7<br>3.0<br>3.3<br>5<br>1.295<br>0.2<br>±0.5<br><b>70</b><br>±0.5 | 5.5<br>1<br>±2<br>± <b>2.8</b><br>±2.5 | V<br>V<br>V<br>V<br>V<br>μΑ<br>%<br>%<br>% |

| $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                                                                                                                                                                                                                                                                             |                                                                                   | $V_{IN} = (V_{OUT} + 0.9V)$ to 15V                                                                                                                    |                                                                |                                                                            | ±3.5                                   | %                                          |

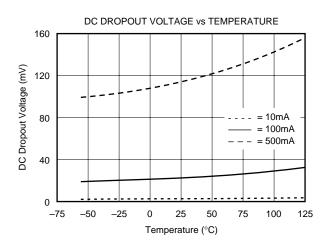

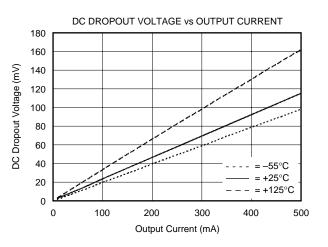

| $\begin{array}{l} \text{DC DROPOUT VOLTAGE}^{(2, \ 3)} \\ \text{For all models except 5V} \\ \text{For 5V model} \\ \text{For all models except 5V} \\ \text{T}_J = -40^\circ \text{C to } +85^\circ \text{C} \\ \text{For 5V models} \\ \text{T}_J = -40^\circ \text{C to } +85^\circ \text{C} \end{array}$                       | V <sub>DROP</sub>                                                                 | I <sub>OUT</sub> = 10mA<br>I <sub>OUT</sub> = 500mA<br>I <sub>OUT</sub> = 500mA<br>I <sub>OUT</sub> = <b>500mA</b><br>I <sub>OUT</sub> = <b>500mA</b> |                                                                | 3<br>115<br>160                                                            | 25<br>200<br>250<br><b>230</b><br>280  | mV<br>mV<br>mV<br>mV                       |

| $\label{eq:Voltage} \begin{array}{l} \hline \textbf{Voltage NOISE} \\ f = 10 Hz \mbox{ to } 100 \mbox{ Hz} \\ \hline \mbox{ Without } C_{NR} \mbox{ (all models)} \\ \hline \mbox{ With } C_{NR} \mbox{ (all fixed voltage models)} \end{array}$                                                                                   | V <sub>n</sub>                                                                    | C <sub>NR</sub> = 0, C <sub>OUT</sub> = 0<br>C <sub>NR</sub> = 0.01μF, C <sub>OUT</sub> = 10μF                                                        | 30<br>10                                                       | )μVrms/V • V <sub>OL</sub><br>)μVrms/V • V <sub>OL</sub>                   | т<br>лт                                | μVrms<br>μVrms                             |

| OUTPUT CURRENT<br>Current Limit <sup>(4)</sup><br>T <sub>J</sub> = -40°C to +85°C                                                                                                                                                                                                                                                  | I <sub>CL</sub>                                                                   |                                                                                                                                                       | 550<br><b>500</b>                                              | 700                                                                        | 950<br><b>1000</b>                     | mA<br>mA                                   |

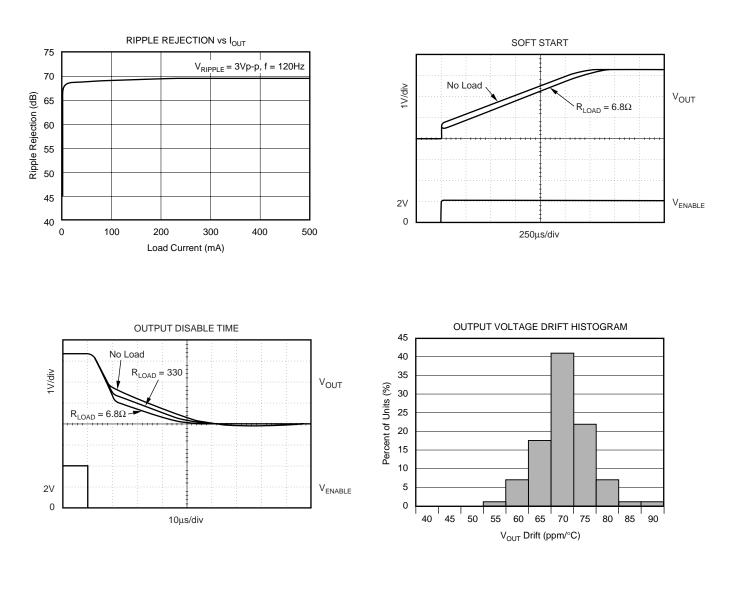

| <b>RIPPLE REJECTION</b><br>f = 120Hz                                                                                                                                                                                                                                                                                               |                                                                                   |                                                                                                                                                       |                                                                | 65                                                                         |                                        | dB                                         |

| ENABLE CONTROL<br>V <sub>ENABLE</sub> HIGH (output enabled)<br>V <sub>ENABLE</sub> LOW (output disabled)<br>I <sub>ENABLE</sub> HIGH (output enabled)<br>I <sub>ENABLE</sub> LOW (output disabled)<br>Output Disable Time<br>Output Enable Soft Start Time                                                                         | V <sub>enable</sub><br>I <sub>enable</sub>                                        | $V_{\text{ENABLE}} = 2V \text{ to } V_{\text{IN}}, V_{\text{IN}} = 2.1V \text{ to } 6.5^{(5)}$<br>$V_{\text{ENABLE}} = 0V \text{ to } 0.5V$           | 2<br>-0.2                                                      | 1<br>2<br>50<br>1.5                                                        | V <sub>IN</sub><br>0.5<br>100<br>100   | V<br>V<br>nA<br>nA<br>μs<br>ms             |

| ERROR FLAG <sup>(6)</sup><br>Current, Logic HIGH (open drain)—Nor<br>Voltage, Logic LOW—On Error                                                                                                                                                                                                                                   | rmal Operation                                                                    | $V_{IN} = V_{ERROR} = V_{OUT} + 1V$<br>Sinking 500µA                                                                                                  |                                                                | 0.1<br>0.2                                                                 | 10<br>0.4                              | μA<br>V                                    |

| THERMAL SHUTDOWN<br>Junction Temperature<br>Shutdown<br>Reset from Shutdown                                                                                                                                                                                                                                                        |                                                                                   |                                                                                                                                                       |                                                                | 150<br>130                                                                 |                                        | °C<br>℃                                    |

| GROUND PIN CURRENT<br>Ground Pin Current<br>ENABLE Pin LOW                                                                                                                                                                                                                                                                         | I <sub>GND</sub>                                                                  | I <sub>OUT</sub> = 10mA<br>I <sub>OUT</sub> = 500mA<br>V <sub>ENABLE</sub> ≤ 0.5V                                                                     |                                                                | 0.5<br>1<br>0.5                                                            | 0.7<br>1.3                             | mA<br>mA<br>μA                             |

| $\label{eq:intermediate} \begin{array}{l} \mbox{INPUT VOLTAGE} \\ \mbox{Operating Input Voltage Range}^{(7)} \\ \mbox{Specified Input Voltage Range} \\ \mbox{T}_J = -40^\circ \mbox{C to } +85^\circ \mbox{C} \end{array}$                                                                                                        | V <sub>IN</sub>                                                                   | V <sub>IN</sub> > 2.7∨<br>V <sub>IN</sub> > 2.9∨                                                                                                      | 2.1<br>V <sub>OUT</sub> + 0.7<br>V <sub>OUT</sub> + <b>0.9</b> |                                                                            | 15<br>15<br><b>15</b>                  | V<br>V<br>V                                |

| TEMPERATURE RANGE<br>Specified Range<br>Operating Range<br>Storage Range                                                                                                                                                                                                                                                           | TJ                                                                                |                                                                                                                                                       | 40<br>55<br>65                                                 |                                                                            | +85<br>+125<br>+150                    | °C<br>℃<br>℃                               |

| Thermal Resistance<br>DDPAK-5 Surface-Mount<br>SO-8 Surface-Mount<br>SOT223-5 Surface-Mount                                                                                                                                                                                                                                        | $egin{array}{c} 	heta_{ m JC} \ 	heta_{ m JA} \ 	heta_{ m JC} \end{array}$        | Junction-to-Case<br>Junction-to-Ambient<br>Junction-to-Case                                                                                           |                                                                | 4<br>150<br>15                                                             |                                        | °C/W<br>°C/W<br>°C/W                       |

NOTES: (1) The REG103 does not require a minimum output capacitor for stability. However, transient response can be improved with proper capacitor selection.

(2) Dropout voltage is defined as the input voltage minus the output voltage that produces a 2% change in the output voltage from the value at V<sub>IN</sub> = V<sub>OUT</sub> + 1V at fixed load

(3) Not applicable for  $V_{OUT}$  less than 2.7V.

(4) Current limit is the output current that produces a 10% change in output voltage from V<sub>IN</sub> = V<sub>OUT</sub> + 1V and I<sub>OUT</sub> = 10mA.

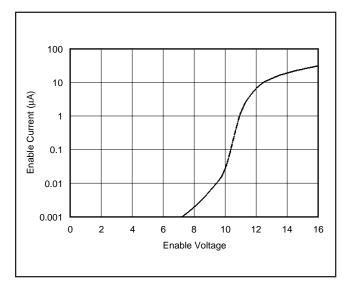

(5) For  $V_{IN} > 6.5V$ , see typical characteristic  $V_{ENABLE}$  vs  $I_{ENABLE}$ .

(6) Logic low indicates out-of-regulation condition by approximately 10%, or thermal shutdown.

(7) The REG103 no longer regulates when  $V_{IN} < V_{OUT} + V_{DROP (MAX)}$ . In drop-out or when the input voltage is between 2.7V and 2.1V, the impedance from  $V_{IN}$  to  $V_{OUT}$  is typically less than 1 $\Omega$  at  $T_J = +25^{\circ}$ C. See typical characteristic.

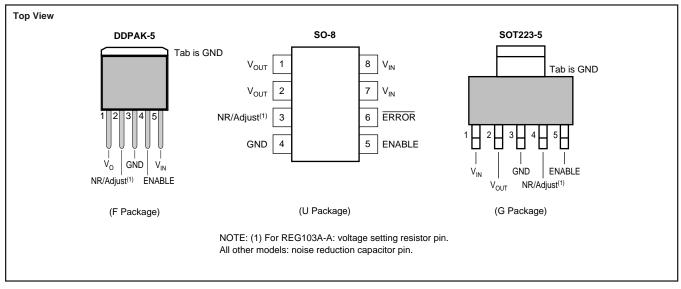

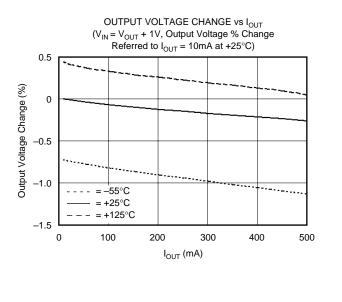

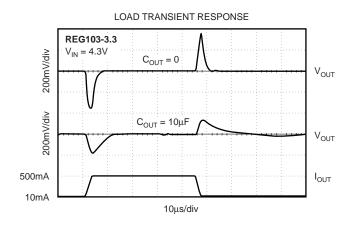

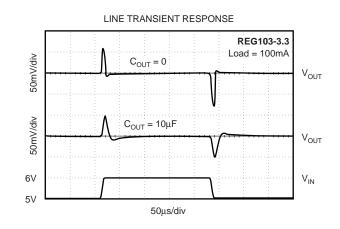

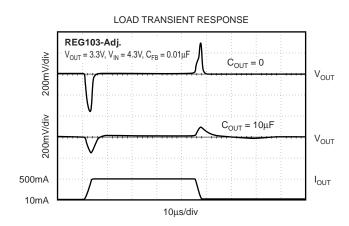

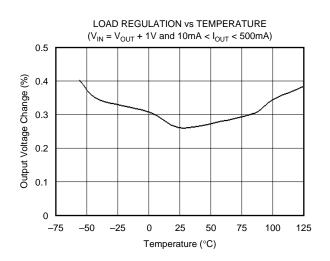

# **TYPICAL CHARACTERISTICS**

For all models, at T\_J = +25°C and V\_{ENABLE} = 2V, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont.)**

For all models, at T<sub>J</sub> = +25°C and V<sub>ENABLE</sub> = 2V, unless otherwise noted.

LINE TRANSIENT RESPONSE REG103-Adj.  $V_{OUT} = 3.3V, C_{FB} = 0.01 \mu F, I_{OUT} = 100 m A$   $C_{OUT} = 0$   $V_{OUT}$   $V_{OUT}$   $C_{OUT} = 10 \mu F$   $V_{OUT}$   $V_{OUT}$ V

# **TYPICAL CHARACTERISTICS (Cont.)**

For all models, at  $T_J$  = +25°C and  $V_{\text{ENABLE}}$  = 2V, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont.)**

For all models, at T<sub>J</sub> = +25°C and V<sub>ENABLE</sub> = 2V, unless otherwise noted.

# **BASIC OPERATION**

The REG103 series is a family of LDO (Low Drop-Out) linear regulators. The family includes five fixed output versions (2.5V to 5.0V) and an adjustable output version. An internal DMOS power device provides low dropout regulation with near constant ground pin current (largely independent of load and drop-out conditions) and very fast line and load transient response. All versions include internal current limit and thermal shutdown circuitry.

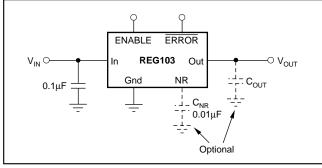

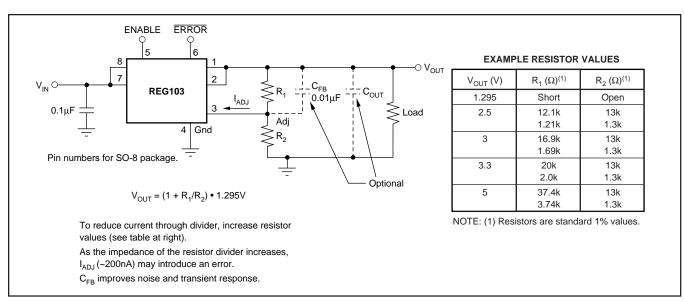

Figure 1 shows the basic circuit connections for the fixed voltage models. Figure 2 gives the connections for the adjustable output version (REG103A) and example resistor values for some commonly used output voltages. Values for other voltages can be calculated from the equation shown in Figure 2. The SO-8 package provides two pins each for  $V_{\rm IN}$  and  $V_{\rm OUT}$ . Both sets of pins **MUST** be used and connected adjacent to the device.

FIGURE 1. Fixed Voltage Nominal Circuit for REG103.

None of the versions require an output capacitor for regulator stability. The REG103 will accept any output capacitor type less than 1 $\mu$ F. For capacitance values larger than 1 $\mu$ F, the effective ESR should be greater than 0.1 $\Omega$ . This minimum ESR value includes parasitics such as printed circuit board traces, solder joints, and sockets. A minimum 0.1 $\mu$ F low ESR capacitor connected to the input supply voltage is recommended.

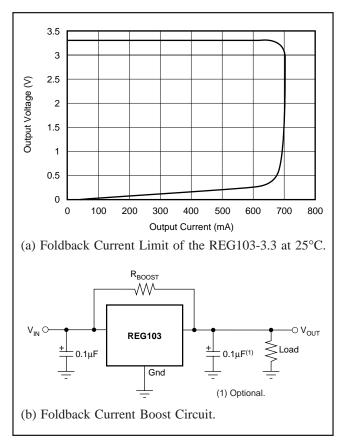

### INTERNAL CURRENT LIMIT

The REG103 internal current limit has a typical value of 700mA. A fold-back feature limits the short-circuit current to a typical short-circuit value of 40mA. This circuit will protect the regulator from damage under all load conditions. A typical characteristic of  $V_{OUT}$  versus  $I_{OUT}$  is given in Figure 3a.

Care should be taken in high current applications to avoid ground currents flowing in the circuit board traces causing voltage drops between points on the circuit. If voltage drops occur on the circuit board ground that causes the load ground voltage to be much lower than the ground voltage seen by the ground pin on the REG103, the foldback current may approach zero and the REG103 may not start up. In these types of applications, a large value resistor can be placed between  $V_{IN}$  and  $V_{OUT}$  to help "boost" up the output of the REG103 during start-up, see Figure 3b. The value for the "boost" resistor is less than the minimum load current:  $R_{BOOST} > (V_{IN} - V_{OUT})/I_{LOAD}$ . Typically, a good value for a "boost" resistor is 5k $\Omega$ .

FIGURE 2. Adjustable Voltage Circuit for REG103A.

FIGURE 3. Foldback Current Limit and Boost Circuit.

#### ENABLE

The ENABLE pin allows the regulator to be turned on and off. This pin is active HIGH and compatible with standard TTL-CMOS levels. Inputs below 0.5V (max) turn the regulator off and all circuitry is disabled. Under this condition, ground pin current drops to approximately 0.5 $\mu$ A. When not used, the ENABLE pin may be connected to V<sub>IN</sub>.

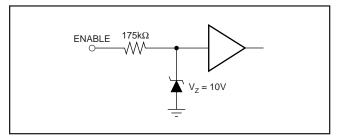

Internal to the part, the ENABLE pin is connected to an input resistor-zener diode circuit, as shown in Figure 4, creating a nonlinear input impedance. The ENABLE Pin Current versus Applied Voltage relationship is shown in Figure 5. When the ENABLE pin is connected to a voltage greater than 10V, a series resistor may be used to limit the current.

FIGURE 4. ENABLE Pin Equivalent Input Circuit.

FIGURE 5. ENABLE Pin Current versus Applied Voltage.

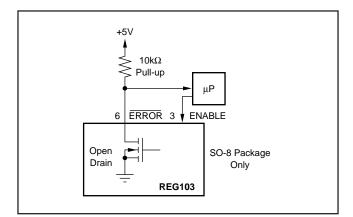

#### **ERROR FLAG**

The error indication pin, only available on the SO-8 package version, provides a fault indication out-of-regulation condition. During a fault condition,  $\overline{\text{ERROR}}$  is pulled LOW by an open drain output device. The pin voltage, in the fault state, is typically less than 0.2V at 500µA.

A fault condition is indicated when the output voltage differs (either above or below) from the specified value by approximately 10%. Figure 6 shows a typical fault-monitoring application.

FIGURE 6. ERROR Pin Typical Fault-Monitoring Circuit.

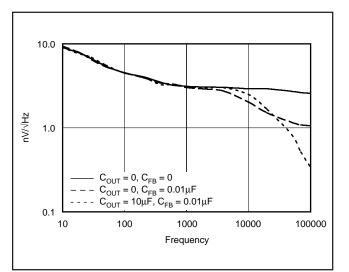

#### **OUTPUT NOISE**

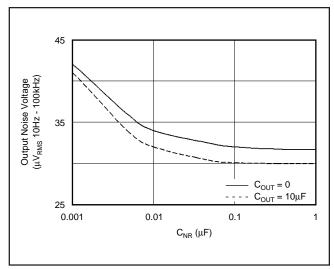

A precision band-gap reference is used for the internal reference voltage,  $V_{REF}$ , for the REG103. This reference is the dominant noise source within the REG103. It generates approximately 45µVrms in the 10Hz to 100kHz bandwidth at the reference output. The regulator control loop gains up the reference noise, so that the noise voltage of the regulator is approximately given by:

$$V_{\rm N} = 45 \mu V rms \frac{R_1 + R_2}{R2} = 45 \mu V rms \bullet \frac{V_{\rm OUT}}{V_{\rm REF}}$$

Since the value of  $V_{REF}$  is 1.295V, this relationship reduces to:

$$V_{\rm N} = 35 \ \frac{\mu V rms}{V} \bullet V_{\rm OUT}$$

Connecting a capacitor,  $C_{NR}$ , from the Noise-Reduction (NR) pin to ground, can reduce the output noise voltage. Adding  $C_{NR}$ , as shown in Figure 7, forms a low-pass filter for the voltage reference. For  $C_{NR} = 10$ nF, the total noise in the 10Hz to 100kHz bandwidth is reduced by approximately a factor of 3.5, as shown in Figure 8.

FIGURE 8. Output Noise versus Noise-Reduction Capacitor.

The REG103 adjustable version does not have the noisereduction pin available, however, the adjust pin is the summing junction of the error amplifier. A capacitor,  $C_{FB}$ , connected from the output to the adjust pin will reduce both the output noise and the peak error from a load transient. Figure 9 shows improved output noise performance for two capacitor combinations.

FIGURE 9. Output Noise Density on Adjustable Versions.

The REG103 utilizes an internal charge pump to develop an internal supply voltage sufficient to drive the gate of the DMOS pass element above  $V_{IN}$ . The charge-pump switching noise (nominal switching frequency = 2MHz) is not measurable at the output of the regulator.

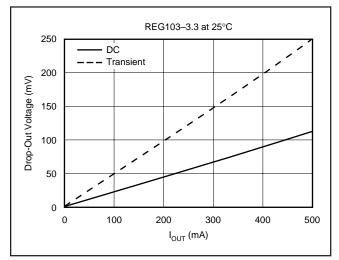

#### DROP-OUT VOLTAGE

The REG103 uses an N-channel DMOS as the "pass" element. When the input voltage is within a few hundred millivolts of the output voltage, the DMOS device behaves like a resistor. Therefore, for low values of  $V_{IN}$  to  $V_{OUT}$ , the regulator's input-to-output resistance is the Rds<sub>ON</sub> of the DMOS pass element (typically 230m $\Omega$ ). For static (DC) loads, the REG103 will typically maintain regulation down to  $V_{IN}$  to  $V_{OUT}$  voltage drop of 115mV at full-rated output current. In Figure 10, the bottom line (DC dropout) shows the minimum  $V_{IN}$  to  $V_{OUT}$  voltage drop required to prevent drop-out under DC load conditions.

FIGURE 7. Block Diagram.

For large step changes in load current, the REG103 requires a larger voltage drop across it to avoid degraded transient response. The boundary of this "transient drop-out" region is shown as the top line in Figure 10. Values of  $V_{\rm IN}$  to  $V_{\rm OUT}$  voltage drop above this line insure normal transient response.

FIGURE 10. Transient and DC Dropout.

In the transient dropout region between "DC" and "Transient", transient response recovery time increases. The time required to recover from a load transient is a function of both the magnitude and rate of the step change in load current and the available "headroom"  $V_{\rm IN}$  to  $V_{\rm OUT}$  voltage drop. Under worst-case conditions (full-scale load change with  $V_{\rm IN}$  to  $V_{\rm OUT}$  voltage drop close to DC dropout levels), the REG103 can take several hundred microseconds to re-enter the specified window of regulation.

#### TRANSIENT RESPONSE

The REG103 response to transient line and load conditions improves at lower output voltages. The addition of a capacitor (nominal value 10nF) from the output pin to ground may improve the transient response. In the adjustable version, the addition of a capacitor,  $C_{FB}$  (nominal value 10nF), from the output to the adjust pin will also improve the transient response.

#### THERMAL PROTECTION

Power dissipated within the REG103 will cause the junction temperature to rise. The REG103 has thermal shutdown circuitry that protects the regulator from damage. The thermal protection circuitry disables the output when the junction temperature reaches approximately 150°C, allowing the device to cool. When the junction temperature cools to approximately 130°C, the output circuitry is again enabled. Depending on various conditions, the thermal protection circuit may cycle on and off. This limits the dissipation of the regulator, but may have an undesirable effect on the load.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heat sink. For reliable operation, junction temperature should be limited to 125°C, maximum. To estimate the margin of safety in a complete design (including heat sink), increase the ambient temperature until the thermal protection is triggered. Use worst-case loads and signal conditions. For good reliability, thermal protection should trigger more than 35°C above the maximum expected ambient condition of your application. This produces a worst-case junction temperature of 125°C at the highest expected ambient temperature and worst-case load.

The internal protection circuitry of the REG103 has been designed to protect against overload conditions. It was not intended to replace proper heat sinking. Continuously running the REG103 into thermal shutdown will degrade reliability.

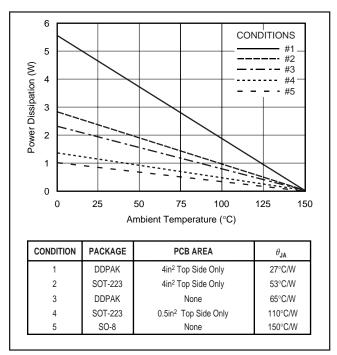

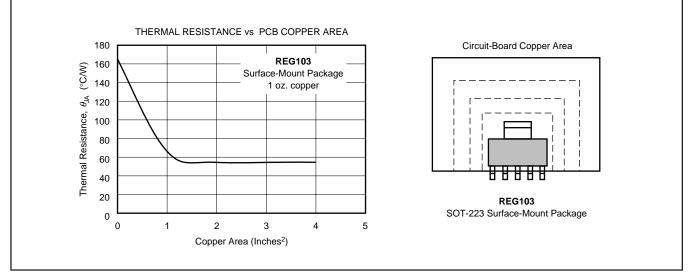

#### POWER DISSIPATION

The REG103 is available in three different package configurations. The ability to remove heat from the die is different for each package type and, therefore, presents different considerations in the printed circuit board (PCB) layout. The PCB area around the device that is free of other components moves the heat from the device to the ambient air. While it is difficult to impossible to quantify all of the variables in a thermal design of this type, performance data for several configurations are shown in Figure 11. In all cases, the PCB copper area is bare copper, free of solder-resist mask, and not solder plated. All examples are for 1-ounce copper. Using heavier copper will increase the effectiveness in moving the heat from the device. In those examples where there is copper on both sides of the PCB, no connection has been provided between the two sides. The addition of plated through holes will improve the heat sink effectiveness.

FIGURE 11. Maximum Power Dissipation versus Ambient Temperature for the Various Packages and PCB Heat Sink Configurations.

Power dissipation depends on input voltage and load conditions. Power dissipation is equal to the product of the average output current times the voltage across the output element,  $V_{\rm IN}$  to  $V_{\rm OUT}$  voltage drop.

$$P_{D} = (V_{IN} - V_{OUT}) \bullet I_{OUT(AVG)}$$

Power dissipation can be minimized by using the lowest possible input voltage necessary to assure the required output voltage.

#### **REGULATOR MOUNTING**

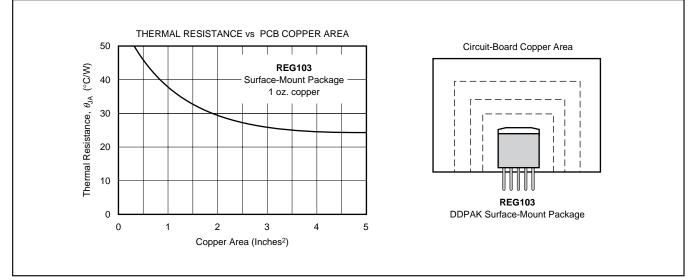

The tab of both packages is electrically connected to ground. For best thermal performance, the tab of the DDPAK surface-mount version should be soldered directly to a circuitboard copper area. Increasing the copper area improves heat dissipation. Figure 12 shows typical thermal resistance from junction to ambient as a function of the copper area for the DDPAK.

Although the tabs of the DDPAK and the SOT-223 are electrically grounded, they are not intended to carry any current. The copper pad that acts as a heat sink should be isolated from the rest of the circuit to prevent current flow through the device from the tab to the ground pin. Solder pad footprint recommendations for the various REG103 devices are presented in the Application Bulletin "Solder Pad Recommendations for Surface-Mount Devices" (SBFA015), available from the Texas Instruments web site (www.ti.com).

FIGURE 12. Thermal Resistance versus PCB Area for the Five-Lead DDPAK.

FIGURE 13. Thermal Resistance versus PCB Area for the Five-Lead SOT-223.

### PACKAGING INFORMATION

| Orderable Device   | Status<br>(1) | Package Type     | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|--------------------|---------------|------------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| REG103FA-2.5KTTT   | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 50             | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-2.5        | Samples |

| REG103FA-2.5KTTTG3 | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 50             | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-2.5        | Samples |

| REG103FA-3.3KTTT   | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 50             | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-3.3        | Samples |

| REG103FA-5KTTT     | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 50             | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-5          | Samples |

| REG103FA-5KTTTG3   | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 50             | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-5          | Samples |

| REG103FA-A/500     | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 500            | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-A          | Samples |

| REG103FA-AKTTT     | ACTIVE        | DDPAK/<br>TO-263 | КТТ                | 5    | 50             | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103FA-A          | Samples |

| REG103GA-2.5       | ACTIVE        | SOT-223          | DCQ                | 6    | 78             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103G25                 | Samples |

| REG103GA-3.3       | ACTIVE        | SOT-223          | DCQ                | 6    | 78             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103G33                 | Samples |

| REG103GA-3.3/2K5   | ACTIVE        | SOT-223          | DCQ                | 6    | 2500           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103G33                 | Samples |

| REG103GA-5         | ACTIVE        | SOT-223          | DCQ                | 6    | 78             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103G50                 | Samples |

| REG103GA-5/2K5     | ACTIVE        | SOT-223          | DCQ                | 6    | 2500           | RoHS & Green    | SN                                   | Level-2-260C-1 YEAR  | -40 to 85    | R103G50                 | Samples |

| REG103GA-5G4       | ACTIVE        | SOT-223          | DCQ                | 6    | 78             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103G50                 | Samples |

| REG103GA-A         | ACTIVE        | SOT-223          | DCQ                | 6    | 78             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103GA                  | Samples |

| REG103GA-A/2K5     | ACTIVE        | SOT-223          | DCQ                | 6    | 2500           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103GA                  | Samples |

| REG103GA-AG4       | ACTIVE        | SOT-223          | DCQ                | 6    | 78             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | R103GA                  | Samples |

| REG103UA-2.5       | ACTIVE        | SOIC             | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U25           | Samples |

| REG103UA-2.5/2K5   | ACTIVE        | SOIC             | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U25           | Samples |

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| REG103UA-3.3     | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103UA4           | Samples |

| REG103UA-3.3/2K5 | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103UA4           | Samples |

| REG103UA-5       | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U50           | Samples |

| REG103UA-5/2K5   | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U50           | Samples |

| REG103UA-A       | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U-A           | Samples |

| REG103UA-A/2K5   | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U-A           | Samples |

| REG103UA-AG4     | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 85    | REG<br>103U-A           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

www.ti.com

## PACKAGE OPTION ADDENDUM

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

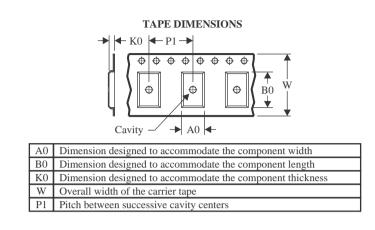

#### TAPE AND REEL INFORMATION

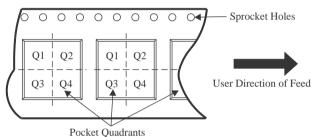

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| REG103GA-3.3/2K5            | SOT-223         | DCQ                | 6 | 2500 | 330.0                    | 12.4                     | 7.1        | 7.45       | 1.88       | 8.0        | 12.0      | Q3               |

| REG103GA-5/2K5              | SOT-223         | DCQ                | 6 | 2500 | 330.0                    | 12.4                     | 6.85       | 7.3        | 1.88       | 8.0        | 12.0      | Q3               |

| REG103GA-A/2K5              | SOT-223         | DCQ                | 6 | 2500 | 330.0                    | 12.4                     | 7.1        | 7.45       | 1.88       | 8.0        | 12.0      | Q3               |

| REG103UA-2.5/2K5            | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| REG103UA-3.3/2K5            | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| REG103UA-5/2K5              | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| REG103UA-A/2K5              | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com

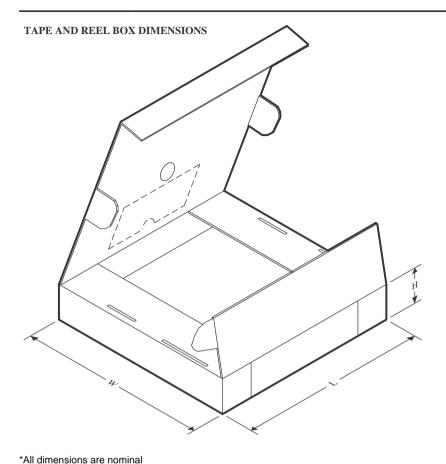

## PACKAGE MATERIALS INFORMATION

30-Dec-2022

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| REG103GA-3.3/2K5 | SOT-223      | DCQ             | 6    | 2500 | 346.0       | 346.0      | 29.0        |

| REG103GA-5/2K5   | SOT-223      | DCQ             | 6    | 2500 | 356.0       | 356.0      | 35.0        |

| REG103GA-A/2K5   | SOT-223      | DCQ             | 6    | 2500 | 346.0       | 346.0      | 29.0        |

| REG103UA-2.5/2K5 | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| REG103UA-3.3/2K5 | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| REG103UA-5/2K5   | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| REG103UA-A/2K5   | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

### TEXAS INSTRUMENTS

www.ti.com

30-Dec-2022

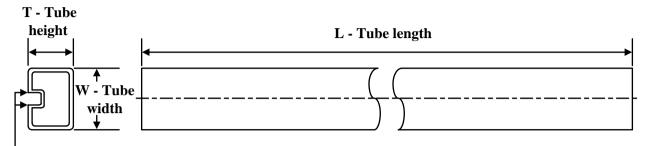

### TUBE

### - B - Alignment groove width

| *All dimensions are nominal |  |

|-----------------------------|--|

|                             |  |

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| REG103GA-2.5 | DCQ          | SOT-223      | 6    | 78  | 532.13 | 8.63   | 3.6    | 3.68   |

| REG103GA-3.3 | DCQ          | SOT-223      | 6    | 78  | 532.13 | 8.63   | 3.6    | 3.68   |

| REG103GA-5   | DCQ          | SOT-223      | 6    | 78  | 532.13 | 8.63   | 3.6    | 3.68   |

| REG103GA-5G4 | DCQ          | SOT-223      | 6    | 78  | 532.13 | 8.63   | 3.6    | 3.68   |

| REG103GA-A   | DCQ          | SOT-223      | 6    | 78  | 532.13 | 8.63   | 3.6    | 3.68   |

| REG103GA-AG4 | DCQ          | SOT-223      | 6    | 78  | 532.13 | 8.63   | 3.6    | 3.68   |

| REG103UA-2.5 | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| REG103UA-3.3 | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| REG103UA-5   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| REG103UA-A   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| REG103UA-AG4 | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

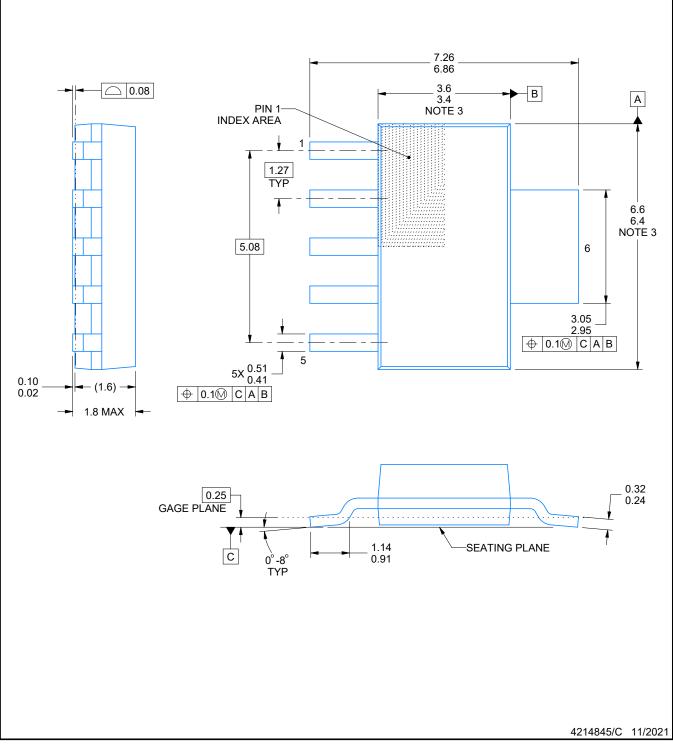

# DCQ0006A

## **PACKAGE OUTLINE**

## SOT - 1.8 mm max height

PLASTIC SMALL OUTLINE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

## **DCQ0006A**

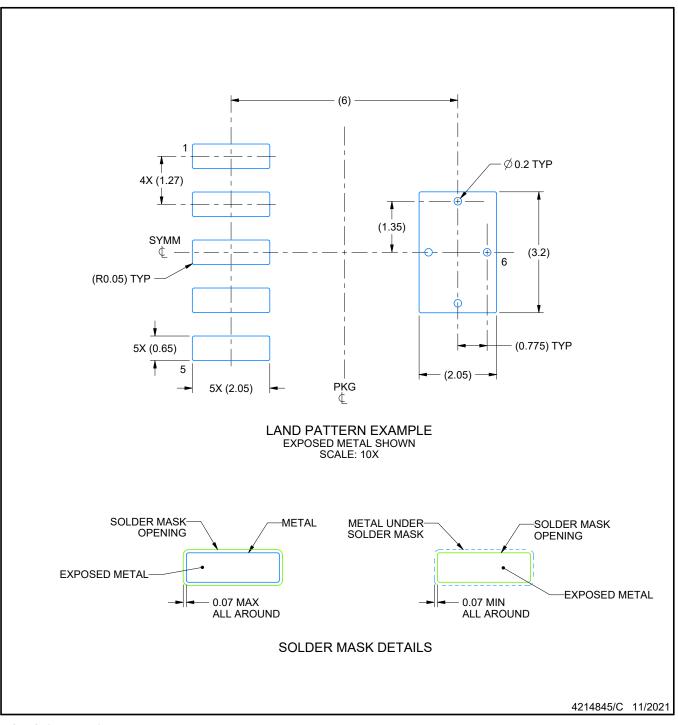

# **EXAMPLE BOARD LAYOUT**

### SOT - 1.8 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.6. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

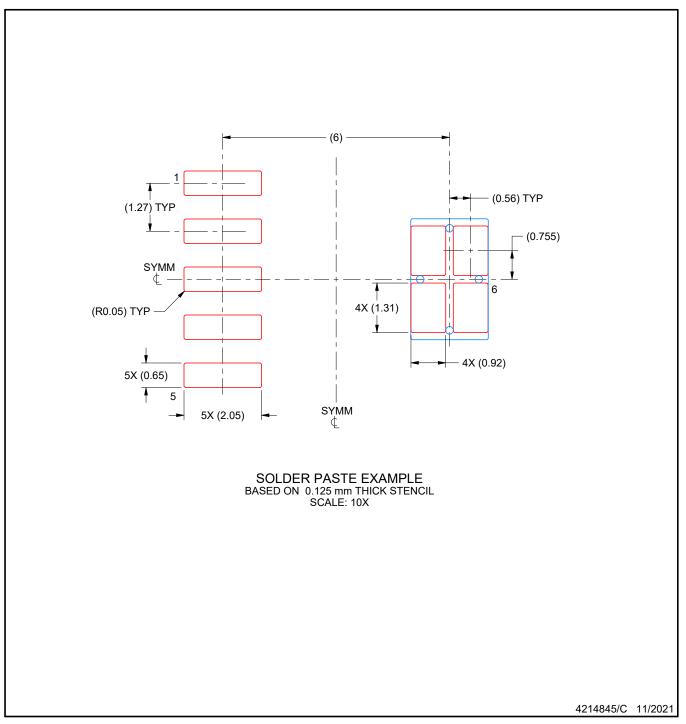

## DCQ0006A

## **EXAMPLE STENCIL DESIGN**

## SOT - 1.8 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

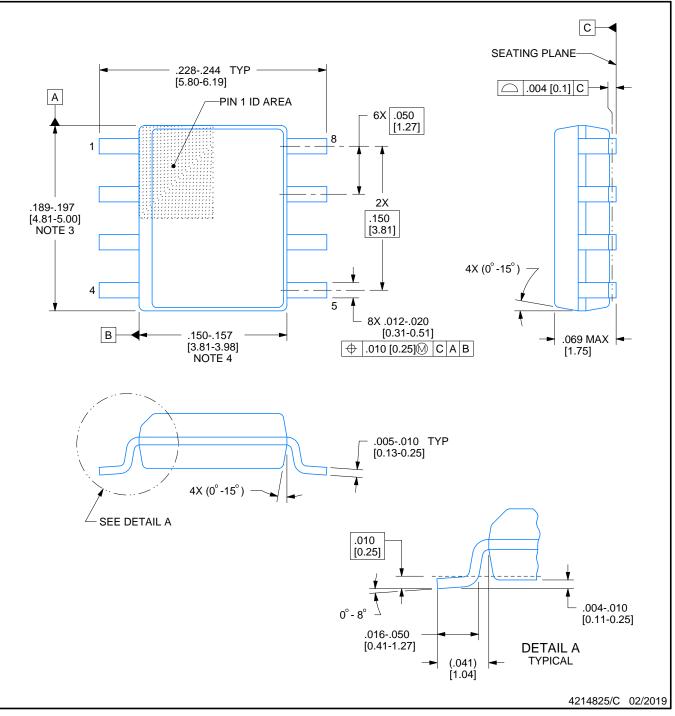

# D0008A

## **PACKAGE OUTLINE**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

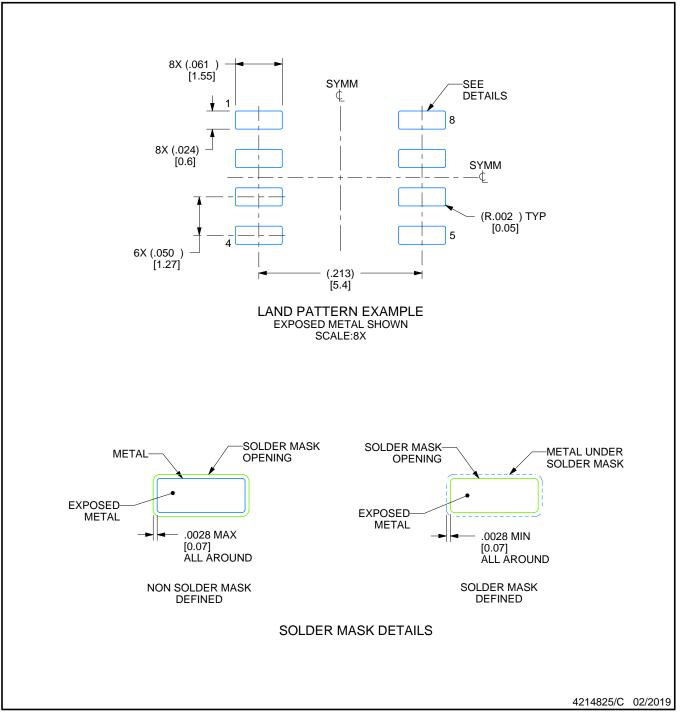

## D0008A

# **EXAMPLE BOARD LAYOUT**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

## D0008A

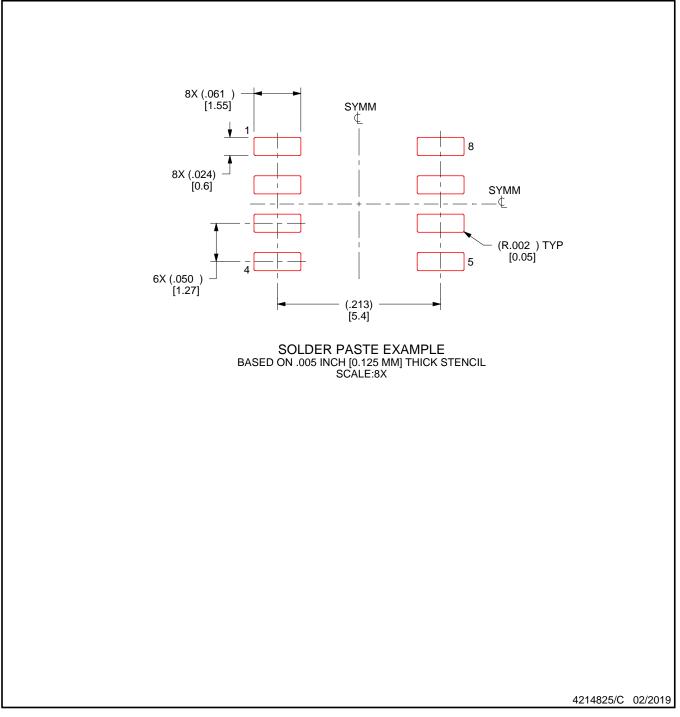

# **EXAMPLE STENCIL DESIGN**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

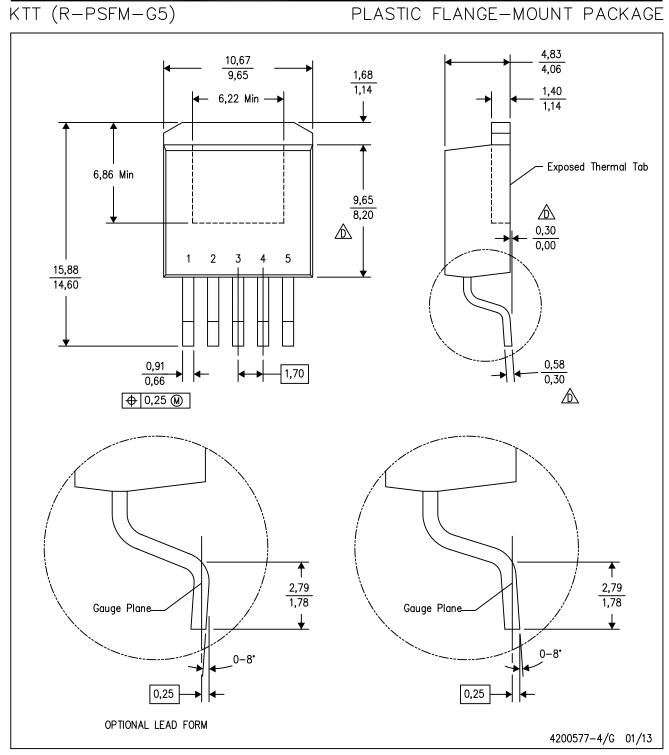

## **MECHANICAL DATA**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash or protrusion not to exceed 0.005 (0,13) per side.

- A Falls within JEDEC TO—263 variation BA, except minimum lead thickness, maximum seating height, and minimum body length.

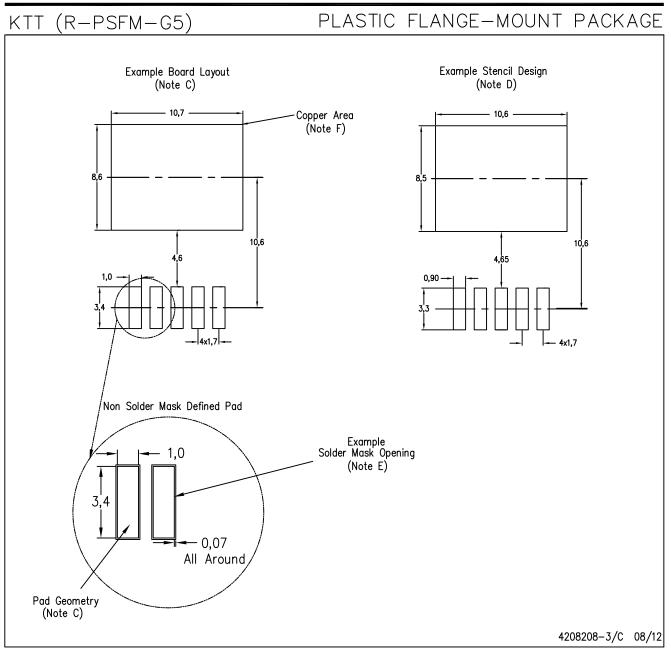

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- F. This package is designed to be soldered to a thermal pad on the board. Refer to the Product Datasheet for specific thermal information, via requirements, and recommended thermal pad size. For thermal pad sizes larger than shown a solder mask defined pad is recommended in order to maintain the solderable pad geometry while increasing copper area.

TEXAS INSTRUMENTS www.ti.com

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated