# 具有 6 位全局亮度控制的 16 通道, 16 位, 脉宽调制 (PWM) 发光二级管 (LED) 驱动器

查询样品: TLC59482

## 特性

- 16 个恒定流入电流源输出通道

- 具有最大亮度控制 (BC) 数据的灌电流能力:

- 1mA 至 35mA (V<sub>cc</sub>≤ 3.6V)

- 1mA 至 45mA (V<sub>CC</sub>> 3.6V)

- 全局亮度控制 (BC): •

- 范围为 0% 至 100% 的 6 位(64 步长)(缺省 值为 50%)

- LED 电源电压: 高达 10V

- VCC: 3.0V 至 5.5V

- 恒定电流精度: ٠

- 通道到通道: ±1% (典型值), ±2.5% (最大 值)

- 器件到器件: ±2%(典型值), ±4%(最大值)

- 数据传输速率: 30MHz

- 灰度控制时钟: 33MHz

- 自动重复显示功能

- 自动数据刷新

- 显示计时复位

- 用来防止涌入电流的 4 通道成组延迟开关 •

- 工作温度范围: -40°C 至 +85°C •

### 应用范围

- LED 视频显示屏

- LED 信号板

### 说明

TLC59482 是一款 16 通道,恒定灌电流驱动器。 每个 通道有一个步长为 65.536 的独立可调节、脉宽调制 (PWM) 灰度 (GS) 亮度控制。 所有通道具有一个 64 步长的全局亮度控制 (BC)。 BC 调节与其它 LED 驱动 器的亮度偏差。可通过一个串行接口访问 GS,和 BC 数据。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com.cn

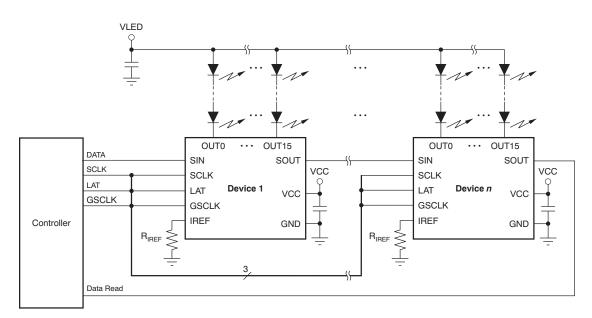

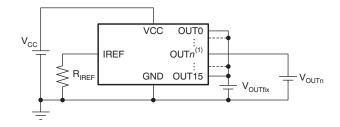

### 典型应用电路(多菊花链 TLC59482)

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ORDERING INFORMATION**<sup>(1)</sup>

| PRODUCT   | PACKAGE<br>DESIGNATOR     | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |  |  |  |

|-----------|---------------------------|--------------------|------------------------------|--|--|--|

|           | DRO                       | TLC59482DBQR       | Tape and Reel, 2500          |  |  |  |

| TI 050482 | DBQ<br>RGE <sup>(2)</sup> | TLC59482DBQ        | Tube, 50                     |  |  |  |

| TLC59482  |                           | TLC59482RGER       | Tape and Reel, 3000          |  |  |  |

|           |                           | TLC59482RGET       | Tape and Reel, 250           |  |  |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

(2) Product preview device.

### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

Over operating free-air temperature range, unless otherwise noted.

|                               |                                          | VALU | JE                    |      |

|-------------------------------|------------------------------------------|------|-----------------------|------|

|                               |                                          | MIN  | MAX                   | UNIT |

|                               | VCC                                      | -0.3 | +6                    | V    |

| Valtara (2)                   | SIN, SCLK, LAT, GSCLK, IREF              | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Voltage <sup>(2)</sup>        | SOUT                                     | -0.3 | V <sub>CC</sub> + 0.3 | V    |

|                               | OUT0 to OUT15                            | -0.3 | +11                   | V    |

| Current                       | I <sub>OUT</sub> (dc), OUT0 to OUT15     |      | +55                   | mA   |

| Tomporatura                   | Operating junction, T <sub>J</sub> (max) |      | +150                  | °C   |

| Temperature                   | Storage, T <sub>stg</sub>                | -55  | +150                  | °C   |

| Electrostatic discharge (ESD) | Human body model (HBM)                   |      | 3000                  | V    |

| ratings                       | Charged device model (CDM)               |      | 2000                  | V    |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to device ground terminal.

### THERMAL INFORMATION

|                    |                                              | TLC59               | 482          |       |

|--------------------|----------------------------------------------|---------------------|--------------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                | DBQ<br>(SSOP, QSOP) | RGE<br>(QFN) | UNITS |

|                    |                                              | 24 PINS             | 24 PINS      |       |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance       | 86.7                | 35.5         |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 50.4                | 44           |       |

| $\theta_{JB}$      | Junction-to-board thermal resistance         | 10.0                | 14.7         | 80.44 |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter   | 13.0                | 0.4          | °C/W  |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter | 39.7                | 14.8         |       |

| $\theta_{JCbot}$   | Junction-to-case (bottom) thermal resistance | N/A                 | 2.9          |       |

(1) 有关传统和新的热度量的更多信息,请参阅/C 封装热度量应用报告, SPRA953。

#### ZHCSAM5-DECEMBER 2012

# **RECOMMENDED OPERATING CONDITIONS**

At  $T_{A} = -40^{\circ}$ C to +85°C, unless otherwise noted.

|                          | PARAMETER                                   | TEST CONDITIONS                                           | MIN                 | NOM MAX             | UNIT |

|--------------------------|---------------------------------------------|-----------------------------------------------------------|---------------------|---------------------|------|

| DC CHARAC                | CTERISTICS (V <sub>CC</sub> = 3 V to 5.5 V) |                                                           |                     |                     |      |

| V <sub>CC</sub>          | Supply voltage                              |                                                           | 3.0                 | 5.5                 | V    |

| Vo                       | Voltage applied to output                   | OUT0 to OUT15                                             |                     | 10                  | V    |

| V <sub>IH</sub>          | High-level input voltage                    | SIN, SCLK, LAT, GSCLK                                     | $0.7 \times V_{CC}$ | V <sub>CC</sub>     | V    |

| V <sub>IL</sub>          | Low-level input voltage                     | SIN, SCLK, LAT, GSCLK                                     | GND                 | $0.3 \times V_{CC}$ | V    |

| I <sub>OH</sub>          | High-level output current                   | SOUT                                                      |                     | -2                  | mA   |

| I <sub>OL</sub>          | Low-level output current                    | SOUT                                                      |                     | 2                   | mA   |

|                          |                                             | OUT0 to OUT15,<br>3 V $\leq$ V <sub>CC</sub> $\leq$ 3.6 V |                     | 35                  | mA   |

| I <sub>OLC</sub>         | Constant output sink current                | OUT0 to OUT15,<br>3.6 V < V <sub>CC</sub> ≤ 5.5 V         |                     | 45                  | mA   |

| T <sub>A</sub>           | Operating free-air temperature range        |                                                           | -40                 | +85                 | °C   |

| TJ                       | Operating junction temperature range        |                                                           | -40                 | +125                | °C   |

| AC CHARAC                | CTERISTICS (V <sub>CC</sub> = 3 V to 5.5 V) |                                                           |                     |                     |      |

| V <sub>CC</sub>          | Supply voltage                              |                                                           | 3.0                 | 5.5                 | V    |

| 4                        | Data shift alask fraguenav                  | SCLK, 3.0 V $\leq$ VCC $\leq$ 3.6 V                       |                     | 25                  | MHz  |

| fclk (SCLK)              | Data shift clock frequency                  | SCLK, 3.6 V < VCC ≤ 5.5 V                                 |                     | 30                  | MHz  |

| f <sub>CLK</sub> (GSCLK) | Grayscale control clock frequency           | GSCLK                                                     |                     | 33                  | MHz  |

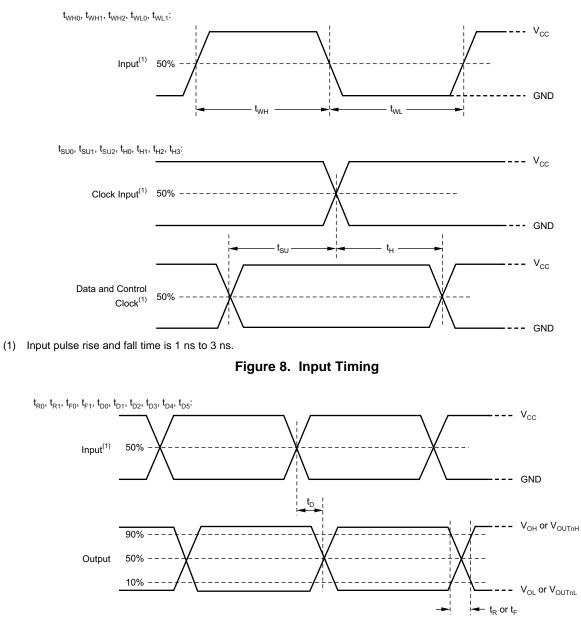

| t <sub>WH0</sub>         |                                             | SCLK                                                      | 10                  |                     | ns   |

| t <sub>WL0</sub>         |                                             | SCLK                                                      | 10                  |                     | ns   |

| t <sub>WH1</sub>         | Pulse duration                              | GSCLK                                                     | 10                  |                     | ns   |

| t <sub>WL1</sub>         |                                             | GSCLK                                                     | 10                  |                     | ns   |

| t <sub>WH2</sub>         |                                             | LAT                                                       | 10                  |                     | ns   |

| t <sub>SU0</sub>         |                                             | SIN to SCLK↑                                              | 4                   |                     | ns   |

| t <sub>SU1</sub>         | Setup time                                  | LAT↑ to SCLK↑                                             | 2                   |                     | ns   |

| t <sub>SU2</sub>         |                                             | LAT↓ to SCLK↑ <sup>(1)</sup>                              | 5                   |                     | ns   |

| t <sub>H0</sub>          |                                             | SCLK↑ to SIN                                              | 4                   |                     | ns   |

| t <sub>H1</sub>          | Hold time                                   | SCLK↑ to LAT↑                                             | 7                   |                     | ns   |

| t <sub>H2</sub>          | Hold time                                   | SCLK↑ to LAT↓                                             | 14                  |                     | ns   |

| t <sub>H3</sub>          |                                             | LAT↓ to GSCLK↑                                            | 30                  |                     | ns   |

(1) Refer to the  $t_{D1}$  parameter in the Switching Characteristics table for the FC data read time.

**TLC59482**

Texas INSTRUMENTS

ZHCSAM5-DECEMBER 2012

www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS**

| PARAMETER          |                                                                                 | TEST CONDI                                                                                                                                                                                                            | TEST CONDITIONS                                                                                                                                                                             |                | TYP   | MAX      | UNIT |

|--------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|----------|------|

| V <sub>OH</sub>    | High-level output voltage (SOUT)                                                | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                                              |                                                                                                                                                                                             | $V_{CC} - 0.4$ |       | $V_{CC}$ | V    |

| V <sub>OL</sub>    | Low-level output voltage (SOUT)                                                 | I <sub>OL</sub> = 2 mA                                                                                                                                                                                                | I <sub>OL</sub> = 2 mA                                                                                                                                                                      |                |       | 0.4      | V    |

| VIREF              | Reference voltage output                                                        | $R_{IREF} = 1.5 \text{ k}\Omega$                                                                                                                                                                                      | 1.175                                                                                                                                                                                       | 1.200          | 1.225 | V        |      |

| I <sub>IN</sub>    | Input current<br>(SIN, SCLK, GSCLK)                                             | $V_{IN} = V_{CC}$ or GND                                                                                                                                                                                              |                                                                                                                                                                                             | -1             |       | 1        | μΑ   |

| I <sub>CC0</sub>   |                                                                                 | SIN, SCLK, LAT, GSCLK = GND,<br>BC = 3Fh, $V_{OUTn}$ = 0.8 V, $R_{IREF}$ =                                                                                                                                            |                                                                                                                                                                                             |                | 1.5   | 3        | mA   |

| I <sub>CC1</sub>   | _                                                                               | $ \begin{array}{l} \text{SIN, SCLK, LAT, GSCLK = GND,} \\ \text{BC} = 3\text{Fh}, \text{V}_{\text{OUTn}} = 0.8 \text{ V},  \text{R}_{\text{IREF}} = \\ (\text{I}_{\text{OUTn}} = 15.9\text{-mA target}) \end{array} $ |                                                                                                                                                                                             |                | 3     | 5        | mA   |

| I <sub>CC2</sub>   | Supply current (V <sub>CC</sub> )                                               |                                                                                                                                                                                                                       | SIN, SCLK, LAT = GND, GSCLK = 33 MHz,<br>GSn = FFFFh, BC = 3Fh, $V_{OUTn} = 0.8$ V, $R_{IREF} = 3$ k $\Omega$                                                                               |                |       | 10       | mA   |

| I <sub>CC3</sub>   |                                                                                 |                                                                                                                                                                                                                       | SIN, SCLK, LAT = GND, GSCLK = 33 MHz,<br>GS $n$ = FFFFh, BC = 3Fh, V <sub>OUTn</sub> = 0.8 V, R <sub>IREF</sub> = 1.5 kΩ<br>(I <sub>OUT</sub> = 31.8-mA target)                             |                |       | 13.5     | mA   |

| I <sub>OLC</sub>   | Constant output sink current<br>(OUT0 to OUT15)                                 |                                                                                                                                                                                                                       | All OUT <i>n</i> = on, BC = 3Fh, V <sub>OUTn</sub> = V <sub>OUTfix</sub> = 0.8 V,<br>$R_{IREF} = 1.5 \text{ k}\Omega$ , $T_A = +25^{\circ}\text{C}$ ( $I_{OLCn} = 31.8 \text{-mA target}$ ) |                |       | 33.8     | mA   |

| I <sub>OLKG0</sub> |                                                                                 | All $OUTn = off, GSn = 0000h,$                                                                                                                                                                                        | T <sub>J</sub> = +25°C                                                                                                                                                                      |                |       | 0.1      | μA   |

| I <sub>OLKG1</sub> | Output leakage current<br>(OUT0 to OUT15)                                       | $V_{OUTn} = V_{OUTfix} = 10 V,$<br>$R_{IRFF} = 1.5 k\Omega$                                                                                                                                                           | $T_J = +85^{\circ}C^{(1)}$                                                                                                                                                                  |                |       | 0.2      | μA   |

| I <sub>OLKG2</sub> |                                                                                 | $(I_{OLCn} = 31.8 \text{-mA target})$                                                                                                                                                                                 | $T_J = +125^{\circ}C^{(1)}$                                                                                                                                                                 |                | 0.3   | 0.8      | μA   |

| ∆I <sub>OLC0</sub> | Constant-current error,<br>channel-to-channel<br>(OUT0 to OUT15) <sup>(2)</sup> | All OUT $n$ = on, BC = 3Fh, V <sub>OUTn</sub> =<br>R <sub>IREF</sub> = 1.5 kΩ, T <sub>A</sub> = +25°C<br>(I <sub>OUTn</sub> = 31.8-mA target)                                                                         | V <sub>OUTfix</sub> = 0.8 V,                                                                                                                                                                |                | ±1%   | ±2.5%    |      |

| ∆I <sub>OLC1</sub> | Constant-current error,<br>device-to-device<br>(OUT0 to OUT15) <sup>(3)</sup>   | All OUT $n$ = on, BC = 3Fh, V <sub>OUTn</sub> =<br>R <sub>IREF</sub> = 1.5 kΩ, T <sub>A</sub> = +25°C<br>(I <sub>OUTn</sub> = 31.8-mA target)                                                                         |                                                                                                                                                                                             |                |       | ±4%      |      |

| ∆I <sub>OLC2</sub> | Line regulation<br>(OUT0 to OUT15) <sup>(4)</sup>                               | $\label{eq:V_CC} \begin{array}{l} V_{CC} = 3.0 \text{ V to } 5.5 \text{ V, all } OUTn = c\\ V_{OUTn} = V_{OUTfix} = 0.8 \text{ V, } R_{IREF} = 1.\\ (I_{OUTn} = 31.8\text{-mA target}) \end{array}$                   |                                                                                                                                                                                             | ±1             | ±3    | %/V      |      |

| ∆I <sub>OLC3</sub> | Load regulation<br>(OUT0 to OUT15) <sup>(5)</sup>                               | All OUT $n$ = on, BC = 3Fh, V <sub>OUTn</sub> =<br>V <sub>OUTfix</sub> = 0.8 V, R <sub>IREF</sub> = 1.5 kΩ<br>(I <sub>OUTn</sub> = 31.8-mA target)                                                                    | 0.8 V to 3.0 V,                                                                                                                                                                             |                | ±1    | ±3       | %/V  |

| R <sub>PDWN</sub>  | Pull-down resistor                                                              | LAT                                                                                                                                                                                                                   |                                                                                                                                                                                             | 250            | 500   | 750      | kΩ   |

(1) Not tested; specified by design.

(2) The deviation of each output from the average of OUT0 to OUT15 constant-current. Deviation is calculated by the formula:

l

(3) current value. Deviation is calculated by the formula:

$$\begin{split} & \text{where } \mathbf{h} = 0 \text{ to } 15. \\ & \text{The deviation of the OUT} n \text{ output current value from the ideal constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-constant-c$$

where n = 0 to 15.

(4)

(5)

ZHCSAM5-DECEMBER 2012

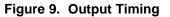

### SWITCHING CHARACTERISTICS

At  $T_A = -40^{\circ}$ C to +85°C,  $V_{CC} = 3$  V to 5.5 V,  $C_L = 15$  pF,  $R_L = 110 \Omega$ ,  $R_{IREF} = 1.5 k\Omega$ , and  $V_{LED} = 5.0$  V, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C and  $V_{CC} = 3.3$  V.

|                     | PARAMETER                           | TEST CONDITIONS                                                                                                 | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>R0</sub>     | Diag time                           | SOUT                                                                                                            |     | 1.5 | 5   | ns   |

| t <sub>R1</sub>     | Rise time                           | $OUTn$ , BC = 7Fh, $T_A = +25^{\circ}C$                                                                         |     | 30  |     | ns   |

| t <sub>F0</sub>     |                                     | SOUT                                                                                                            |     | 1.5 | 5   | ns   |

| t <sub>F1</sub>     | Fall time                           | $OUTn$ , BC = 7Fh, $T_A = +25^{\circ}C$                                                                         |     | 30  |     | ns   |

| t <sub>D0</sub>     |                                     | SCLK↑ to SOUT↑↓                                                                                                 |     | 23  | 35  | ns   |

| t <sub>D1</sub>     |                                     | LAT↓ to SOUT↑↓                                                                                                  |     | 27  | 42  | ns   |

| t <sub>D2</sub>     |                                     | GSCLK <sup>↑</sup> to OUT0, OUT7, OUT8, OUT15 on/off with BC = 7Fh, $T_A = +25$ °C                              |     | 50  |     | ns   |

| t <sub>D3</sub>     | Propagation delay                   | GSCLK↑ to OUT1, OUT6, OUT9, OUT14 on/off with BC = 7Fh, $T_A = +25$ °C                                          |     | 55  |     | ns   |

| t <sub>D4</sub>     |                                     | GSCLK↑ to OUT2, OUT5, OUT10, OUT13 on/off with BC = 7Fh, $T_A = +25$ °C                                         |     | 60  |     | ns   |

| t <sub>D5</sub>     |                                     | GSCLK↑ to OUT3, OUT4, OUT11, OUT12 on/off with BC = 7Fh, $T_A = +25$ °C                                         |     | 65  |     | ns   |

| t <sub>ON_ERR</sub> | Output on-time error <sup>(1)</sup> | $t_{OUTON} - t_{GSCLK}$ , $GSn = 0001h$ , $GSCLK = 20$ MHz,<br>BC = 3Fh, $V_{CC} = 3.3$ V, $T_A = +25^{\circ}C$ | -35 |     | 10  | ns   |

(1) Output on-time error ( $t_{ON\_ERR}$ ) is calculated by the formula:  $t_{ON\_ERR} = t_{OUT\_ON} - t_{GSCLK}$ .  $t_{OUT\_ON}$  is the actual on-time of the constantcurrent driver.  $t_{GSCLK}$  is the GSCLK period.

ZHCSAM5-DECEMBER 2012

### PARAMETER MEASUREMENT INFORMATION

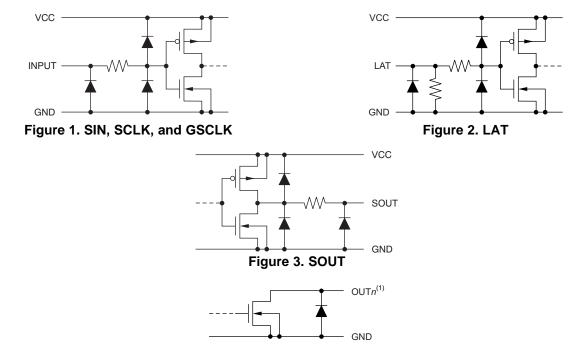

## PIN-EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

(1) n = 0 to 15.

Figure 4. OUT0 Through OUT15

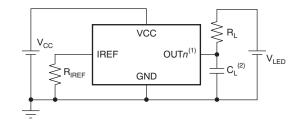

### **TEST CIRCUITS**

(1) n = 0 to 15.

(2)  $C_L$  includes measurement probe and jig capacitance.

### Figure 5. Rise Time and Fall Time Test Circuit for OUTn

(1)  $C_L$  includes measurement probe and jig capacitance.

### Figure 6. Rise Time and Fall Time Test Circuit for SOUT

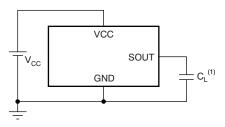

(1) n = 0 to 15.

Figure 7. Constant-Current Test Circuit for OUTn

www.ti.com.cn

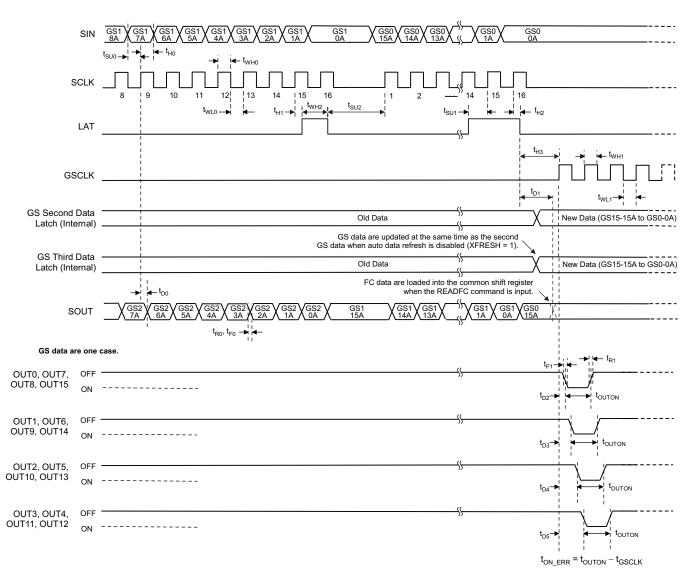

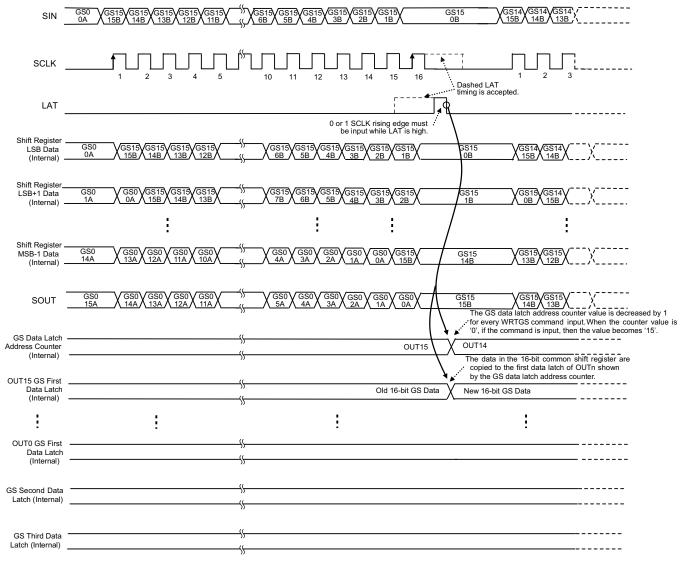

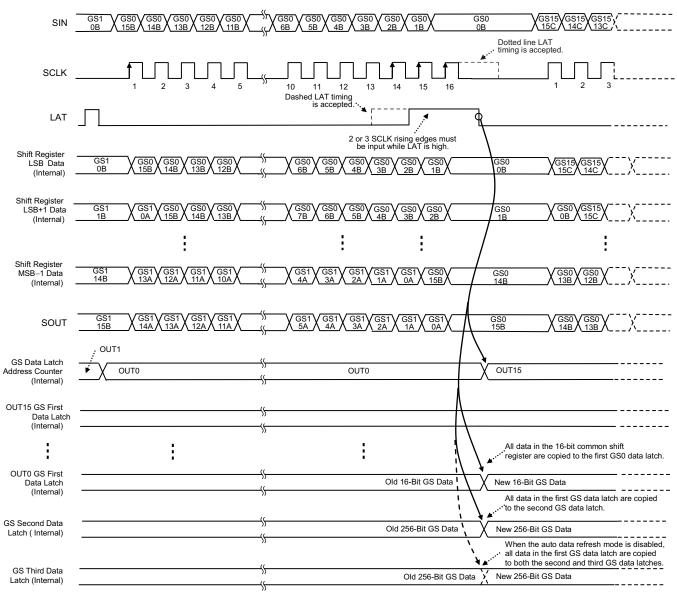

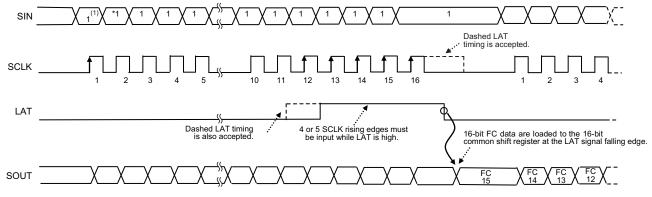

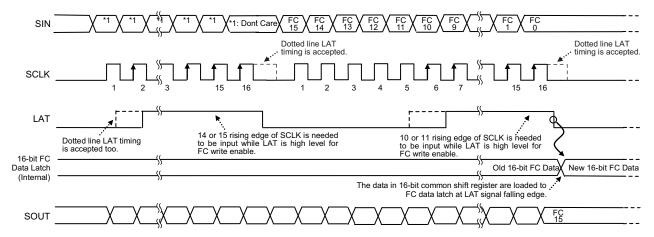

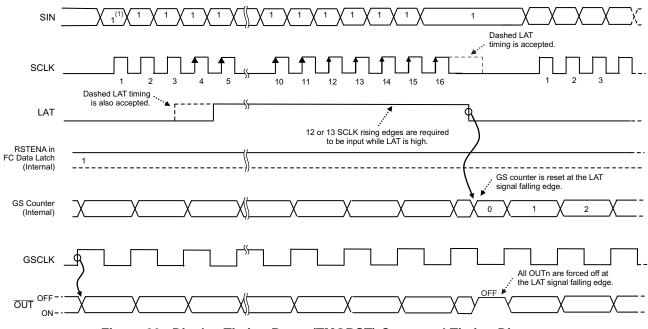

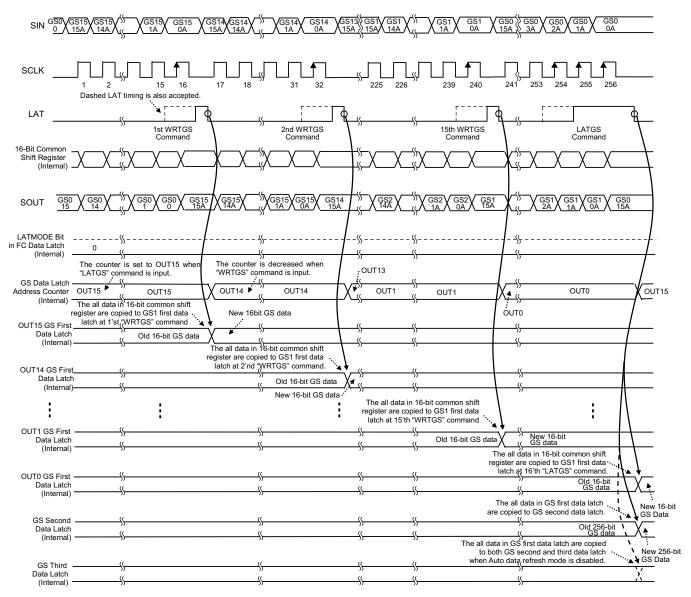

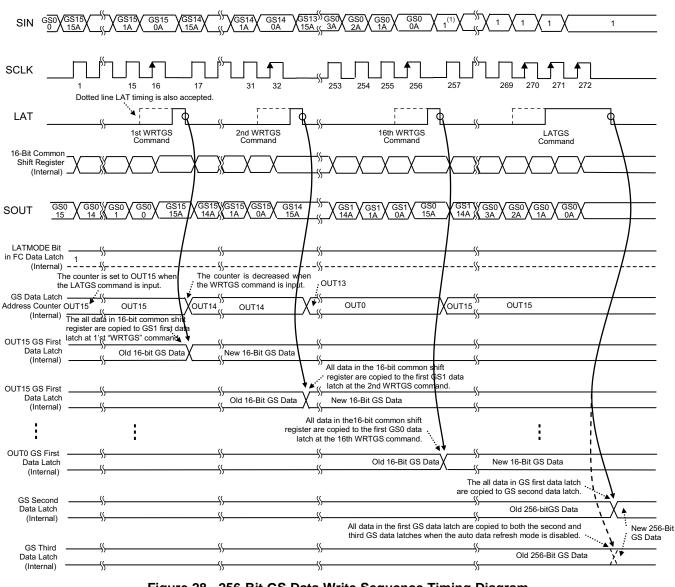

### **TIMING DIAGRAMS**

(1) Input pulse rise and fall time is 1 ns to 3 ns.

# TLC59482

TEXAS INSTRUMENTS

#### ZHCSAM5-DECEMBER 2012

www.ti.com.cn

(1) NV = Not valid; these data are not used for any function.

### Figure 10. Timing Diagram

ZHCSAM5-DECEMBER 2012

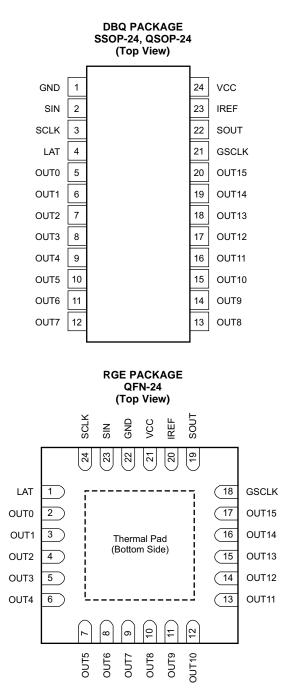

### **PIN CONFIGURATIONS**

NOTE: The thermal pad is not internally connected to GND. The thermal pad must be connected to GND via the printed board circuit (PCB) pattern.

### TEXAS INSTRUMENTS

#### ZHCSAM5-DECEMBER 2012

www.ti.com.cn

|       |     |     |     | PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PIN |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | NC  | ).  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NAME  | DBQ | RGE | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND   | 1   | 22  | —   | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GSCLK | 21  | 18  | 1   | Grayscale (GS) pulse width modulation (PWM) reference clock control for OUT <i>n</i> .<br>Each GSCLK rising edge increments the GS counter for PWM control.<br>When the TMGRST command is input with the TMRSTEN bit (equal to '1') in the function<br>control data latch, all constant-current outputs (OUT0 to OUT15) are forced off and the GS<br>counter is reset to '0'. Furthermore, all constant-current outputs are forced off and the GS<br>counter is reset to '0' when the LATGS command is input with the XRFRESH bit (equal to '1')<br>in the function control data latch. |

| IREF  | 23  | 20  | I/O | Reference current terminal.<br>A resistor connected between IREF to GND sets the maximum current for all constant-current<br>outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LAT   | 4   | 1   | I   | The LAT falling edge latches the data from the 16-bit common shift register into the first GS data latch for the OUT <i>n</i> that are selected by either the GS data address down counter, global brightness control (BC) data latch, or function control (FC) data latch. The data latch is selected by the number of input SCLK rising edges while LAT is high. This pin is internally pulled down to GND with a 500-k $\Omega$ (typ) resistor.                                                                                                                                      |

| OUT0  | 5   | 2   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT1  | 6   | 3   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT2  | 7   | 4   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT3  | 8   | 5   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT4  | 9   | 6   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT5  | 10  | 7   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT6  | 11  | 8   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT7  | 12  | 9   | 0   | Constant-current outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUT8  | 13  | 10  | 0   | Multiple outputs can be configured in parallel to increase the constant-current capability.<br>Different voltages can be applied to each output.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT9  | 14  | 11  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT10 | 15  | 12  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT11 | 16  | 13  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT12 | 17  | 14  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT13 | 18  | 15  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT14 | 19  | 16  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT15 | 20  | 17  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCLK  | 3   | 24  | I   | Serial data shift clock.<br>Data present on SIN are shifted to the LSB of the 16-bit common shift register with the SCLK<br>rising edge. Data in the shift register are shifted towards the MSB at each SCLK rising edge.<br>The MSB of the common shift register appears on SOUT.                                                                                                                                                                                                                                                                                                      |

| SIN   | 2   | 23  | Ι   | Serial data input for the 16-bit common shift register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SOUT  | 22  | 19  | ο   | Serial data output of the 16-bit common shift register.<br>SOUT is connected to the 16-bit common shift register MSB. Data are clocked out at the<br>SCLK rising edge. Data in the function data latch can be read from SOUT during the READFC<br>command.                                                                                                                                                                                                                                                                                                                              |

| VCC   | 24  | 21  | —   | Power-supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

ZHCSAM5-DECEMBER 2012

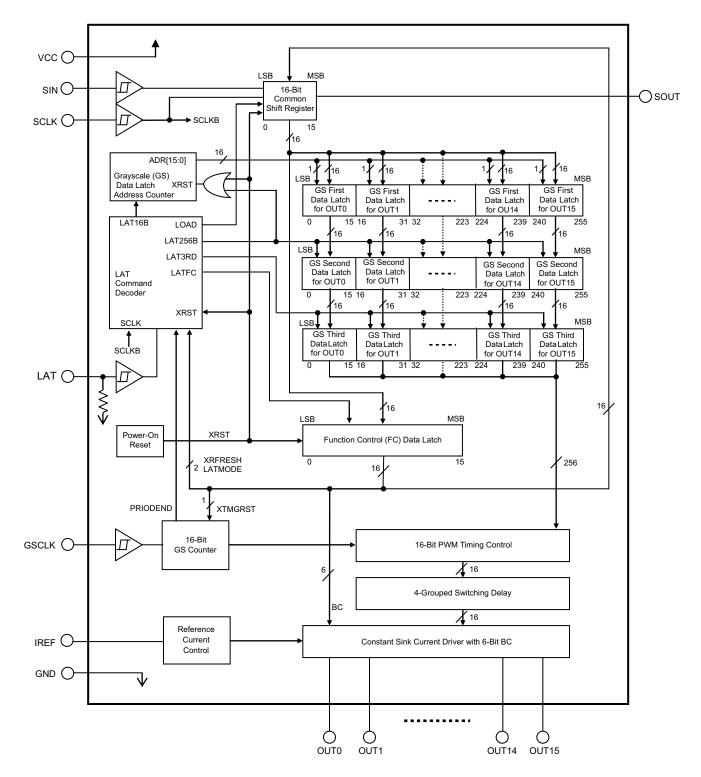

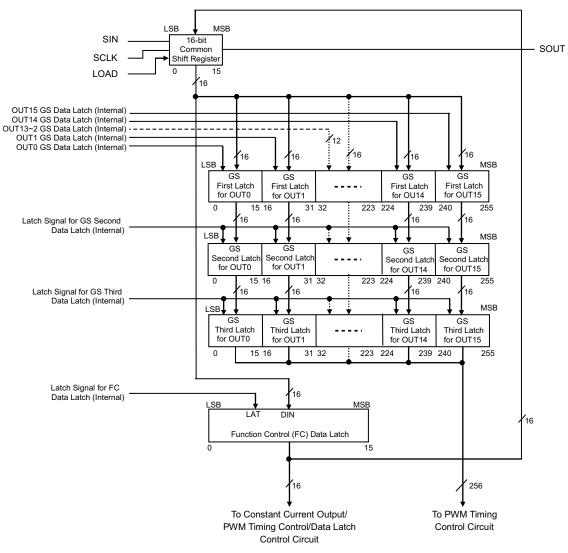

## FUNCTIONAL BLOCK DIAGRAM

#### ZHCSAM5-DECEMBER 2012

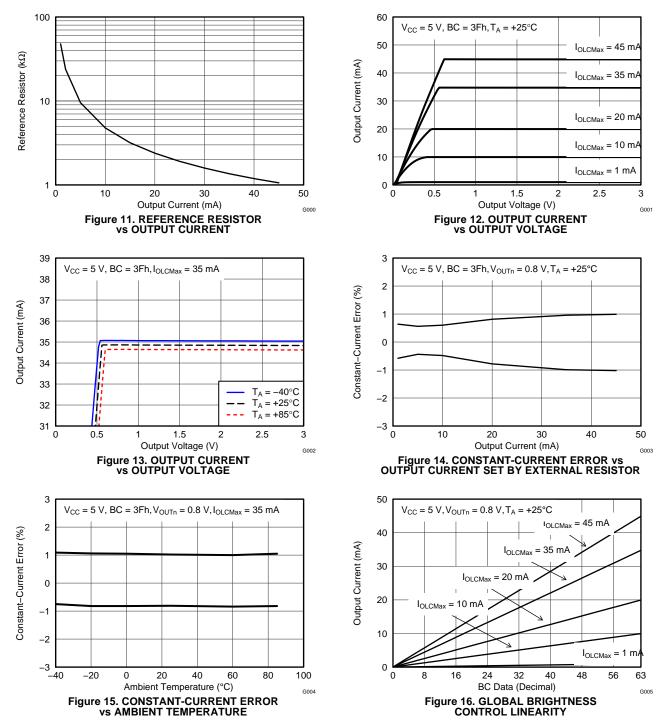

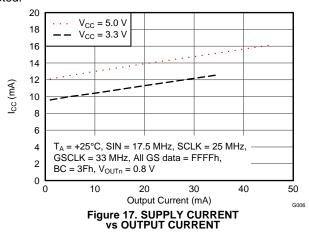

### **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ , unless otherwise noted.

www.ti.com.cn

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}$ C, unless otherwise noted.

www.ti.com.cn

### DETAILED DESCRIPTION

### MAXIMUM CONSTANT SINK CURRENT VALUE

The maximum output current value of each channel ( $I_{OLCMax}$ ) is programmed by a single resistor ( $R_{IREF}$ ) that is placed between the IREF and GND pins. The current value can be calculated by Equation 1:

$$\mathsf{R}_{\mathsf{IREF}}\left(\mathsf{k}\Omega\right) = \frac{\mathsf{V}_{\mathsf{IREF}}\left(\mathsf{V}\right)}{\mathsf{I}_{\mathsf{OLCMax}}\left(\mathsf{m}\mathsf{A}\right)} \times 39.8$$

Where:

$V_{IREF}$  = the internal reference voltage on IREF (typically 1.20 V when the global BC data are at maximum)  $I_{OLCMax}$  = 1 mA to 35 mA (3 V ≤ VCC ≤ 3.6 V) or 1 mA to 45 mA (3.6 V < VCC ≤ 5.5 V) at OUT*n* and BC = 63 (1)

$I_{OLCMax}$  is the highest current for each output. Each output sinks  $I_{OLCMax}$  current when it is turned on and the global brightness control (BC) data are set to the maximum value of 3Fh (64). Each output sink current can be reduced by lowering the BC value.

$R_{IREF}$  must be between 1.06 k $\Omega$  and 47.8 k $\Omega$  in order to hold  $I_{OLCMax}$  between 45 mA (typ) and 1 mA (typ). Otherwise, the output may be unstable. Output currents lower than 1 mA can be achieved by setting  $I_{OLCMax}$  to 1 mA or higher and then using global BC to lower the output current.

Table 1 shows the characteristics of the constant-current sink versus the external resistor, R<sub>IREF</sub>.

### Table 1. Maximum Constant-Current Output versus External Resistor Value

| I <sub>OLCMax</sub> (mA)          | I <sub>OLC</sub> FOLLOWING POWER-UP (mA, BC = 32) | R <sub>IREF</sub> (kΩ, typ) |

|-----------------------------------|---------------------------------------------------|-----------------------------|

| 45 (V <sub>CC</sub> > 3.6 V only) | 22.5                                              | 1.06                        |

| 40 (V <sub>CC</sub> > 3.6 V only) | 20                                                | 1.19                        |

| 35                                | 17.5                                              | 1.37                        |

| 30                                | 15                                                | 1.59                        |

| 25                                | 12.5                                              | 1.91                        |

| 20                                | 10                                                | 2.39                        |

| 15                                | 7.5                                               | 3.18                        |

| 10                                | 5                                                 | 4.78                        |

| 5                                 | 2.5                                               | 9.55                        |

| 1                                 | 0.5                                               | 47.8                        |

### **GLOBAL BRIGHTNESS CONTROL (BC) FUNCTION**

The TLC59482 can simultaneously adjust the output current of all constant-current outputs. This function is called *global brightness control* (BC). The global BC for all outputs (OUT0 to OUT15) is programmed with a 6-bit word. The global BC adjusts all output currents in 64 steps from 0% to 100%, where 100% corresponds to the maximum output current set by  $R_{IREF}$ . Equation 2 calculates the actual output current as a function of  $R_{IREF}$  and global BC value. BC data can be set via the serial interface. When the device is powered on, the BC data in the function control (FC) data latch is set to 32 as the initial value.

The output current value controlled by BC can be calculated by Equation 2.

$$I_{OUTn}$$

(mA) =  $I_{OLCMax}$  (mA)  $\times \frac{BCn}{63}$

Where:

I<sub>OLCMax</sub> = the maximum constant-current value for each output determined by R<sub>IREF</sub>

BC = the global brightness control value in the brightness control data latch (0 to 63)

(2)

Table 2 summarizes the BC data versus the set current value.

|                   | BC DATA RATIO OF OUTPUT |              |                                       |                                       |                                                            |

|-------------------|-------------------------|--------------|---------------------------------------|---------------------------------------|------------------------------------------------------------|

| BINARY            | DECIMAL                 | HEX          | CURRENT TO<br>I <sub>OLCMax</sub> (%) | (I <sub>OLCMax</sub> = 45 mA,<br>typ) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 1 mA, typ) |

| 00 0000           | 0                       | 00           | 0                                     | 0                                     | 0                                                          |

| 00 0001           | 1                       | 01           | 1.6                                   | 0.71                                  | 0.02                                                       |

| 00 0010           | 2                       | 02           | 3.2                                   | 1.43                                  | 0.03                                                       |

| —                 | —                       | —            | —                                     | —                                     | —                                                          |

| 01 1111           | 31                      | 1F           | 49.2                                  | 22.14                                 | 0.49                                                       |

| 10 0000 (default) | 32 (default)            | 20 (default) | 50.8                                  | 22.86                                 | 0.51                                                       |

| 10 0001           | 33                      | 21           | 52.4                                  | 23.57                                 | 0.52                                                       |

| —                 | —                       | —            | —                                     | —                                     | —                                                          |

| 11 1101           | 61                      | 3D           | 96.8                                  | 43.57                                 | 0.97                                                       |

| 11 1110           | 62                      | 3E           | 98.4                                  | 44.29                                 | 0.98                                                       |

| 11 1111           | 63                      | 3F           | 100.0                                 | 45.00                                 | 1.00                                                       |

| Table 2. BC Data versus Constant-Current Ratio and Set Curre | nt Value |

|--------------------------------------------------------------|----------|

|--------------------------------------------------------------|----------|

### **GRAYSCALE (GS) FUNCTION (PWM CONTROL)**

The TLC59482 can adjust the brightness of each output channel using a pulse width modulation (PWM) control scheme. The architecture of 16 bits per channel results in 65,536 brightness steps, from 0% up to 100% brightness.

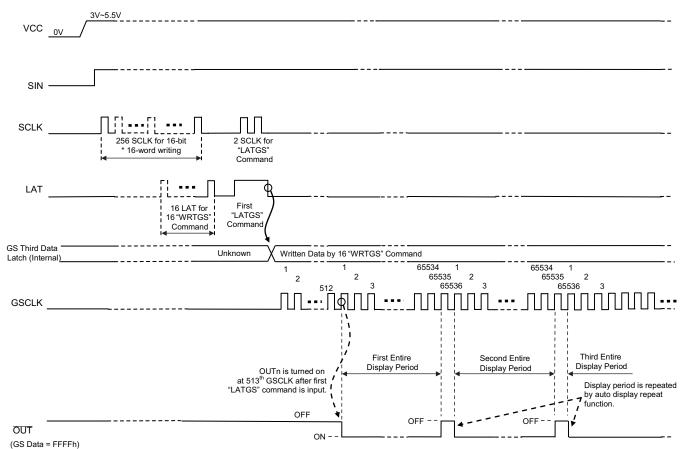

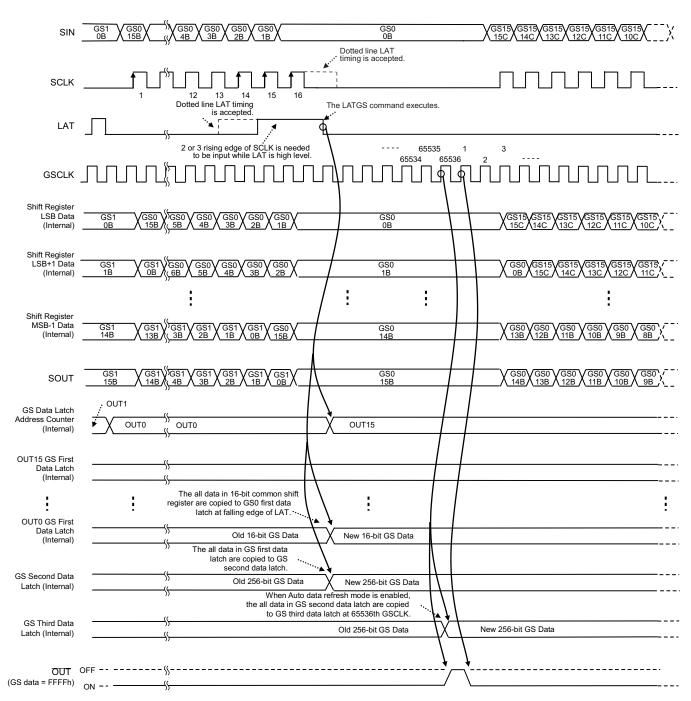

The PWM operation is controlled by the grayscale (GS) counter based on the GS data in the third GS data latch. The GS counter increments on each rising edge of the grayscale reference clock (GSCLK). When the TMGRST command is input with the TMRSTEN bit (equal to '1') of the function control data latch, or when the LATGS command is input with the XRFRESH bit (equal to '1') of the function control data latch, all constant-current outputs (OUT0 to OUT15) are forced off, the GS counter is reset to '0', and the GS PWM timing controller is initialized.

The on-time (t<sub>OUT ON</sub>) of each output (OUT*n*) can be calculated by Equation 3.

$t_{OUT_ON}$  (ns) =  $t_{GSCLK} \times GSn$

where:

$t_{GSCLK}$  is on GS clock period GS*n* is the programmed GS value for OUT*n* (0 to 65535)

(3)

www.ti.com.cn

Table 3 summarizes the GS data values versus the output on-time duty cycle in a 16-bit length PWM. When the device powers up, all outputs are forced off and do not turn on until the 256-bit GS data are written to the third data latch even if GSCLK is input.

| GS DATA |      | ON-TIME RATE vs | GS D    | ATA  | ON-TIME RATE vs |

|---------|------|-----------------|---------|------|-----------------|

| DECIMAL | HEX  | MAX GS (%)      | DECIMAL | HEX  | MAX GS (%)      |

| 0       | 0    | 0               | 32768   | 8000 | 50.001          |

| 1       | 1    | 0.002           | 32769   | 8001 | 50.002          |

| 2       | 2    | 0.003           | 32770   | 8002 | 50.004          |

| 3       | 3    | 0.005           | 32771   | 8003 | 50.005          |

| _       | _    | _               | _       | _    | —               |

| 8191    | 1FFF | 12.499          | 40959   | 9FFF | 62.499          |

| 8192    | 2000 | 12.500          | 40960   | A000 | 62.501          |

| 8193    | 2001 | 12.502          | 40961   | A001 | 62.502          |

| _       | _    | _               | _       | _    | —               |

| 16383   | 3FFF | 24.999          | 49151   | BFFF | 75.000          |

| 16384   | 4000 | 25.000          | 49152   | C000 | 75.001          |

| 16385   | 4001 | 25.002          | 49153   | C001 | 75.003          |

| _       | _    | _               | _       | _    | —               |

| 24575   | 5FFF | 37.499          | 57343   | DFFF | 87.500          |

| 24576   | 6000 | 37.501          | 57344   | E000 | 87.501          |

| 24577   | 6001 | 37.502          | 57345   | E001 | 87.503          |

| _       | _    | _               | _       | _    | _               |

| 32765   | 7FFD | 49.996          | 65533   | FFFD | 99.997          |

| 32766   | 7FFE | 49.998          | 65534   | FFFE | 99.998          |

| 32767   | 7FFF | 49.999          | 65535   | FFFF | 100.000         |

### Table 3. Output Duty Cycle and On-Time versus GS Data (16-Bit PWM Bit Length)

### **Enhanced Spectrum (ES) PWM Control**

In this PWM control, the entire display period is divided into 128 display segments. The total display period is the time from the first grayscale clock (GSCLK) to the 65,536th GS clock input for the 16-bit length PWM. Each display segment has a maximum of 512 grayscale clocks (maximum). The OUT*n* on-time changes, depending on the 16-bit grayscale data. Refer to Table 4 for the sequence of information and to Figure 18 for the timing information.

TLC59482

## Table 4. ES PWM Drive Turn On-Time Length

| GS DATA     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DECIMAL HEX |       | OUT n DRIVER OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 0           | 0000h | Does not turn on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 1           | 0001h | Turns on for one GSCLK period in the first display segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 2           | 0002h | Turns on for one GSCLK period in the first and 65th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 3           | 0003h | Turns on for one GSCLK period in the first, 65th, and 33th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 4           | 0004h | Turns on for one GSCLK period in the first, 65th, 33th, and 97th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 5           | 0005h | Turns on for one GSCLK period in the first, 65th, 33th, 97th, and 17th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 6           | 0006h | Turns on for one GSCLK period in the first, 65th, 33th, 97th, 17th, and 81th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| _           | _     | The number of display segments where OUT <i>n</i> is turned on for one GSCLK is incremented by increasing the GS data in the following order:<br>1 > 65 > 33 > 97 > 17 > 81 > 49 > 113 > 9 > 73 > 41 > 105 > 25 > 89 > 57 > 121 > 5 > 69 > 37 > 101 > 21 > 85 > 53 > 117 > 13 > 77 > 45 > 109 > 29 > 93 > 61 > 125 > 3 > 67 > 35 > 99 > 19 > 83 > 51 > 115 > 11 > 75 > 43 > 107 > 27 > 91 > 59 > 123 > 7 > 71 > 39 > 103 > 23 > 87 > 55 > 119 > 15 > 79 > 47 > 111 > 31 > 95 > 63 > 127 > 2 > 66 > 34 > 98 > 18 > 82 > 50 > 114 > 10 > 74 > 42 > 106 > 26 > 90 > 58 > 122 > 6 > 70 > 38 > 102 > 22 > 86 > 54 > 118 > 14 > 78 > 46 > 110 > 30 > 94 > 62 > 126 > 4 > 68 > 36 > 100 > 20 > 84 > 52 > 116 > 12 > 76 > 44 > 108 > 28 > 92 > 60 > 124 > 8 > 72 > 40 > 104 > 24 > 88 > 56 > 120 > 16 > 80 > 48 > 112 > 32 > 96 > 64 > 128. |  |  |  |  |  |

| 127         | 007Fh | Turns on for one GSCLK period in the first to 127th display segments, but does not turn on in the 128th display segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 128         | 0080h | Turns on for one GSCLK period in all display segments (first to 128th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 129         | 0081h | Turns on for two GSCLK periods in the first display period and for one GSCLK period in all other display periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| _           | _     | The number of display segments where OUT <i>n</i> is turned on for one GSCLK is incremented by increasing the GS data in the following order:<br>1 > 65 > 33 > 97 > 17 > 81 > 49 > 113 > 9 > 73 > 41 > 105 > 25 > 89 > 57 > 121 > 5 > 69 > 37 > 101 > 21 > 85 > 53 > 117 > 13 > 77 > 45 > 109 > 29 > 93 > 61 > 125 > 3 > 67 > 35 > 99 > 19 > 83 > 51 > 115 > 11 > 75 > 43 > 107 > 27 > 91 > 59 > 123 > 7 > 71 > 39 > 103 > 23 > 87 > 55 > 119 > 15 > 79 > 47 > 111 > 31 > 95 > 63 > 127 > 2 > 66 > 34 > 98 > 18 > 82 > 50 > 114 > 10 > 74 > 42 > 106 > 26 > 90 > 58 > 122 > 6 > 70 > 38 > 102 > 22 > 86 > 54 > 118 > 14 > 78 > 46 > 110 > 30 > 94 > 62 > 126 > 4 > 68 > 36 > 100 > 20 > 84 > 52 > 116 > 12 > 76 > 44 > 108 > 28 > 92 > 60 > 124 > 8 > 72 > 40 > 104 > 24 > 88 > 56 > 120 > 16 > 80 > 48 > 112 > 32 > 96 > 64 > 128. |  |  |  |  |  |

| 255         | 00FFh | Turns on for two GSCLK periods in the first to 127th display segments and turns on one GSCLK period in the 128th display segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 256         | 0100h | Turns on for two GSCLK periods in all display segments (first to 128th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 257         | 0101h | Turns on for three GSCLK periods in the first display segments and for two GSCLK periods in all other display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|             | _     | The number of display segments where OUT <i>n</i> is turned on for one GSCLK is incremented by increasing the GS data in the following order:<br>1 > 65 > 33 > 97 > 17 > 81 > 49 > 113 > 9 > 73 > 41 > 105 > 25 > 89 > 57 > 121 > 5 > 69 > 37 > 101 > 21 > 85 > 53 > 117 > 13 > 77 > 45 > 109 > 29 > 93 > 61 > 125 > 3 > 67 > 35 > 99 > 19 > 83 > 51 > 115 > 11 > 75 > 43 > 107 > 27 > 91 > 59 > 123 > 7 > 71 > 39 > 103 > 23 > 87 > 55 > 119 > 15 > 79 > 47 > 111 > 31 > 95 > 63 > 127 > 2 > 66 > 34 > 98 > 18 > 82 > 50 > 114 > 10 > 74 > 42 > 106 > 26 > 90 > 58 > 122 > 6 > 70 > 38 > 102 > 22 > 86 > 54 > 118 > 14 > 78 > 46 > 110 > 30 > 94 > 62 > 126 > 4 > 68 > 36 > 100 > 20 > 84 > 52 > 116 > 12 > 76 > 44 > 108 > 28 > 92 > 60 > 124 > 8 > 72 > 40 > 104 > 24 > 88 > 56 > 120 > 16 > 80 > 48 > 112 > 32 > 96 > 64 > 128. |  |  |  |  |  |

| 65407       | FF7Fh | Turns on for 511 GSCLK periods in the first to 127th display segments, but only turns on 510 GSCLK periods in the 128th display segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 65408       | FF80h | Turns on for 511 GSCLK periods in all display segments (first to 128th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 65409       | FF81h | Turns on for 512 GSCLK periods in the first display period and for 511 GSCLK periods in the second to 128th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|             | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 65534       | FFFEh | Turns on for 512 GSCLK periods in the first to 63th and 65th to 127th display segments; also turns on 511 GSCLK periods in 64th and 128th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 65535       | FFFFh | Turns on for 512 GSCLK periods in the first to 127th display segments but only turns on 511 GSCLK periods in the 128th display segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |