ZHCSB12-MAY 2013

TLK10232

# 具有交叉点的双通道 XAUI/10GBASE-KR 收发器

# 查询样品: TLK10232

# 1 介绍

#### 1.1 特性

- 双通道多速率收发器

- 支持 10GBASE-KR, XAUI, 和 1GBASE-KX 以太 网标准

- 支持所有数据速率高达 10Gbps 通用公共无线接口 (CPRI) 和开放基站架构协议 (OBSAI)

- 在高速端支持数据速率高达 10.3125Gbps 的多速率 串行解串器 (SERDES) 运行,在低速端支持的数据 速率高达 5Gbps

- 高速端和低速端上的差分电流模式逻辑 (CML) I/O 接口

- 到背板、无源和有源铜线缆、或者小尺寸可插拔 (SFP)+ 光模块的接口

- 可选基准时钟每通道(带有多输出时钟选项)

- 集成交叉点开关可实现灵活的信号路由和冗余输出

- 支持数据重定时操作

- 支持伪随机二进制序列 (PRBS),随机测试兼容模板 (CRPAT),长连续抖动测试图案 (CJPAT),高/低/ 混频模式,和 KR 伪随机模式生成以及验证,方波 生成

- 两个电源: 1.0V(内核),以及 1.5 或 1.8V (I/O)

# 1.2 应用范围

- 10GBASE-KR 兼容背板连接

- 10 兆位以太网交换机、路由器、和网络接口卡

- 无需电源排序

- 发送去加重功能和接收自适应均衡可允许扩展背板/ 线缆达到高速端和低速端

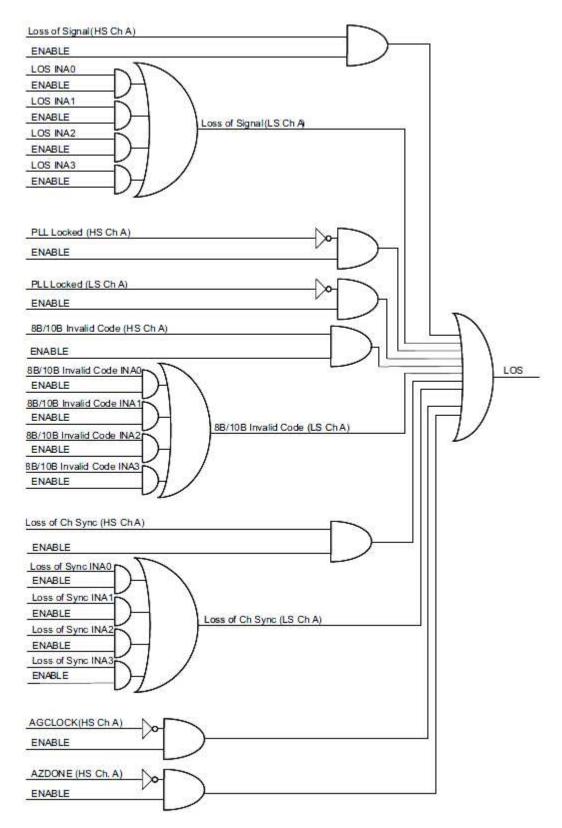

- 信号损失 (LOS) 检测

- 支持 10G-KR 链路协商、前向纠错、自动协商

- 超大数据包支持

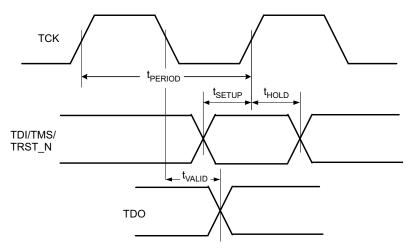

- JTAG; IEEE 1149.1 测试接口

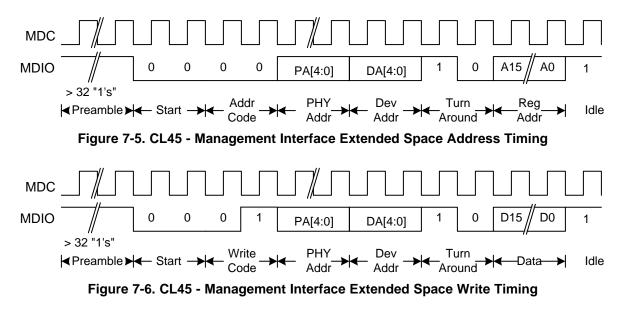

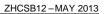

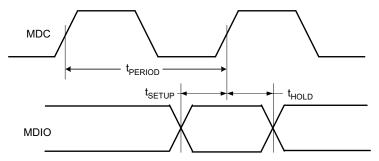

- 工业标准管理数据输入输出 (MDIO) 控制接口

- 65nm 高级 CMOS 技术

- 工业用环境运行温度(-40°C 至 85°C)

- 功耗:每通道 800mW (标称值)

- 器件封装: 13mm x 13mm, 144 引脚塑料球状引 脚栅格阵列封装 (PBGA), 1mm 焊球间距

- 私有线缆/背板连接

- 高速点到点传输系统

#### 1.3 说明

ÆΑ

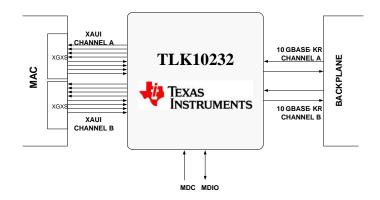

TLK10232 是一款双通道多速率收发器,此收发器用于高速双向点到点数据传输系统中。这个器件支持三个 主模式。它可被用作一个 XAUI 到 10GBASE-KR 的收发器、一个通用 8b/10b 多速率 4:1,2:1,1:1 串行 器/解串行器,或者被用在 1G-KX 模式中。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

运行在 10GBASE-KR 模式中时,TLK10232 将出现在其低速 (LS) 端数据输入上的 8B/10B 经编码 XAUI 数据流串行化。 经串行化的 8B/10B 经编码数据以 64B/66B 编码格式出现在高速 (HS) 端输出上。 相似的,TLK10232 对出现在其高速端数据输入上的 64B/66B 经编码数据流进行解串操作。 格式为 XAUI 8B/10B 的经解串行化 64B/66B 数据出现在低侧端输出上。 这个模式支持链路协商以及针对扩展长度应用的前向纠错 (FEC)。

当运行在通用 SERDES 模式时,TLK10232 将出现在其低速 (LS) 端数据输入上的 8B/10B 经编码数据流进 行 2:1 和 4:1 串化。 经串化的 8B/10B 编码数据出现在高速 (HS) 输出上。 相似的,TLK10232 将出现在其 高速端数据输入上的 8B/10B 编码数据流进行 1:2 和 1:4 解串化。 经解串化的 8B/10B 编码数据出现在低速 端输出上。 根据串化/解串化比率,低速端数据传输速率范围介于 0.5Gbps 至 5Gbps 之间,而高速端数据 传输速率介于 1Gbps 至 10Gbps 之间。还支持 1:1 重定时模式,但是速率限制在 1Gbps 至 5Gbps。

TLK10232 还支持具有 PCS (CTC) 功能的 1G-KX (1.25Gbps) 模式。通过软件服务开通或者自动协商可启 用这个模式。如果使用了软件服务开通,那么支持的数据传输速率可高达 3.125Gbps。

TLK10232 特有一个内置的交叉点开关,此开关可实现冗余输出和简便的数据重路由。每个输出端口(高速 或低速)能够被配置成输出来自任一器件输入端口的数据。此切换可通过一个硬件引脚或软件控制来启动, 并可被配置成立即切换,或配置成在当前数据包的末尾后出现。这可在不破坏数据包的情况下实现数据源之 间的切换。

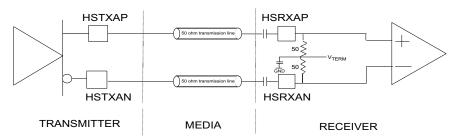

低速端和高速端数据输入和输出是具有集成端接电阻器的差分电流模式逻辑 (CML) 类型。

为了支持不同操作,TLK10232 提供了灵活的计时机制。 这些机制包括对使用一个从高速端恢复的外部抖动 清除时钟进行计时的支持。 此器件还能够在 10GBASE-KR 和 1GBASE-KX 模式下执行时钟容限补偿 (CTC),从而实现异步计时。

TLK10232 为自检和系统诊断用途提供低速端和高速端回路模式。

TLK10232 具有内置模式生成器和验证器以帮助进行系统测试。 此器件支持不同 PRBS,高/低/混合频率,CRPAT 长/短,CJPAT,和 KR 伪随机测试模式的生成和验证以及方波生成。 低速端和高速端上支持的模式类型取决于所选择的操作模式。

TLK10232 在高速端和低速端都具有一个集成信号损失 (LOS) 检测功能。 在输入差分电压摆幅少于 LOS 置 位阀值的条件下, LOS 被置为有效。

**TLK10232** 的两个通道是完全独立的。它们可以在不同的基准时钟、不同的数据速率、和不同的串化/解串化比率下运行。

TLK10232 的低速端非常适合与现场可编程栅极阵列 (FPGA),特定用途集成电路 (ASIC),媒体访问控制器 (MAC)或能够处理较低速率串行数据流的网络处理器对接。高速端非常适合通过光纤、电缆、或者背板接 口与远程系统对接。TLK10232 支持 SFP 和 SFP+ 光模块,以及 10GBASE-KR 兼容背板系统的运行。

# 2 Physical Characteristics

#### 2.1 Block Diagram

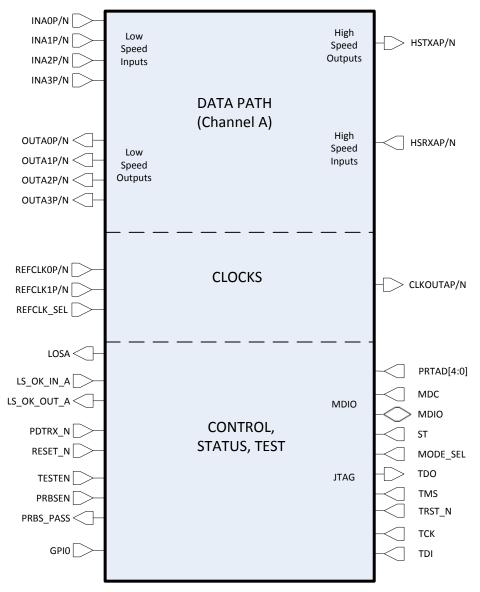

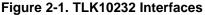

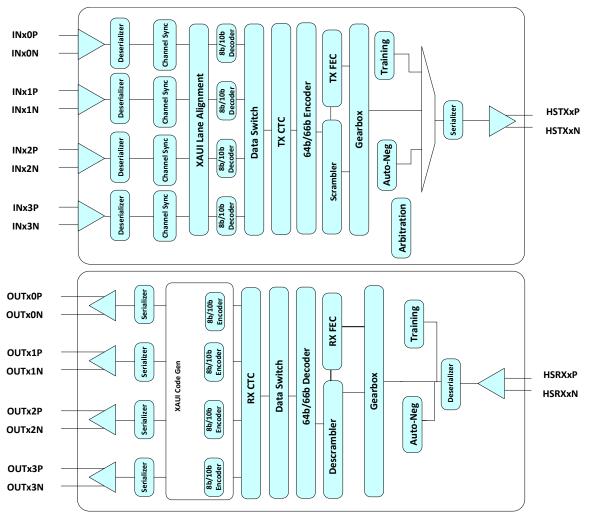

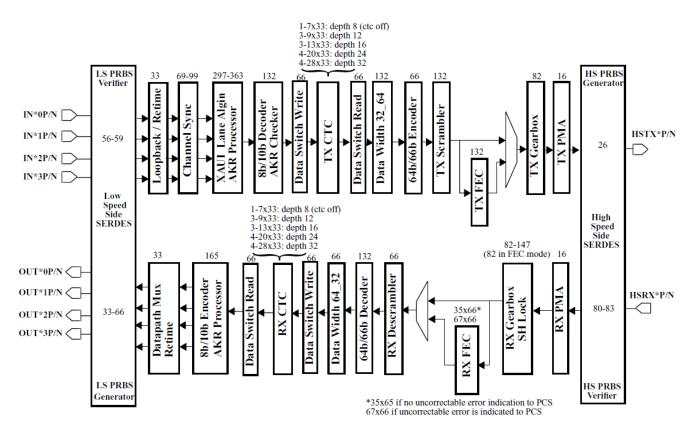

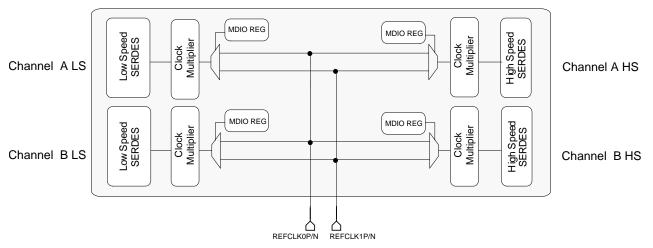

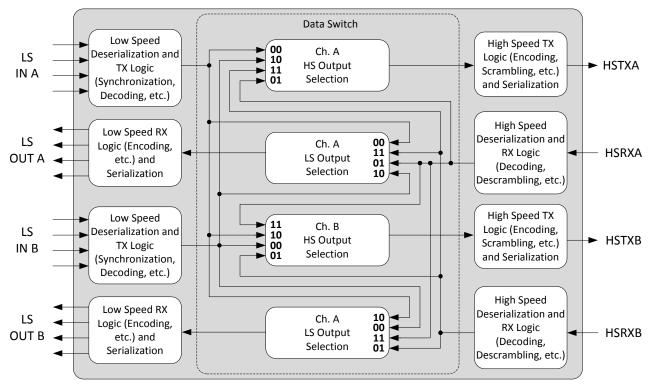

Various interfaces of the TLK10232 device are shown in Figure 2-1 for Channel A. The implementation is the same for Channel B. A simplified one-channel block diagram of both the transmit and recive data path is shown in Figure 2-2. This low-power transceiver consists of two serializer/deserializer (SERDES) blocks, one on the low speed side and the other on the high speed side. The core logic block that lies between the two SERDES blocks carries out all the logic functions including channel synchronization, lane alignment, 8B/10B and 64B/66B encoding/decoding, as well as test pattern generation and verification.

The TLK10232 provides a management data input/output (MDIO Clause 22/45) interface as well as a JTAG interface for device configuration, control, and monitoring. Detailed description of the TLK10232 pin functions is provided in Table 2-1.

# TLK10232

ZHCSB12-MAY 2013

www.ti.com.cn

Figure 2-2. A Simplified One Channel Block Diagram of the TLK10232 Data Paths

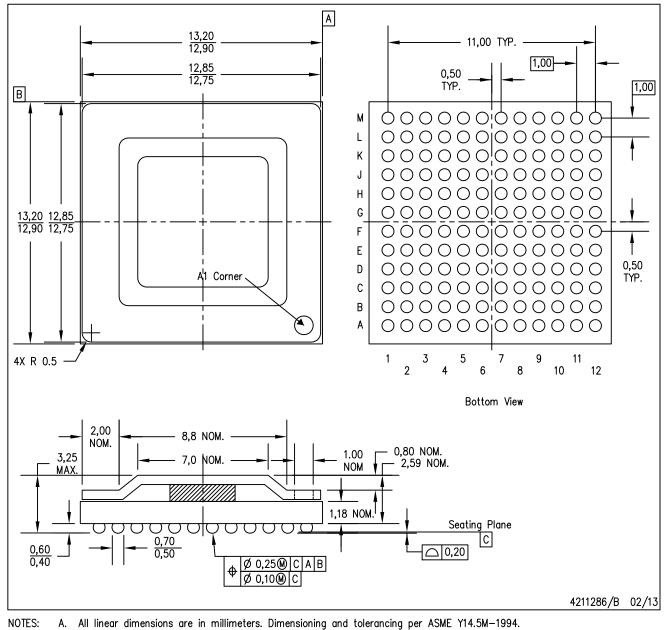

# 2.2 Package

A 13-mm x 13-mm, 144-pin PBGA package with a ball pitch of 1 mm is used. The device pin-out is as shown in Figure 2-3 and is described in detail in Table 2-1 and Table 2-2.

|   | 1      | 2       | 3        | 4        | 5       | 6      | 7      | 8          | 9           | 10         | 11       | 12     |

|---|--------|---------|----------|----------|---------|--------|--------|------------|-------------|------------|----------|--------|

| Α | INA1P  | VSS     | INAON    | INA0P    | VSS     | OUTA0P | OUTA0N | PDTRXA_N   | CLKOUTBP    | CLKOUTBN   | VSS      | HSRXAN |

| в | INA 1N | INA2P   | VSS      | VSS      | OUTA1P  | OUTA1N | VSS    | TMS        | PRBSEN      | LS_OK_IN_A | VSS      | HSRXAP |

| с | VSS    | INA2N   | VDDRA_LS | OUTA2P   | OUTA2N  | VSS    | VDD00  | TDI        | CLKOUTAP    | CLKOUTAN   | AMUXA    | VSS    |

| D | INA3P  | VDDA_LS | VSS      | AMUXB    | VSS     | TDO    | VPP    | тск        | LS_OK_OUT_A | VSS        | VSS      | HSTXAP |

| E | INA3N  | VSS     | OUTA3N   | VSS      | TRST_N  | VDDD   | DVDD   | VDDD       | LOSA        | PRTAD0     | VDDRA_HS | HSTXAN |

| F | VSS    | VDDA_LS | OUTA3P   | VDDT_LS  | VSS     | VDDD   | DVDD   | VSS        | VDDT_HS     | VSS        | VDDA_HS  | VSS    |

| G | VSS    | VDDA_LS | VSS      | VDDT_LS  | VSS     | DVDD   | VSS    | DVDD       | PRTAD1      | VDDA_HS    | VSS      | HSRXBN |

| н | INB0P  | VSS     | OUTBON   | VSS      | RESET_N | VDDD   | DVDD   | VDDD       | LS_OK_OUT_B | MODE_SEL   | VSS      | HSRXBP |

| ſ | INBON  | VDDA_LS | OUTB0P   | PDTRXB_N | VSS     | PRTAD3 | M DIO  | MDC        | PRBS_PASS   | GPI0       | VDDRB_HS | VSS    |

| к | VSS    | INB 1P  | VDDRB_LS | OUTB1N   | OUTB1P  | VSS    | VDDO1  | LOSB       | REFCLK1P    | REFCLK1N   | VSS      | HSTXBP |

| L | INB2P  | INB 1N  | VSS      | VSS      | OUTB2N  | OUTB2P | VSS    | LS_OK_IN_B | PRTAD2      | TESTEN     | VSS      | HSTXBN |

| м | INB2N  | VSS     | INB3P    | INB3N    | VSS     | OUTB3N | OUTB3P | PRTAD4     | ST          | REFCLK0P   | REFCLK0N | VSS    |

Figure 2-3. The Pin-Out of the TLK10232

#### www.ti.com.cn

# 2.3 Terminal Functions

The details of the terminal functions of the TLK10232 are provided in Table 2-1 and Table 2-2.

| TERMINA          | L                                | DIRECTION                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL           | BGA                              | TYPE<br>SUPPLY                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CHANNEL A        |                                  |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HSTXAP<br>HSTXAN | D12<br>E12                       | Output<br>CML VDDA_HS                          | High Speed Transmit Channel A Output. HSTXAP and HSTXAN comprise the high speed side transmit direction Channel A differential serial output signal. During device reset (RESET_N asserted low) these pins are driven differential zero. These CML outputs must be AC coupled.                                                                                                                                                                                                                                              |

| HSRXAP<br>HSRXAN | B12<br>A12                       | Input<br>CML VDDA_HS                           | High Speed Receive Channel A Input. HSRXAP and HSRXAN comprise the high speed side receive direction Channel A differential serial input signal. These CML input signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                |

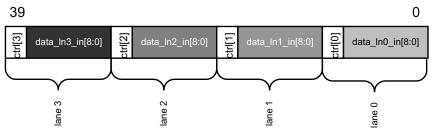

| INA[3:0]P/N      | D1/E1<br>B2/C2<br>A1/B1<br>A4/A3 | Input<br>CML VDDA_LS                           | Low Speed Channel A Inputs. INAP and INAN comprise the low speed side transmit direction Channel A differential input signals. These signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                                            |

| OUTA[3:0]P/N     | F3/E3<br>C4/C5<br>B5/B6<br>A6/A7 | Output<br>CML VDDA_LS                          | Low Speed Channel A Outputs. OUTAP and OUTAN comprise the low speed side receive direction Channel A differential output signals. During device reset (RESET_N asserted low) these pins are driven differential zero. These signals must be AC coupled.                                                                                                                                                                                                                                                                     |

| LOSA             | E9                               | Output LVCMOS<br>1.5V/1.8V<br>VDDO0 40Ω Driver | Channel A Receive Loss Of Signal (LOS) Indicator.<br>LOSA=0: Signal detected.<br>LOSA=1: Loss of signal.<br>Loss of signal detection is based on the input signal level. When HSRXAP/N has a<br>differential input signal swing of ≤75 mV <sub>pp</sub> , LOSA will be asserted (if enabled). If the input<br>signal is greater than 150 mV <sub>p-p</sub> , LOS will be deasserted. Outside of these ranges, the<br>LOS indication is undefined.<br>Other functions can be observed on LOSA real-time, configured via MDIO |

|                  |                                  | VDDO0 4022 Driver                              | During device reset (RESET_N asserted low) this pin is driven low. During pin based power down (PDTRXA_N asserted low), this pin is floating. During register based power down, this pin is floating.<br>It is highly recommended that LOSA be brought to an easily accessible point on the                                                                                                                                                                                                                                 |

|                  |                                  |                                                | application board (header) in the event that debug is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

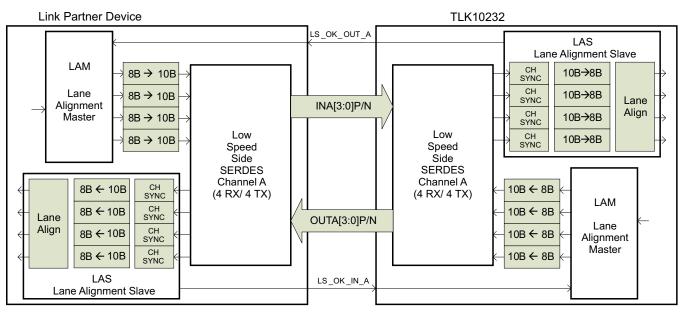

| LS_OK_IN_A       | B10                              | Input LVCMOS<br>1.5V/1.8V VDDO0                | Channel A Receive Lane Alignment Status Indicator.<br>Lane alignment status signal received from a Lane Alignment Slave on the link partner<br>device. Valid in 10G General Purpose Serdes Mode.<br>LS_OK_IN_A=0: Channel A link partner receive lanes not aligned.<br>LS_OK_IN_A=1: Channel A link partner receive lanes aligned                                                                                                                                                                                           |

| LS_OK_OUT_A      | D9                               | Output LVCMOS<br>1.5V/1.8V<br>VDDO0 40Ω Driver | Channel A Transmit Lane Alignment Status Indicator.<br>Lane alignment status signal sent to a Lane Alignment Master on the link partner device.<br>Valid in 10G General Purpose Serdes Mode.<br>LS_OK_OUT_A=0: Channel A link partner transmit lanes not aligned.<br>LS_OK_OUT_A=1: Channel A link partner transmit lanes aligned.                                                                                                                                                                                          |

| PDTRXA_N         | A8                               | Input LVCMOS<br>1.5V/1.8V VDDO0                | Transceiver Power Down.<br>When this pin is held low (asserted), Channel A is placed in power down mode. When<br>deasserted, Channel A operates normally. After deassertion, a software data path reset<br>should be issued through the MDIO interface.                                                                                                                                                                                                                                                                     |

| CHANNEL B        |                                  |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HSTXBP<br>HSTXBN | K12<br>L12                       | Output CML<br>VDDA_HS                          | High Speed Transmit Channel B Output. HSTXBP and HSTXBN comprise the high speed side transmit direction Channel B differential serial output signal. During device reset (RESET_N asserted low) these pins are driven differential zero. These CML outputs must be AC coupled.                                                                                                                                                                                                                                              |

| HSRXBP<br>HSRXBN | H12<br>G12                       | Input CML<br>VDDA_HS                           | High Speed Receive Channel B Input. HSRXBP and HSRXBN comprise the high speed side receive direction Channel B differential serial input signal. These CML input signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                |

| INB[3:0]P/N      | M3/M4<br>L1/M1<br>K2/L2<br>H1/J1 | Input CML<br>VDDA_LS                           | Low Speed Channel B Inputs. INBP and INBN comprise the low speed side transmit direction Channel B differential input signals. These signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                                            |

| OUTB[3:0]P/N     | M7/M6<br>L6/L5<br>K5/K4<br>J3/H3 | Output CML<br>VDDA_LS                          | Low Speed Channel B Outputs. OUTBP and OUTBN comprise the low speed side receive direction Channel B differential output signals. During device reset (RESET_N asserted low) these pins are driven differential zero. These signals must be AC coupled.                                                                                                                                                                                                                                                                     |

#### Table 2-1. Pin Description - Signal Pins

# Table 2-1. Pin Description - Signal Pins (continued)

| TERMINAL                 |                                                  | DIRECTION                                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|--------------------------|--------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SIGNAL                   | BGA                                              | TYPE<br>SUPPLY                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| LOSB                     | К8                                               | Output<br>LVCMOS 1.5V/1.8V                     | Channel B Receive Loss Of Signal (LOS) Indicator.<br>LOSB=0: Signal detected.<br>LOSB=1: Loss of signal.<br>Loss of signal detection is based on the input signal level.<br>When HSRXBP/N has a differential input signal swing of ≤75 mV <sub>pp</sub> , LOSB will be asserted<br>(if enabled). If the input signal is greater than 150 mV <sub>p-p</sub> , LOS will be deasserted. Outside<br>of these ranges, the LOS indication is undefined.     |  |  |  |  |  |

|                          |                                                  | VDDO1 40Ω Driver                               | Other functions can be observed on LOSB real-time, configured via MDIO<br>During device reset (RESET_N asserted low) this pin is driven low. During pin based<br>power down (PDTRXB_N asserted low), this pin is floating. During register based power<br>down, this pin is floating.                                                                                                                                                                 |  |  |  |  |  |

|                          |                                                  |                                                | It is highly recommended that LOSB be brought to easily accessible point on the application board (header), in the event that debug is required.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| LS_OK_IN_B               | L8                                               | Input<br>LVCMOS 1.5V/1.8V<br>VDDO0             | Channel B Receive Lane Alignment Status Indicator. Lane alignment status signal received from a Lane Alignment Slave on the link partner device. Valid in 10G General Purpose Serdes Mode.<br>LS_OK_IN_B=0: Channel B Receive lanes not aligned.<br>LS_OK_IN_B=1: Channel B Receive lanes aligned                                                                                                                                                     |  |  |  |  |  |

| LS_OK_OUT_B              | H9                                               | Output<br>LVCMOS 1.5V/1.8V<br>VDDO0 40Ω Driver | Channel B Transmit Lane Alignment Status Indicator. Lane alignment status signal<br>sent to a Lane Alignment Master on the link partner device. Valid in 10G General Purpose<br>Serdes Mode.<br>LS_OK_OUT_B=0: Channel B Transmit lanes not aligned.<br>LS_OK_OUT_B=1: Channel B Transmit lanes aligned.                                                                                                                                              |  |  |  |  |  |

| PDTRXB_N                 | J4                                               | Input<br>LVCMOS<br>1.5V/1.8V VDDO1             | <b>Transceiver Power Down.</b> When this pin is held low (asserted), Channel B is placed in power down mode. When deasserted, Channel B operates normally. After deassertion, a software data path reset should be issued through the MDIO interface.                                                                                                                                                                                                 |  |  |  |  |  |

| REFERENCE CLOCKS, C      | UTPUT CLOO                                       | CKS, AND CONTROL AND                           | MONITORING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| REFCLK0P/N               | M10<br>M11                                       | Input<br>LVDS/ LVPECL<br>DVDD                  | Reference Clock Input Zero. This differential input is a clock signal used as a reference to channels A or B. The reference clock selection is done through MDIO. This input signal <b>must</b> be AC coupled. If unused, REFCLK0P/N should be pulled down to GND through a shared 100 $\Omega$ resistor.                                                                                                                                             |  |  |  |  |  |

| REFCLK1P/N               | K9<br>K10                                        | Input<br>LVDS/ LVPECL<br>DVDD                  | Reference Clock Input One. This differential input is a clock signal used as a reference to channels A or B. The reference clock selection is done through MDIO. This input signal must be AC coupled. If unused, REFCLK1P/N should be pulled down to GND through a shared 100 $\Omega$ resistor.                                                                                                                                                     |  |  |  |  |  |

| CLKOUTAP/N<br>CLKOUTBP/N | C9/C10<br>A9/A10                                 | Output<br>CML                                  | <b>Channel A/B Output Clock.</b> By default, these outputs are enabled and output the high speed side Channel A recovered byte clock (high speed line rate divided by 16 or 20). Optionally, they can be configured to output the VCO clock divided by 2. (Note: for full rates, VCO/2 pre-divided clocks will be equivalent to the line rate divided by 8; for subrates, VCO/2 pre-divided clocks will be equivalent to the line rate divided by 4). |  |  |  |  |  |

|                          | //3///10                                         | DVDD                                           | These CML outputs must be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                          |                                                  |                                                | During device reset (RESET_N asserted low), pin-based power down (PDTRXA_N and PDTRXB_N asserted low), or register-based power down, these pins are floating.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| PRBSEN                   | В9                                               | Input<br>LVCMOS 1.5V/1.8V                      | <b>Enable PRBS:</b> When this pin is asserted high, the internal PRBS generator and verifier circuits are enabled on both transmit and receive data paths on high speed and low speed sides of both channels.                                                                                                                                                                                                                                         |  |  |  |  |  |

|                          |                                                  | VDDO0                                          | The PRBS 27-1 pattern is selected by default, and can be changed through MDIO.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                          |                                                  | Output                                         | Receive PRBS Error Free (Pass) Indicator.<br>When PRBS test is enabled (PRBSEN=1):<br>PRBS_PASS=1 indicates that PRBS pattern reception is error free.<br>PRBS_PASS=0 indicates that a PRBS error is detected. The channel, high speed or low<br>speed side, and lane (for low speed side) that this signal refers to is chosen through<br>MDIO.                                                                                                      |  |  |  |  |  |

| PRBS_PASS                | RBS_PASS J9 LVCMOS 1.5V/1.8\<br>VDDO1 40Ω Driver |                                                | During device reset (RESET_N asserted low) this pin is driven high.<br>During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is<br>floating.<br>During register based power down, this pin is floating.                                                                                                                                                                                                                          |  |  |  |  |  |

|                          |                                                  |                                                | It is highly recommended that PRBS_PASS be brought to easily accessible point on the application board (header), in the event that debug is required.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ST                       | М9                                               | Input<br>LVCMOS 1.5V/1.8V                      | <b>MDIO Select</b> . Used to select Clause 22 (=1) or Clause 45 (=0) operation. Note that selecting clause 22 will impact mode availability. See MODE_SEL.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                          |                                                  | VDDO[1:0]                                      | A hard or soft reset must be applied after a change of state occurs on this input signal.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| MODE_SEL                 | H10                                              | Input LVCMOS<br>1.5V/1.8V VDDO[1:0]            | Device Operating Mode Select.<br>Used together with ST pin to select device operating mode. See Table 2-3 for details.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

Copyright © 2013, Texas Instruments Incorporated

www.ti.com.cn

# TLK10232

ZHCSB12-MAY 2013

# Table 2-1. Pin Description - Signal Pins (continued)

| TERMINAL   |                       | DIRECTION                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|------------|-----------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SIGNAL     | BGA                   | TYPE<br>SUPPLY                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|            |                       |                                                        | MDIO Port Address. Used to select the MDIO port address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|            | M8<br>J6              |                                                        | PRTAD[4:1] selects the MDIO port address. The TLK10232 has two different MDIO port addresses. Selecting a unique PRTAD[4:1] per TLK10232 device allows 16 TLK10232 devices per MDIO bus. Each channel can be accessed by setting the appropriate port address field within the serial interface protocol transaction.                                                                                                                                                                                                                                   |  |  |  |  |

| PRTAD[4:0] | 56<br>L9<br>G9<br>E10 | Input LVCMOS<br>1.5V/1.8V VDDO[1:0]                    | The TLK10232 will respond if the 4 MSB's of the port address field on MDIO protocol (PA[4:1]) matches PRTAD[4:1].<br>If PA[0] = 1'b0, TLK10232 Channel A will respond.<br>If PA[0] = 1'b1, TLK10232 Channel B will respond.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|            |                       |                                                        | PRTAD0 is not needed for port addressing, but can be used as a general purpose input pin to control the switching function or the stopwatch latency measurement. If these functions are not needed, PRTAD0 should be grounded on the application board.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| RESET_N    | H5                    | Input LVCMOS<br>1.5V/1.8V VDDO01                       | <b>Low True Device Reset.</b> RESET_N must be held asserted (low logic level) for at least 10us after device power stabilization.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| MDC        | J8                    | Input LVCMOS<br>with Hysteresis<br>1.5V/1.8V VDDO1     | <b>MDIO Clock Input.</b> Clock input for the MDIO interface.<br>Note that an external pullup is generally not required on MDC except if driven by an open drain/open-collector clock source.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|            |                       |                                                        | MDIO Data I/O. MDIO interface data input/output signal for the MDIO interface. This signal must be externally pulled up to VDDO using a $2k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MDIO       | J7                    | Input/ Output<br>LVCMOS 1.5V/1.8V<br>VDDO1 25Ω Driver  | During device reset (RESET_N asserted low) this pin is floating. During software initiated power down the management interface remains active for control register writes and reads. Certain status bits will not be deterministic as their generating clock source may be disabled as a result of asserting either power down input signal. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is floating. During register based power down, this pin is driven normally.                                                     |  |  |  |  |

| TDI        | C8                    | Input LVCMOS<br>1.5V/1.8V VDDO0<br>(Internal Pullup)   | <b>JTAG Input Data.</b> TDI is used to serially shift test data and test instructions into the device during the operation of the test port. In system applications where JTAG is not implemented, this input signal may be left floating. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled up. During register based power down, this pin is pulled up normally.                                                                                                                                               |  |  |  |  |

| TDO        | D6                    | Output LVCMOS<br>1.5V/1.8V VDDO0<br>50Ω Driver         | JTAG Output Data. TDO is used to serially shift test data and test instructions out of the device during operation of the test port. When the JTAG port is not in use, TDO is in a high impedance state.<br>During device reset (RESET_N asserted low) this pin is floating. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled up. During register based power down, this pin is pulled up normally.                                                                                                             |  |  |  |  |

| TMS        | B8                    | Input LVCMOS<br>1.5V/1.8V VDDO0<br>(Internal Pullup)   | JTAG Mode Select. TMS is used to control the state of the internal test-port controller. In system applications where JTAG is not implemented, this input signal can be left unconnected.<br>During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled up. During register based power down, this pin is pulled up normally.                                                                                                                                                                                             |  |  |  |  |

| тск        | D8                    | Input LVCMOS<br>with Hysteresis<br>1.5V/1.8V VDDO0     | <b>JTAG Clock.</b> TCK is used to clock state information and test data into and out of the device during boundary scan operation. In system applications where JTAG is not implemented, this input signal should be grounded.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| TRST_N     | E5                    | Input LVCMOS<br>1.5V/1.8V VDDO0<br>(Internal Pulldown) | JTAG Test Reset. TRST_N is used to reset the JTAG logic into system operational mode. This input can be left unconnected in the application and is pulled down internally, disabling the JTAG circuitry. If JTAG is implemented on the application board, this signal should be deasserted (high) during JTAG system testing, and otherwise asserted (low) during normal operation mode. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled up. During register based power down, this pin is pulled up normally. |  |  |  |  |

| TESTEN     | L10                   | Input LVCMOS<br>1.5V/1.8V VDDO1                        | <b>Test Enable.</b> This signal is used during the device manufacturing process. It should be grounded through a resistor in the device application board. The application board should allow the flexibility of easily reworking this signal to a high level if device debug is necessary (by including an uninstalled resistor to VDDO).                                                                                                                                                                                                              |  |  |  |  |

| GPI0       | J10                   | Input LVCMOS<br>1.5V/1.8V VDDO1                        | General Purpose Input. This signal is used during the device manufacturing process. It should be grounded through a resistor on the device application board. The application board should also allow the flexibility of easily reworking this signal to a high level if device debug is necessary (by including an uninstalled resistor to VDDO).                                                                                                                                                                                                      |  |  |  |  |

| AMUXA      | C11                   | Analog I/O                                             | SERDES Channel A Analog Testability I/O. This signal is used during the device manufacturing process. It should be left unconnected in the device application.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| AMUXB      | D4                    | Analog I/O                                             | SERDES Channel B Analog Testability I/O. This signal is used during the device manufacturing process. It should be left unconnected in the device application.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

www.ti.com.cn

Table 2-2. Pin Description - Power Pins

| TERMINAL    |                                                                                                                                                                                                         | TYPE   | DESCRIPTION                                                                                                                                                                                                                        |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SIGNAL      | BGA                                                                                                                                                                                                     | TYPE   | DESCRIPTION                                                                                                                                                                                                                        |  |  |  |  |  |

| VDDA_LS/HS  | D2, F2, G2, J2, G10,<br>F11                                                                                                                                                                             | Power  | <b>SERDES Analog Power.</b><br>VDDA_LS and VDDA_HS provide supply voltage for the analog circuits on the low-speed and high-speed sides respectively. 1.0V nominal. Can be tied together on the application board.                 |  |  |  |  |  |

| VDDT_LS/HS  | F4, G4, F9                                                                                                                                                                                              | Power  | <b>SERDES Analog Power.</b><br>VDDT_LS and VDDT_HS provide termination and supply voltage for the analog circuits on the low-speed and high-speed sides respectively. 1.0V nominal. Can be tied together on the application board. |  |  |  |  |  |

| VDDD        | E6, F6, H6, E8, H8                                                                                                                                                                                      | Power  | SERDES Digital Power.<br>VDDD provides supply voltage for the digital circuits internal to the SERDES.<br>1.0V nominal.                                                                                                            |  |  |  |  |  |

| DVDD        | G6, E7, F7, H7, G8                                                                                                                                                                                      | Power  | <b>Digital Core Power.</b><br>DVDD provides supply voltage to the digital core. 1.0V nominal.                                                                                                                                      |  |  |  |  |  |

| VDDRA_LS/HS | C3<br>E11                                                                                                                                                                                               | Power  | SERDES Analog Regulator Power.<br>VDDRA_LS and VDDRA_HS provide supply voltage for the internal PLL<br>regulator for Channel A low speed and high speed sides respectively. 1.5V or<br>1.8V nominal.                               |  |  |  |  |  |

| VDDRB_LS/HS | K3<br>J11                                                                                                                                                                                               | Power  | <b>SERDES Analog Regulator Power</b><br>VDDRB_LS and VDDRB_HS provide supply voltage for the internal PLL<br>regulator for Channel B low speed and high speed sides respectively. 1.5V or<br>1.8V nominal.                         |  |  |  |  |  |

| VDDO[1:0]   | K7<br>C7                                                                                                                                                                                                | Power  | <b>LVCMOS I/O Power.</b><br>VDDO0 and VDDO1 provide supply voltage for the LVCMOS inputs and outputs. 1.5V or 1.8V nominal. Can be tied together on the application board.                                                         |  |  |  |  |  |

| VPP         | D7                                                                                                                                                                                                      | Power  | <b>Factory Program Voltage.</b><br>Used during device manufacturing. The application must connect this power supply directly to DVDD.                                                                                              |  |  |  |  |  |

| VSS         | A2, A5, A11, B3, B4,<br>B7, B11, C1, C6,<br>C12, D3, D5, D10,<br>D11, E2, E4, F1, F5,<br>F8, F10, F12, G1,<br>G3, G5, G7, G11, H2,<br>H4, H11, J5, J12, K1,<br>K6, K11, L3, L4, L7,<br>L11, M2, M5, M12 | Ground | <b>Ground.</b><br>Common analog and digital ground.                                                                                                                                                                                |  |  |  |  |  |

# 2.4 Operating Modes

The TLK10232 is a versatile high-speed transceiver device that is designed to perform various physical layer functions in three operating modes: 10GBASE-KR Mode, 1G-KX Mode, and General Purpose (10G) SERDES Mode. The three modes are described in three separate sections. The device operating mode is determined by the MODE\_SEL and ST pin settings, as well as MDIO register 1E.0001 bit 10.

| Table 2-3. TLK10232 C | perating Mode Selection |

|-----------------------|-------------------------|

|-----------------------|-------------------------|

|                                            | ST = 0 (Clause 45)                       | ST = 1 (Clause 22)     |

|--------------------------------------------|------------------------------------------|------------------------|

| {MODE_SEL pin, Register<br>1E.0001 bit 10} |                                          |                        |

| 1x                                         | 10G                                      | 10G                    |

| 01                                         | 10G                                      | 10G                    |

| 00                                         | 10G-KR/1G-KX<br>(Determined by Auto Neg) | 1G-KX<br>(No Auto Neg) |

TEXAS INSTRUMENTS

TLK10232

ZHCSB12-MAY 2013

www.ti.com.cn

# 3 10GBASE-KR MODE FUNCTIONAL DESCRIPTION

A simplified block diagram of the transmit and receive data paths in 10GBASE-KR mode is shown in Figure 3-1. This section gives a high-level overview of how data moves through these paths, then gives a more detailed description of each block's functionality.

Figure 3-1. A Simplified One Channel KR Data Path Block Diagram

# 3.1 10GBASE-KR Transmit Data Path Overview

In 10GBASE-KR Mode, the TLK10232 takes in XAUI data on the four low speed input lanes. The serial data in each lane is deserialized into 10-bit parallel data, then byte aligned (channel synchronized) based on comma detection. The four XAUI lanes are then aligned with one another, and the aligned data is input to four 8B/10B decoders. The decoded data is then input to the transmit clock tolerance compensation (CTC) block which compensates for any frequency offsets between the incoming XAUI data and the local reference clock. The CTC block then delivers the data to a 64B/66B encoder and a scrambler. The resulting scrambled 10GBASE-KR data is then input to a transmit gearbox which in turn delivers it to the high speed side SERDES for serialization and output through the HSTX\*P/N pins.

www.ti.com.cn

# 3.2 10GBASE-KR Receive Data Path Overview

In the receive direction, the TLK10232 will take in 64B/66B-encoded serial 10GBASE-KR data on the HSRX\*P/N pins. This data is deserialized by a high speed SERDES, then input to a receive gearbox. After the gearbox, the data is aligned to 66-bit frames, descrambled, 64B/66B decoded, and then input to the receive CTC block. After CTC, the data is encoded by four 8B/10B encoders, and the resulting four 10-bit parallel words are serialized by the low speed SERDES blocks. The four serial XAUI output lanes are transmitted out the OUT\*P/N pins.

# 3.3 Channel Synchronization Block

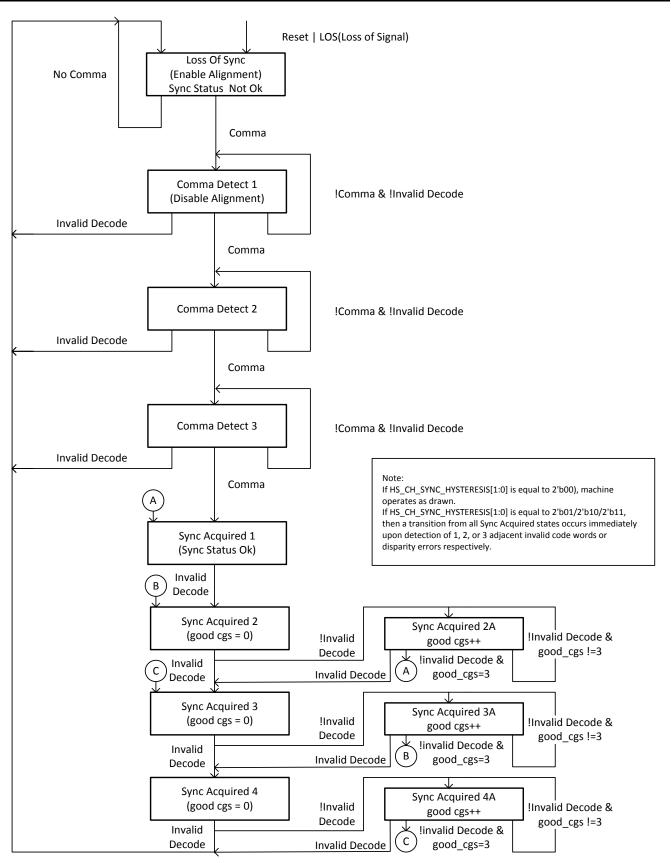

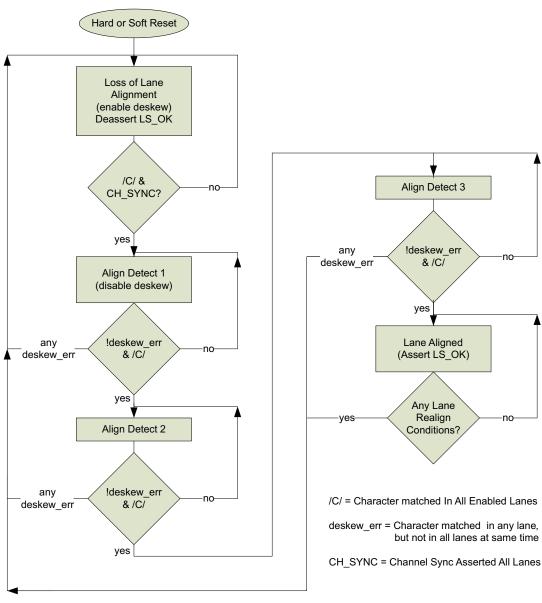

When parallel data is clocked into a parallel-to-serial converter, the byte boundary that was associated with the parallel data is lost in the serialization of the data. When the serial data is received and converted to parallel format again, a method is needed to be able to recognize the byte boundary again. Generally, this is accomplished through the use of a synchronization pattern. This is a unique pattern of 1's and 0's that either cannot occur as part of valid data or is a pattern that repeats at defined intervals. 8B/10B encoding contains a character called the comma (b'0011111' or b'1100000') which is used by the comma detect circuit to align the received serial data back to its original byte boundary. The TLK10232 channel synchronization block detects the comma pattern found in the K28.5 character, generating a synchronization signal aligning the data to their 10-bit boundaries for decoding. It is important to note that the comma can be either a (b'0011111') or the inverse (b'1100000') depending on the running disparity. The TLK10232 decoder will detect both patterns.

The TLK10232 performs channel synchronization per lane as shown in the flowchart of Figure 3-2.

ZHCSB12-MAY 2013

# 3.4 8B/10B Encoder

Embedded-clock serial interfaces require a method of encoding to ensure sufficient transition density for the receiving CDR to acquire and maintain lock. The encoding scheme also maintains the signal DC balance by keeping the number of ones and zeros balanced which allows for AC coupled data transmission. The TLK10232 uses the 8B/10B encoding algorithm that is used by the 10 Gbps and 1 Gbps Ethernet and Fibre Channel standards. This provides good transition density for clock recovery and improves error checking.

The 8B/10B encoder converts each 8-bit wide data to a 10-bit wide encoded data character to improve its transition density. This transmission code includes /D/ characters, used for transmitting data, and /K/ characters, used for transmitting protocol information. Each /K/ or /D/ character code word can also have both a positive and a negative disparity version. The disparity of a code word is selected by the encoder to balance the running disparity of the serialized data stream.

# 3.5 8B/10B Decoder

Once the Channel Synchronization block has identified the byte boundaries from the received serial data stream, the 8B/10B decoder converts 10-bit 8B/10B-encoded characters into their respective 8-bit formats. When a code word error or running disparity error is detected in the decoded data, the error is reported in the status register (1E.000F) and the LOS pin is asserted (depending on the LOS overlay selection).

# 3.6 64B/66B Encoder/Scrambler

To facilitate the transmission of data received from the media access control (MAC) layer, the TLK10232 encodes data received from the MAC using the 64B/66B encoding algorithm defined in the IEEE802.3-2008 standard. The TLK10232 takes two consecutive transfers from the XAUI interface and encodes them into a 66-bit code word. The information from the two XAUI transfers includes 64 bits of data and 8 bits of control information after 8B/10B decoding.

If the 64B/66B encoder detects an invalid packet format from the XAUI interface, it replaces erroneous information with appropriately-encoded error information. The resulting 66-bit code word is then sent on to the transmit gearbox.

The encoding process implemented in the TLK10232 includes two steps:

- 1. an encoding step, which converts the 72 bits of data (8 data bytes plus 8 control-code indicators) received from the transmit CTC FIFO into a 66-bit code word

- 2. a scrambling step, which scrambles 64 bits of encoded data using the scrambler polynomial x<sup>58</sup>+x<sup>39</sup>+1. The 66 bits created by the encoder consists of 64 bits of data and a 2-bit synchronization field consisting of either 01 or 10. Only the 64 bits of data are scrambled, leaving the two synchronization bits unmodified. The two synchronization bits allow the receive gearbox to obtain frame alignment and, in addition, ensure an edge transition of at least once in 66 bits of data. The encoding process allows a limited amount of control information to be sent in-line with the data.

# 3.7 Forward Error Correction

Optionally enabled, Forward Error Correction (FEC) follows the IEEE 802.3-2008 standard, and is able to correct a burst errors up to 11 bits. In the TX data path, the FEC logic resides between the scrambler and gearbox. In the RX datapath, FEC resides between the gearbox and descrambler. Frame alignment is handled inside the RX FEC block during FEC operation, and the RX gearbox sync header alignment is bypassed. Because latency is increased in both the TX and RX data paths with FEC enabled, it is disabled by default and must be enabled through MDIO programming. Note that FEC by nature will add latency due to frame storage.

#### 3.8 64B/66B Decoder/Descrambler

The data received from the serial 10GBASE-KR is 64B/66B-encoded data. The TLK10232 decodes the data received using the 64B/66B decoding algorithm defined in the IEEE 802.3-2008 standard. The TLK10232 creates consecutive 72-bit data words from the encoded 66-bit code words for transfer over the XAUI interface to the MAC. The information for the two XAUI transfers includes 64 bits of data and 8 bits of control information before 8B/10B encoding.

Not all 64B/66B block payloads are valid. Invalid block payloads are handled by the 64B/66B decoder block and appropriate error handling is provided, as defined in the IEEE 802.3-2008 standard. The decoding algorithm includes two steps: a descrambling step which descrambles 64 bits of the 66-bit code word with the scrambling polynomial  $x^{58}+x^{39}+1$ , and a decoding step which converts the 66 bits of data received into 64 bits of data and 8 bits of control information. These words are sent to the receive CTC FIFO.

#### 3.9 Transmit Gearbox

The function of the transmit gearbox is to convert the 66-bit encoded, scrambled data stream into a 16-bitwide data stream to be sent out to the serializer and ultimately to the physical medium attachment (PMA) device. The gearbox is needed because while the effective bit rate of the 66-bit data stream is equal to the effective bit rate of the 16-bit data, the clock rates of the two buses are of different frequencies.

#### 3.10 Receive Gearbox

While the transmit gearbox only performs the task of converting 66-bit data to be transported on to the 16bit serializer, the receive gearbox has more to do than just the reverse of this function. The receive gearbox must also determine where within the incoming data stream the boundaries of the 66-bit code words are.

The receive gearbox has the responsibility of initially synchronizing the header field of the code words and continuously monitoring the ongoing synchronization. After obtaining synchronization to the incoming data stream, the gearbox assembles 66-bit code words and presents these to the 64B/66B decoder.

Note that in FEC mode, the Receive Gearbox blindly converts 16-bit data to 66-bit data and depends on the RX FEC logic to frame align the data.

# 3.11 XAUI Lane Alignment / Code Gen (XAUI PCS)

The XAUI interface standard is defined to allow for 21 UI of skew between lanes. This block is implemented to handle up to 30 UI (XAUI UI) of skew between lanes using /A/ characters. The state machine follows the standard 802.3-2008 defined state machine.

# 3.12 Inter-Packet Gap (IPG) Characters

The XAUI interface transports information that consists of packets and inter-packet gap (IPG) characters. The IEEE 802.3-2008 standard defines that the IPG, when transferred over the XAUI interface, consists of alignment characters (/A/), control characters (/K/) and replacement characters (/R/).

TLK10232 converts all AKR characters to IDLE characters, performs insertions or deletions on the IDLE characters, and transmits only encoded IDLE characters out to the 10GBASE-KR interface. The receive channel expects encoded IDLE characters to enter the 10GBASE-KR interface, and performs insertions and deletions on IDLE characters and then converts IDLE characters back to AKR characters. Any AKR characters received on the high speed interface are by default converted to IDLE characters for reconversion to AKR columns.

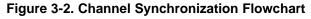

Both the transmit and receive FIFOs rely upon a valid IDLE stream to perform clock tolerance compensation (CTC).

# 3.13 Clock Tolerance Compensation (CTC)

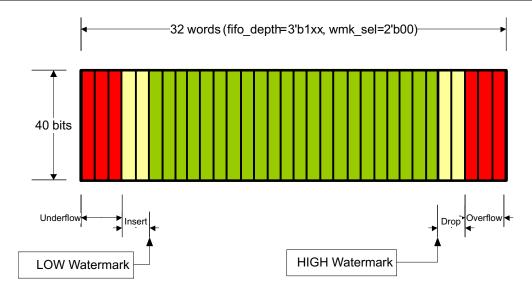

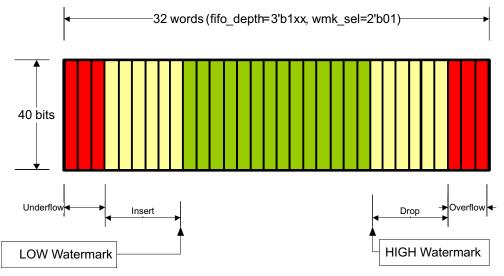

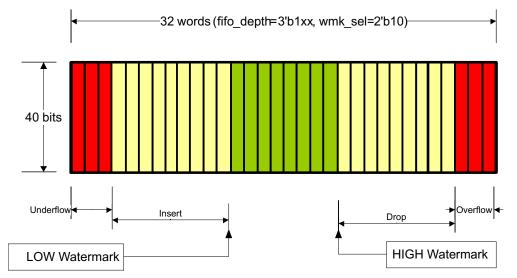

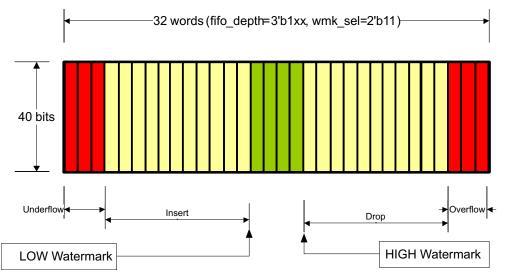

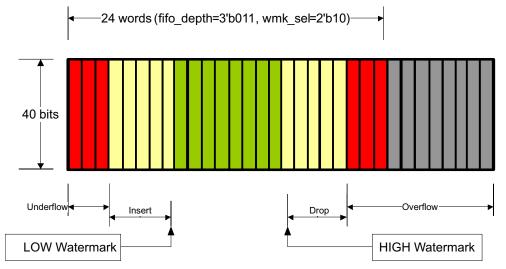

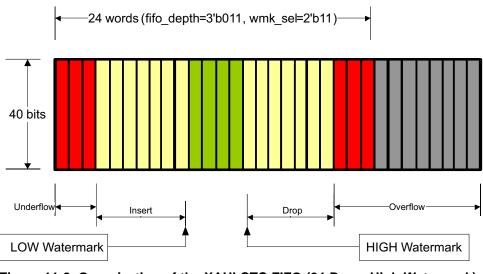

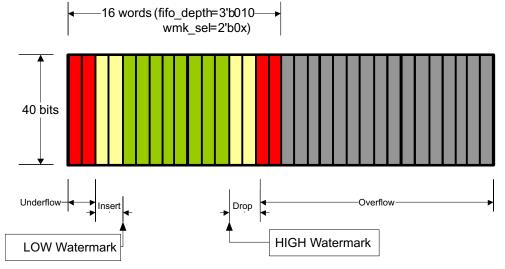

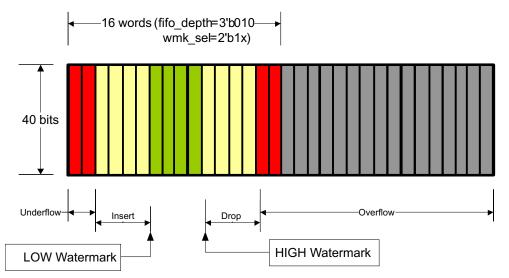

The XAUI interface is defined to allow for separate clock domains on each side of the link. Though the reference clocks for two devices on a XAUI link have the same specified frequencies, there can be slight differences that, if not compensated for, will lead to over or under run of the FIFO's on the receive/transmit data path. The TLK10232 provides compensation for these differences in clock frequencies via the insertion or the removal of idle (/I/) characters on all lanes, as shown in Figure 3-3 and Figure 3-4.

# Figure 3-4. Clock Tolerance Compensation: Drop

The TLK10232 allows for provisioning of both the CTC FIFO depth and the low/high watermark thresholds that trigger idle insertion/deletion beyond the standard requirements. This allows for optimization between maximum clock tolerance and packet length. For more information on the TLK10232 CTC provisioning, see Appendix A.

# 3.14 10GBASE-KR Auto-Negotiation

When TLK10232 is selected to operate in 10GKR/1G-KX mode (MODE\_SEL pin held low), Clause 73 Auto-Negotiation will commence after power up or hardware or software reset. The data path chosen from the result of Auto-Negotiation will be the highest speed of 10G-KR or 1G-KX as advertised in the MDIO ability fields (set to 10G-KR by default). If 10G-KR is chosen, link training will commence immediately following the completion of Auto-Negotiation. Legacy devices that operate in 1G-KX mode and do not support Clause 73 Auto Negotiation will be recognized through the Clause 73 parallel detection mechanism.

# 3.15 10GBASE-KR Link Training

Link training for 10G-KR mode is performed after auto-negotiation, and follows the procedure described in IEEE 802.3-2008. The high speed TX SERDES side will update pre-emphasis tap coefficients as requested through the Coefficient update field. Received training patterns are monitored for bit errors (MDIO configurable), and requests are made to update partner channel TX coefficients until optimal settings are achieved.

The RX link training algorithm consists of sending a series of requests to move the link partner's transmitter tap coefficients to the center point of an error free region. Once link training has completed, the 10G-KR data path is enabled. If link is lost, the entire process repeats with auto-negotiation, link training, and 10G-KR mode.

TLK10232 also offers a manual mode whereby coefficient update requests are handled through external software management.

# 3.16 10GBASE-KR Line Rate, PLL Settings, and Reference Clock Selection

The TLK10232 includes internal low-jitter high quality oscillators that are used as frequency multipliers for the low speed and high speed SERDES and other internal circuits of the device. Specific MDIO registers are available for SERDES rate and PLL multiplier selection to match line rates and reference clock (REFCLK0/1) frequencies for various applications.

The external differential reference clock has a large operating frequency range allowing support for many different applications. A low-jitter reference clock should be used, and its frequency accuracy should be within  $\pm 200$  PPM of the incoming serial data rate ( $\pm 100$  PPM of nominal data rate).

When the TLK10232 device is set to operate in the 10GBASE-KR mode with a low speed side line rate of 3.125 Gbps and a high speed side line rate of 10.3125 Gbps, the reference clock choices are as shown in Table 3-1. In general, using a higher reference clock frequency results in improved jitter performance.

|                     | LOW SPEED SIDE           |      |                    |  |                     | HIGH SPEED SIDE          |      |                    |  |  |  |

|---------------------|--------------------------|------|--------------------|--|---------------------|--------------------------|------|--------------------|--|--|--|

| Line Rate<br>(Mbps) | SERDES PLL<br>Multiplier | Rate | REFCLKP/N<br>(MHz) |  | Line Rate<br>(Mbps) | SERDES PLL<br>Multiplier | Rate | REFCLKP/N<br>(MHz) |  |  |  |

| 3125                | 10                       | Full | 156.25             |  | 10312.5             | 16.5                     | Full | 156.25             |  |  |  |

| 3125                | 5                        | Full | 312.5              |  | 10312.5             | 8.25                     | Full | 312.5              |  |  |  |

Table 3-1. Specific Line Rate and Reference Clock Selection for the 10GBASE-KR Mode:

# 3.17 10GBASE-KR Test Pattern Support

The TLK10232 has the capability to generate and verify various test patterns for self-test and system diagnostic measurements. The following test patterns are supported:

- High Speed (HS) Side: PRBS 2<sup>7</sup> 1, PRBS 2<sup>23</sup> 1, PRBS 2<sup>31</sup> 1, Square Wave with Provisionable Length, and KR Pseudo-Random Pattern

- Low Speed (LS) Side: PRBS 2<sup>7</sup> 1, PRBS 2<sup>23</sup> 1, PRBS 2<sup>31</sup> 1, High Frequency, Low Frequency, Mixed Frequency, CRPAT, CJPAT.

The TLK10232 provides two pins: PRBSEN and PRBS\_PASS, for additional control and monitoring of PRBS pattern generation and verification. When PRBSEN is asserted high, the internal PRBS generator and verifier circuits are enabled on both transmit and receive data paths on high speed and low speed sides of all channels. PRBS 2<sup>7</sup>-1 is selected by default, and can be changed through MDIO.

When PRBS test is enabled (PRBSEN=1):

- PRBS\_PASS = 1 indicates that PRBS pattern reception is error free.

- PRBS\_PASS = 0 indicates that a PRBS error is detected. The channel, the side (high speed or low speed), and the lane (for low speed side) that this signal refers to is chosen through MDIO.

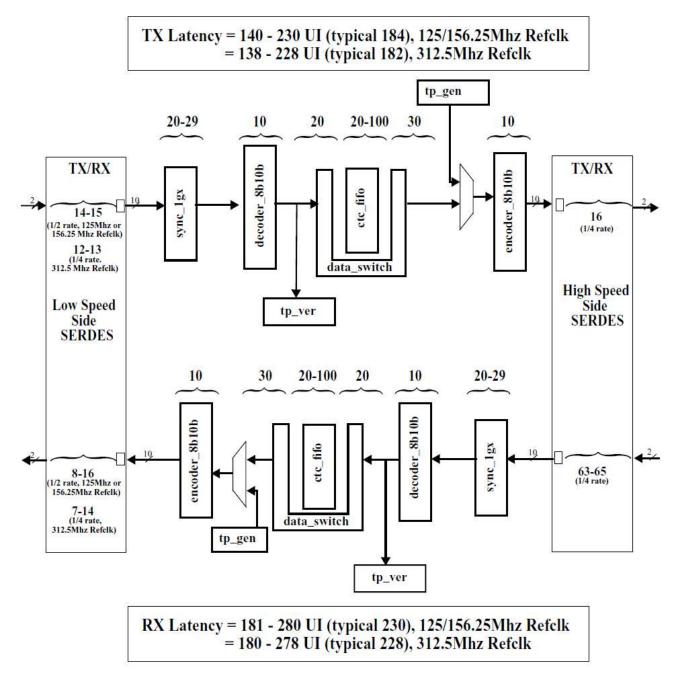

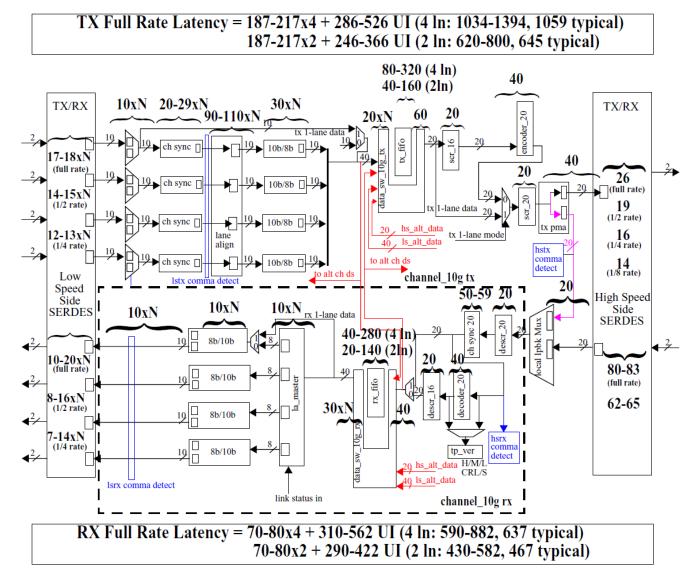

# 3.18 10GBASE-KR Latency

The latency through the TLK10232 in 10GBASE-KR mode is as shown in Figure 3-5. Note that the latency ranges shown indicate static rather than dynamic latency variance, i.e., the range of possible latencies when the serial link is initially established. During normal operation, the latency through the device is fixed.

TX, FEC bypassed, CTC depth 12: 1269-1569 UI (123ns - 152ns) NOTE: TX Latency numbers represent no external skew between lanes. External lane skew will increase overall latency

RX, FEC bypassed, CTC depth 12: 838-1203 UI (81ns - 117ns)

Figure 3-5. 10GBASE-KR Mode Latency Per Block

# 4 1GBASE-KX MODE FUNCTIONAL DESCRIPTION

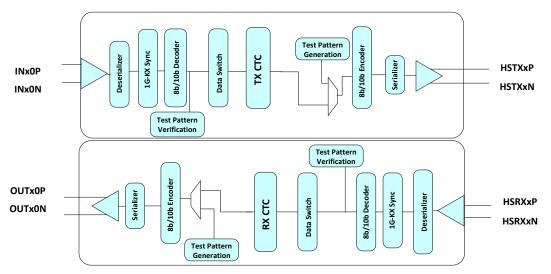

A simplified block diagram of the 1GBASE-KX data path is shown in Figure 4-1.

Figure 4-1. A Simplified One Channel Block Diagram of the 1GKX Data Path

#### 4.1 Channel Sync Block

This block is used to align the deserialized signals to the proper 10-bit word boundaries. The Channel Sync block generates a synchronization flag indicating incoming data is synchronized to the correct word boundary. This module implements the synchronization state machine found in Figure 36-9 of the IEEE 802.3-2008 Standard. A synchronization status signal, latched low, is available to indicate synchronization errors.

# 4.2 8b/10b Encoder and Decoder Blocks

As in the 10GBASE-KR operating mode, these blocks are used to convert between 10-bit (encoded) data and 8-bit data words. They can be optionally bypassed. A code invalid signal, latched low, is available to indicate 8b/10b encode and decode errors.

# 4.3 TX CTC

The transmit clock tolerance compensation (CTC) block acts as a FIFO with add and delete capabilities, adding and deleting 2 cycles each time to support ±200ppm during IFG (no errors) between the read and write clocks. This block implements a 12 deep asynchronous FIFO with a usable space 8 deep. It has two separate pointer tracking systems. One determines when to delete or insert and another determines when to reset. Inserts and deletes are only allowed during non-errored inter-frame gaps and occurs 2 cycles at a time. It has an auto reset feature once collision occurs. If a collision occurs, the indication is latched high until read by MDIO.

# 4.4 1GBASE-KX Line Rate, PLL Settings, and Reference Clock Selection

When the TLK10232 is configured to operate in the 1GBASE-KX mode, the available line rates, reference clock frequencies, and corresponding PLL multipliers are summarized in Table 4-1.

#### ZHCSB12-MAY 2013

# Table 4-1. Specific Line Rate and Reference Clock Selection for the 1GBASE-KX Mode

|                     | LOW SPEED                | SIDE    |                    | HIGH SPEED SIDE                     |                          |         |                    |  |  |

|---------------------|--------------------------|---------|--------------------|-------------------------------------|--------------------------|---------|--------------------|--|--|

| Line Rate<br>(Mbps) | SERDES PLL<br>Multiplier | Rate    | REFCLKP/N<br>(MHz) | Line Rate<br>(Mbps <sup>(1)</sup> ) | SERDES PLL<br>Multiplier | Rate    | REFCLKP/N<br>(MHz) |  |  |

| 3125 <sup>(2)</sup> | 10                       | Full    | 156.25             | 3125 <sup>(2)</sup>                 | 10                       | Full    | 156.25             |  |  |

| 3125 <sup>(2)</sup> | 5                        | Full    | 312.5              | 3125 <sup>(2)</sup>                 | 5                        | Full    | 312.5              |  |  |

| 1250                | 10                       | Half    | 125 <sup>(2)</sup> | 1250                                | 20                       | Quarter | 125 <sup>(2)</sup> |  |  |

| 1250                | 8                        | Half    | 156.25             | 1250                                | 16                       | Quarter | 156.25             |  |  |

| 1250                | 8                        | Quarter | 312.5              | 1250                                | 8                        | Quarter | 312.5              |  |  |

(1) High Speed Side SERDES runs at 2x effective data rate.

(2) Manual mode only, as auto negotiation does not support 125Mhz REFCLK or line rate of 3125Mbps. To disable automatic setting of PLL and rate modes, write 1'b1 to bit 13 of register 0x1E.001D.

# 4.5 Test Pattern Generator

In 1G-KX mode, this block can be used to generate test patterns allowing the 1G-KX channel to be tested for compliance while in a system environment or for diagnostic purposes. Test patterns generated are high/low/mixed frequency and CRPAT long or short.

# 4.6 Test Pattern Verifier

The 1G-KX test pattern verifier performs the verification and error reporting for the CRPAT Long and Short test patterns specified in Annex 36A of the IEEE 802.3-2008 standard. Errors are reported to MDIO registers.

# 4.7 1GBASE-KX Mode Latency

The latency through the TLK10232 in 1G-KX mode is as shown in Figure 4-2. Note that the latency ranges shown indicate static rather than dynamic latency variance, i.e., the range of possible latencies when the serial link is initially established. During normal operation, the latency through the device is fixed.

ZHCSB12-MAY 2013

Figure 4-2. 1G-KX Mode Latency

# 5 GENERAL PURPOSE (10G) SERDES MODE FUNCTIONAL DESCRIPTION

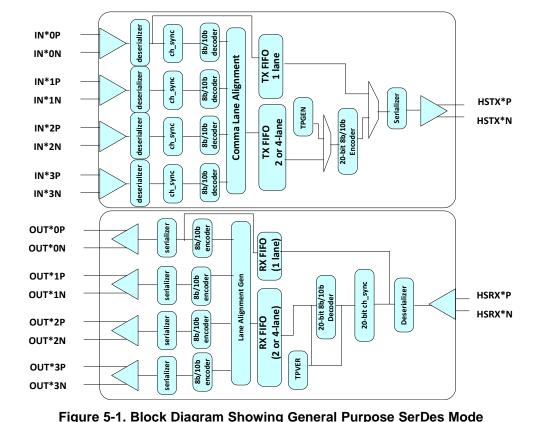

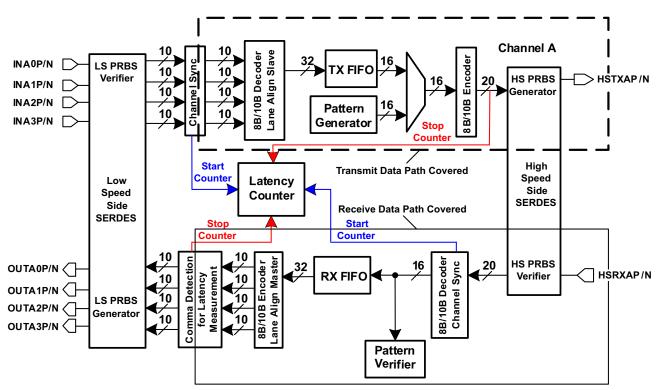

A block diagram showing the transmit and receive data paths of the TLK10232 operating in General Purpose (10G) SerDes mode is shown in Figure 5-1.

rigure 3-1. Diock Diagram Showing General 1 urpose Serbes mode

# 5.1 General Purpose SERDES Transmit Data Path

The TLK10232 General Purpose SERDES low speed to high speed (transmit) data path with the device configured to operate in the normal transceiver (mission) mode is shown in the upper half of Figure 5-1. In this mode, 8B/10B encoded serial data (IN\*P/N) in 2 or 4 lanes is received by the low speed side SERDES and deserialized into 10-bit parallel data for each lane. The data in each individual lane is then byte aligned (channel synchronized) and then 8B/10B decoded into 8-bit parallel data for each lane. The lane data is then lane aligned by the Lane Alignment Slave. 32 bits of lane aligned parallel data is input to a transmit FIFO which delivers it to an 8B/10B encoder, 16 data bits at a time. The resulting 20-bit 8B/10B encoded parallel data is sent to the high speed side SERDES for serialization and output through the HSTX\*P/N pins.

# 5.2 General Purpose SERDES Receive Data Path

With the device configured to operate in the normal transceiver (mission) mode, the high speed to low speed (receive) data path is shown in the lower half of Figure 5-1. 8B/10B encoded serial data (HSRX\*P/N) is received by the high speed side SERDES and deserialized into 20-bit parallel data. The data is then byte aligned, 8B/10B decoded into 16-bit parallel data, and then delivered to a receive FIFO. The receive FIFO in turn delivers 32-bit parallel data to the Lane Alignment Master which splits the data into the same number of lanes as configured on the transmit data path. The lane data is then 8B/10B encoded and the resulting 10-bit parallel data for each lane is input to the low speed side SERDES for serialization and output through the OUT\*P/N pins.

**EXAS**

#### 5.3 Channel Synchronization

As in the 10GBASE-KR mode, the channel synchronization block is used in the 10G General Purpose SERDES mode to align received serial data to a defined byte boundary. The channel synchronization block detects the comma pattern found in the K28.5 character, and follows the synchronization flowchart shown in Figure 3-2.

#### 5.4 8B/10B Encoder and Decoder

As in the 10GBASE-KR and 1GBASE-KX modes, the 8B/10B encoder and decoder blocks are used to convert between 10-bit (encoded) and 8-bit (unencoded) data words.

# 5.5 Lane Alignment Scheme for 8b/10b General Purpose Serdes Mode

Lower rate multi-lane serial signals per channel must be byte aligned and lane aligned such that high speed multiplexing (proper reconstruction of higher rate signal) is possible. For that reason, the TLK10232 implements a special lane alignment scheme on the low speed (LS) side for 8b/10b data that does not contain XAUI alignment characters.

During lane alignment, a proprietary pattern (or a custom comma compliant data stream) is sent by the LS transmitter to the LS receiver on each active lane. This pattern allows the LS receiver to both delineate byte boundaries within a lower speed lane and align bytes across the lanes (2 or 4) such that the original higher rate data ordering is restored.

Lane alignment completes successfully when the LS receiver asserts a "Link Status OK" signal monitored by the LS transmitter on the link partner device such as an FPGA. The TLK10232 sends out the "Link Status OK" signals through the LS\_OK\_OUT\_A/B output pins, and monitors the "Link Status OK" signals from the link partner device through the LS\_OK\_IN\_A/B input pins. If the link partner device does not need the TLK10232 Lane Alignment Master (LAM) to send proprietary lane alignment pattern, LS\_OK\_IN\_A/B can be tied high on the application board or set through MDIO register bits.

The lane alignment scheme is activated under any of the following conditions:

- Device/System power up (after configuration/provisioning)

- Loss of channel synchronization assertion on any enabled LS lane

- · Loss of signal assertion on any enabled LS lane

- LS SERDES PLL Lock indication deassertion

- After device configuration change

- After software determined LS 8B/10B decoder error rate threshold exceeded

- · After device reset is deasserted

- Any time the LS receiver deasserts "Link Status OK".

- Presence of reoccurring higher level / protocol framing errors

All the above conditions are selectable through MDIO register provisioning.

The block diagram of the lane alignment scheme is shown in Figure 5-2.

# TLK10232

ZHCSB12 - MAY 2013

Texas Instruments

www.ti.com.cn

Figure 5-2. Block Diagram of the Lane Alignment Scheme

# 5.6 Lane Alignment Components

- Lane Alignment Master (LAM)

- Responsible for generating proprietary LS lane alignment initialization pattern

- Resides in the TLK10232 receive path (one instance per channel)

- Responsible for bringing up LS receive link for the data sent from the TLK10232 to a link partner device

- Monitors the LS\_OK\_IN pins for "Link Status OK" signals sent from the Lane Alignment Slave (LAS) of the link partner device

- Resides in the link partner device (one instance per channel)

- Responsible for bringing up LS transmit link for the data sent from the link partner device to the TLK10232

- Monitors the "Link Status OK" signals sent from the LS\_OK\_OUT pins of the Lane Alignment Slave (LAS) of the TLK10232

- Lane Alignment Slave (LAS)

- Responsible for monitoring the LS lane alignment initialization pattern