## 1 TMS320DM6435 Digital Media Processor

#### 1.1 Features

- High-Performance Digital Media Processor (DM6435)

- 2.5-, 2.-, 1.67-,1.51-, 1.43-ns ns Instruction Cycle Time

- 400-, 500-, 600-, 660-, 700-MHz C64x+™ Clock Rate

- Eight 32-Bit C64x+ Instructions/Cycle

- 3200, 4000, 4800, 5280, 5600 MIPS

- Fully Software-Compatible With C64x

- Commercial and Automotive (Q or S suffix)

Grades

- Low Power Device (L suffix)

- VelociTI.2<sup>™</sup> Extensions to VelociTI<sup>™</sup>

Advanced Very-Long-Instruction-Word (VLIW)

TMS320C64x+<sup>™</sup> DSP Core

- Eight Highly Independent Functional Units With VelociTl.2 Extensions:

- Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle

- Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle

- Load-Store Architecture With Non-Aligned Support

- 64 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Additional C64x+™ Enhancements

- Protected Mode Operation

- Exceptions Support for Error Detection and Program Redirection

- Hardware Support for Modulo Loop Auto-Focus Module Operation

- C64x+ Instruction Set Features

- Byte-Addressable (8-/16-/32-/64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- Normalization, Saturation, Bit-Counting

- VelociTI.2 Increased Orthogonality

- C64x+ Extensions

- Compact 16-bit Instructions

- Additional Instructions to Support Complex Multiplies

- C64x+ L1/L2 Memory Architecture

- 256K-Bit (32K-Byte) L1P Program RAM/Cache [Flexible Allocation]

- 640K-Bit (80K-Byte) L1D Data RAM/Cache [Flexible Allocation]

- 1M-Bit (128K-Byte) L2 Unified Mapped RAM/Cache [Flexible Allocation]

- Supports Little Endian Mode Only

- Video Processing Subsystem (VPSS), VPFE Only

- Front End Provides:

- CCD and CMOS Imager Interface

- BT.601/BT.656 Digital YCbCr 4:2:2 (8-/16-Bit) Interface

- Preview Engine for Real-Time Image Processing

- Glueless Interface to Common Video Decoders

- Histogram Module

- Auto-Exposure, Auto-White Balance and Auto-Focus Module

- Resize Engine

- Resize Images From 1/4x to 4x

- Separate Horizontal/Vertical Control

- External Memory Interfaces (EMIFs)

- 32-Bit DDR2 SDRAM Memory Controller With 256M-Byte Address Space (1.8-V I/O)

- Supports up to 333-MHz (data rate) bus and interfaces to DDR2-400 SDRAM

- Asynchronous 8-Bit Wide EMIF (EMIFA)

With up to 64M-Byte Address Reach

- Flash Memory Interfaces

- NOR (8-Bit-Wide Data)

- NAND (8-Bit-Wide Data)

- Enhanced Direct-Memory-Access (EDMA)

Controller (64 Independent Channels)

- Two 64-Bit General-Purpose Timers (Each Configurable as Two 32-Bit Timers)

- One 64-Bit Watch Dog Timer

- Two UARTs (One with RTS and CTS Flow Control)

- Master/Slave Inter-Integrated Circuit (I<sup>2</sup>C Bus<sup>™</sup>)

- Multichannel Buffered Serial Port (McBSP)

- I2S and TDM

- AC97 Audio Codec Interface

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

All trademarks are the property of their respective owners.

- SP

- Standard Voice Codec Interface (AIC12)

- Telecom Interfaces ST-Bus, H-100

- 128 Channel Mode

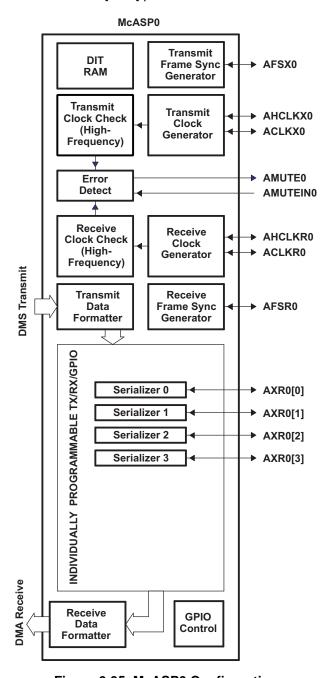

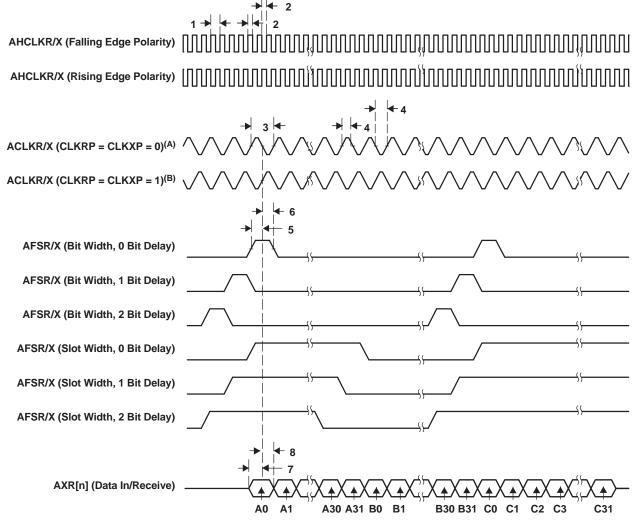

- Multichannel Audio Serial Port (McASP0)

- Four Serializers and SPDIF (DIT) Mode

- 16-Bit Host-Port Interface (HPI)

- High-End CAN Controller (HECC)

- 10/100 Mb/s Ethernet MAC (EMAC)

- IEEE 802.3 Compliant

- Supports Media Independent Interface (MII)

- Management Data I/O (MDIO) Module

- VLYNQ™ Interface (FPGA Interface)

- Three Pulse Width Modulator (PWM) Outputs

- On-Chip ROM Bootloader

- Individual Power-Savings Modes

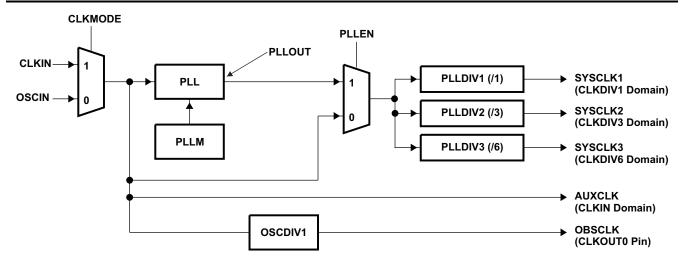

- Flexible PLL Clock Generators

- IEEE-1149.1 (JTAG™)

Boundary-Scan-Compatible

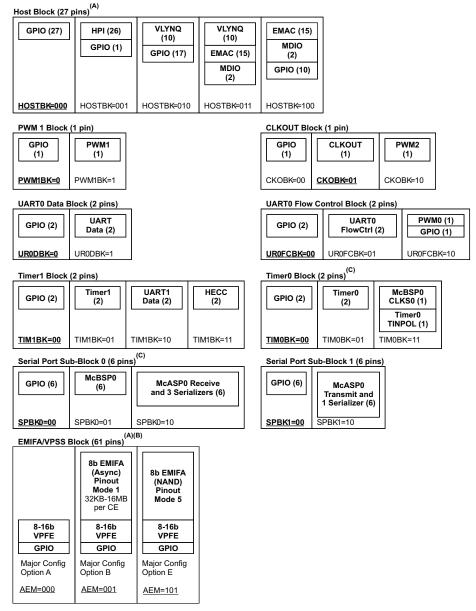

- Up to 111 General-Purpose I/O (GPIO) Pins (Multiplexed With Other Device Functions)

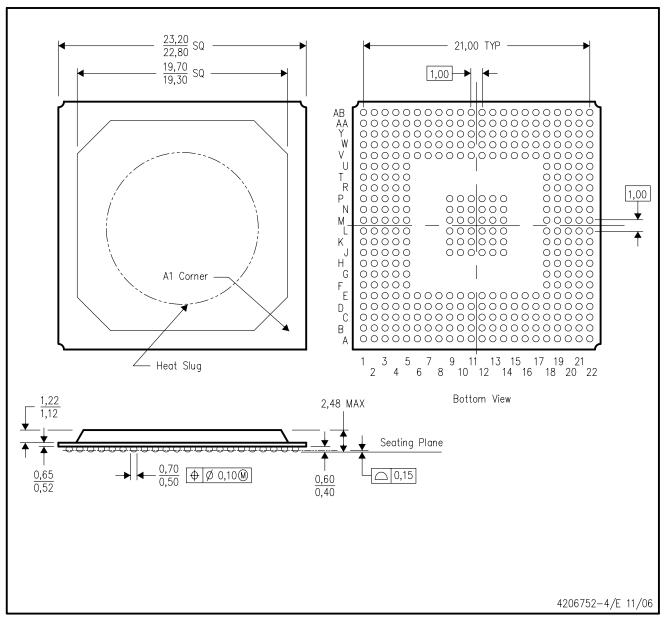

- Packages:

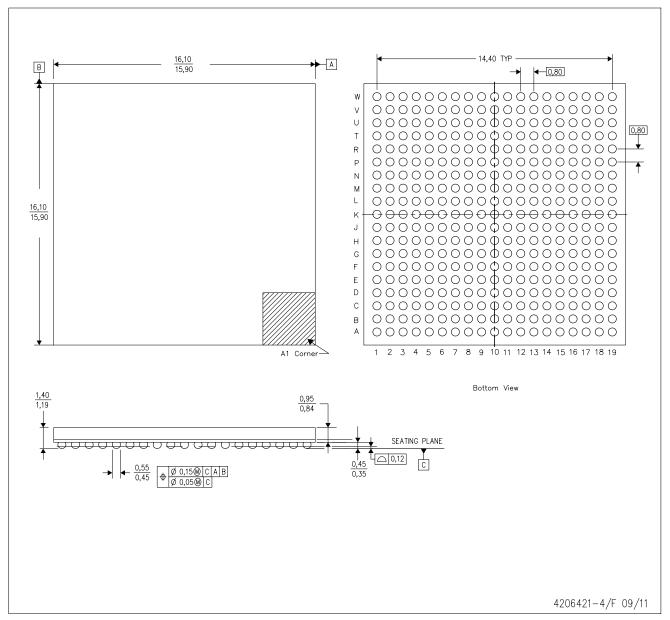

- 361-Pin Pb-Free PBGA Package (ZWT Suffix), 0.8-mm Ball Pitch

- 376-Pin Plastic BGA Package (ZDU Suffix), 1.0-mm Ball Pitch

- 0.09-μm/6-Level Cu Metal Process (CMOS)

- 3.3-V and 1.8-V I/O, 1.2-V Internal (-7/-6/-5/-4/-L/-Q6/-Q5/-Q4)

- 3.3-V and 1.8-V I/O, 1.05-V Internal (-7/-6/-5/-4/-L/-Q5)

- Applications:

- Digital Media

- Networked Media Encode

- Video Imaging

#### 1.2 Description

The TMS320C64x+™ DSPs (including the TMS320DM6435 device) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM6435 device is based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices.

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively.

With performance of up to 5600 million instructions per second (MIPS) at a clock rate of 700 MHz, the C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The eight functional units include instructions to accelerate the performance in video and imaging applications. The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2800 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 5600 MMACS. For more details on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732).

The DM6435 also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices. The DM6435 core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P) consists of a 256K-bit memory space that can be configured as mapped memory or direct mapped cache, and the Level 1 data (L1D) consists of a 640K-bit memory space —384K-bit of which is mapped memory and 256K-bit of which can be configured as mapped memory or 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 1M-bit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

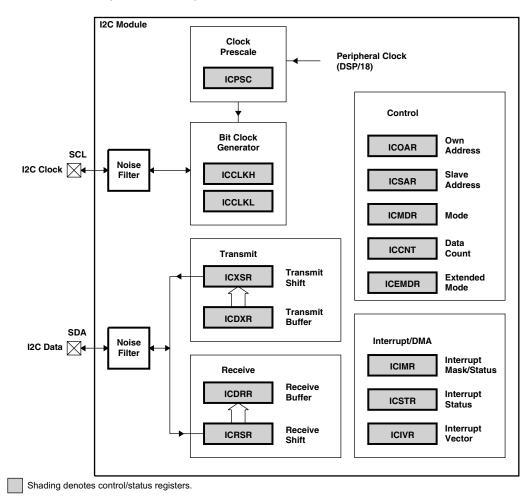

The peripheral set includes: a configurable video port (VPFE); a 10/100 Mb/s Ethernet MAC (EMAC) with a management data input/output (MDIO) module; a 4-bit transmit, 4-bit receive VLYNQ interface; an inter-integrated circuit (I2C) Bus interface; a multichannel buffered serial port (McBSP); a multichannel audio serial port (McASP0) with 4 serializers; 2 64-bit general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer; a user-configurable 16-bit host-port interface (HPI); up to 111-pins of general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed with other peripherals; 2 UARTs with hardware handshaking support on 1 UART; 3 pulse width modulator (PWM) peripherals; 1 high-end controller area network (CAN) controller [HECC]; and 2 glueless external memory interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a higher speed synchronous memory interface for DDR2.

The DM6435 device includes a Video Processing Subsystem (VPSS) with a configurable video/imaging front-end input peripheral used for video capture.

The Video Processing Front-End (VPFE) is comprised of a CCD Controller (CCDC), a Preview Engine (Previewer), Histogram Module, Auto-Exposure/White Balance/Focus Module (H3A), and Resizer. The CCDC is capable of interfacing to common video decoders, CMOS sensors, and Charge Coupled Devices (CCDs). The Previewer is a real-time image processing engine that takes raw imager data from a CMOS sensor or CCD and converts from an RGB Bayer Pattern to YUV422. The Histogram and H3A modules provide statistical information on the raw color data for use by the DM6435. The Resizer accepts image data for separate horizontal and vertical resizing from 1/4x to 4x in increments of 256/N, where N is between 64 and 1024.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6435 and the network. The DM6435 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS) support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system.

The I2C and VLYNQ ports allow DM6435 to easily control peripheral devices and/or communicate with host processors.

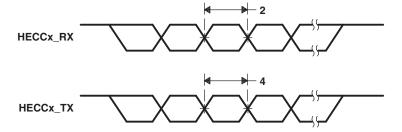

The high-end controller area network (CAN) controller [HECC] module provides a network protocol in a harsh environment to communicate serially with other controllers, typically in automotive applications.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections later in this document and the associated peripheral reference guides.

The DM6435 has a complete set of development tools. These include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows<sup>™</sup> debugger interface for visibility into source code execution.

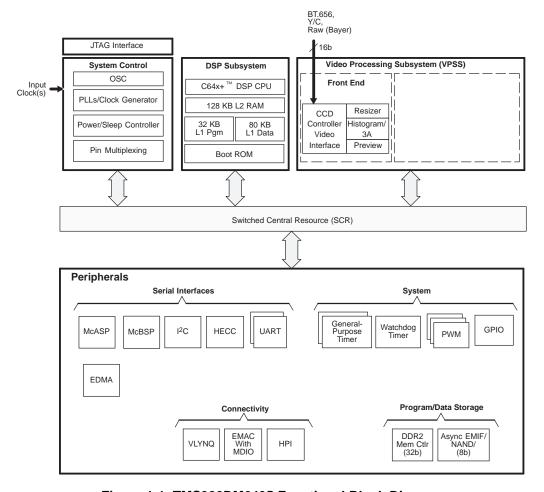

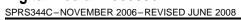

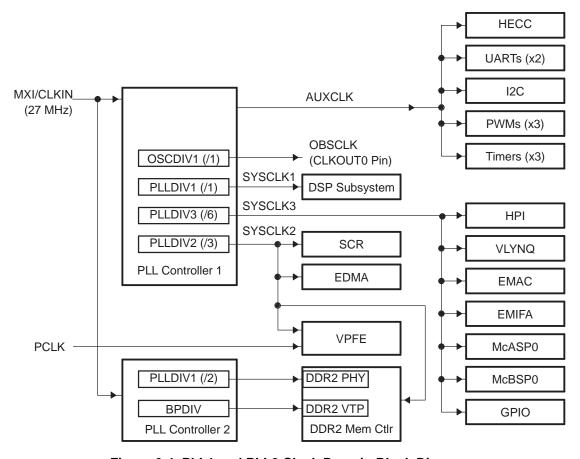

## 1.3 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the DM6435 device.

Figure 1-1. TMS320DM6435 Functional Block Diagram

#### www.ti.com

# **Contents**

| 1   | TMS   | 320DM6435 Digital Media Processor 1            |   |              | Temperature (Unless Otherwise Noted)               | 127        |

|-----|-------|------------------------------------------------|---|--------------|----------------------------------------------------|------------|

|     | 1.1   | Features 1                                     | 6 | Perip        | heral Information and Electrical                   |            |

|     | 1.2   | Description 2                                  |   | Spec         | ifications                                         | 129        |

|     | 1.3   | Functional Block Diagram 4                     |   | 6.1          | Parameter Information                              | 129        |

| Rev | ision | History <u>6</u>                               |   | 6.2          | Recommended Clock and Control Signal Transition    |            |

| 2   |       | ce Overview 7                                  |   |              | Behavior                                           |            |

|     | 2.1   | Device Characteristics                         |   | 6.3          | Power Supplies                                     | <u>130</u> |

|     | 2.2   | CPU (DSP Core) Description8                    |   | 6.4          | Enhanced Direct Memory Access (EDMA3) Controller   | 137        |

|     | 2.3   | C64x+ CPU                                      |   | 6.5          | Reset                                              |            |

|     | 2.4   | Memory Map Summary 12                          |   | 6.6          | External Clock Input From MXI/CLKIN Pin            |            |

|     | 2.5   | Pin Assignments 16                             |   | 6.7          | Clock PLLs                                         |            |

|     | 2.6   | Terminal Functions                             |   | 6.8          |                                                    |            |

|     | 2.7   | Device Support                                 |   |              | Interrupts (FMIF)                                  |            |

|     | 2.8   | Device and Development-Support Tool            |   | 6.9          | External Memory Interface (EMIF)                   |            |

|     |       | Nomenclature <u>58</u>                         |   | 6.10<br>6.11 | Video Processing Sub-System (VPSS) Overview .      | 173        |

|     | 2.9   | Documentation Support                          |   | 0.11         | Universal Asynchronous Receiver/Transmitter (UART) | 187        |

| 3   | Devi  | ce Configuration <u>61</u>                     |   | 6.12         | Inter-Integrated Circuit (I2C)                     |            |

|     | 3.1   | System Module Registers                        |   | 6.13         | Host-Port Interface (HPI) Peripheral               |            |

|     | 3.2   | Power Considerations <u>62</u>                 |   | 6.14         | Multichannel Buffered Serial Port (McBSP)          |            |

|     | 3.3   | Clock Considerations                           |   | 6.15         | Multichannel Audio Serial Port (McASP0)            | 100        |

|     | 3.4   | Boot Sequence <u>67</u>                        |   | 01.0         | Peripheral                                         | 208        |

|     | 3.5   | Configurations At Reset                        |   | 6.16         | High-End Controller Area Network Controller        |            |

|     | 3.6   | Configurations After Reset                     |   |              | (HECC)                                             | 216        |

|     | 3.7   | Multiplexed Pin Configurations                 |   | 6.17         | Ethernet Media Access Controller (EMAC)            | 222        |

|     | 3.8   | Device Initialization Sequence After Reset 119 |   | 6.18         | Management Data Input/Output (MDIO)                | 229        |

|     | 3.9   | Debugging Considerations                       |   | 6.19         | Timers                                             | <u>230</u> |

| 4   | Svst  | em Interconnect 123                            |   | 6.20         | Pulse Width Modulator (PWM)                        | 233        |

|     | 4.1   | System Interconnect Block Diagram 123          |   | 6.21         | VLYNQ                                              | 235        |

| 5   | Devi  | ce Operating Conditions                        |   | 6.22         | General-Purpose Input/Output (GPIO)                | 239        |

| -   | 5.1   | Absolute Maximum Ratings Over Operating        |   | 6.23         | IEEE 1149.1 JTAG                                   | 243        |

|     |       | Temperature Range (Unless Otherwise Noted) 125 | 7 | Mech         | nanical Data                                       | 245        |

|     | 5.2   | Recommended Operating Conditions <u>126</u>    |   | 7.1          | Thermal Data for ZWT                               | 24         |

|     | 5.3   | Electrical Characteristics Over Recommended    |   | 7.1.1        | Thermal Data for ZDU                               | 246        |

|     |       | Ranges of Supply Voltage and Operating         |   | 7.1.2        | Packaging Information                              | 246        |

#### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

This data manual revision history highlights the technical changes made to the SPRS344B device-specific data manual to make it an SPRS344C revision.

This data manual revision history highlights the technical changes made to the SPRS344B device-specific data manual to make it an SPRS344C revision.

**Scope**: Applicable updates to the TMS320DM643x DMP, specifically relating to the TMS320DM6435 device, have been incorporated.

- Added 660- and 700-MHz C64x+<sup>™</sup> device speeds.

- Added designators for low-power (-L) devices.

| SEE           | ADDITIONS/MODIFICATIONS/DELETIONS                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global        | <ul> <li>Updated/Changed signal name from "C_WE" to "C_WE"</li> <li>Updated/Changed signal name from "C_WEN" to "C_WE"</li> </ul>                                                                                                                                                                                                                                                                      |

| Section 1.1   | Added "5280, 5600 MIPS" to "High-Performance Digital Signal Processor (DM6435)" bullet                                                                                                                                                                                                                                                                                                                 |

| Section 1.2   | In first paragraph, updated/changed the following:     First sentence <i>from</i> "With performance up to 4800 million instructions per second (MIPS) at a clock rate of 600 MHz" <i>to</i> "With performance up to 5600 million instructions per second (MIPS) with a clock rate of 700 MHz"      Fifth sentence <i>from</i> "The DSP core can producefor a total of 2400 million MACs per secondor a |

|               | total of 4800 MMACS." to "The DSP core can producefor a total of 2800 million MACs per secondor a total of 5600 MMACS."                                                                                                                                                                                                                                                                                |

| Section 2.6   | Table 2-19, Multichannel Audio Serial Port (McASP0) Terminal Functions:  Updated/Changed AFSR0/DR0/GP[100] pin description from " frame synchronization AFSX0" to "frame synchronization AFSR0"                                                                                                                                                                                                        |

|               | <ul> <li>Updated/Changed AFSX0/DX1/GP[107] pin description from "frame synchronization AFSR0" to "frame synchronization AFSX0"</li> </ul>                                                                                                                                                                                                                                                              |

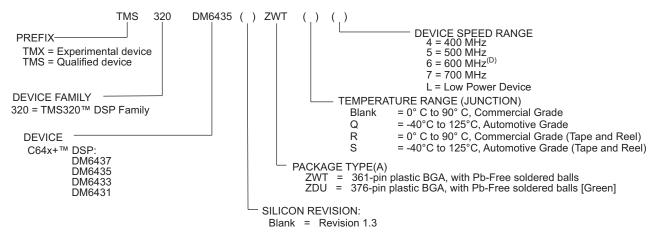

| Section 2.8   | Updated/Changed Figure 2-10, <i>Device Nomenclature</i> , to reflect new device speeds and low-power designator (-L suffix).                                                                                                                                                                                                                                                                           |

| Section 5     | Added footnote <b>to</b> Section 5.1, Absolute Maximum Ratings Over Operating Temperature Range (Unless Otherwise Noted).                                                                                                                                                                                                                                                                              |

| Section 5     | Updated/Changed I <sub>CDD</sub> and I <sub>DDD</sub> test conditions and footnote in Section 5.3, Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Temperature (Unless Otherwise Noted).                                                                                                                                                                            |

| Section 5.2   | Deleted "Future variants" footnote from table                                                                                                                                                                                                                                                                                                                                                          |

| Section 6.7.1 | Table 6-15, PLLC1 Clock Frequency Ranges:  • Updated/Changed PLLOUT 1.2V-CV <sub>DD</sub> max value <b>from</b> "700 MHz" <b>to</b> "600 MHz" for                                                                                                                                                                                                                                                      |

|               | -6/-5/-4/-L/-Q6/-Q5/-Q4 devices.  • Updated/Changed SYSCLK1 1.05V-CV <sub>DD</sub> max value <i>from</i> "560 MHz" <i>to</i> "520 MHz" for -7 devices.                                                                                                                                                                                                                                                 |

| Section 6.7.1 | Updated/Changed sentence <i>from</i> "TI requires EMI filter manufacturer Murata" <i>to</i> "TI recommends EMI filter manufacturer Murata"                                                                                                                                                                                                                                                             |

| Section 6.7.4 | Deleted "(-4, -4Q, -4S, -5, -5Q, -5S, -6)" from Table 6-19 title, Timing Requirements for MXI/CLKIN.                                                                                                                                                                                                                                                                                                   |

Revision History Submit Documentation Feedback

#### 2 Device Overview

#### 2.1 Device Characteristics

Table 2-1, provides an overview of the TMS320DM6435 DSP. The tables show significant features of the DM6435 device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type with pin count.

Table 2-1. Characteristics of the DM6435 Processor

|                                 | HARDWARE FEATURES                                                      | DM6435                                                                                                                                                                   |  |  |  |

|---------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                 | DDR2 Memory Controller                                                 | (16-/32-bit bus width) [1.8 V I/O]                                                                                                                                       |  |  |  |

|                                 | Asynchronous EMIF [EMIFA]                                              | Asynchronous (8-bit bus width), RAM, Flash, (8-bit NOR <i>or</i> 8-bit NAND)                                                                                             |  |  |  |

|                                 | EDMA3                                                                  | 1 (64 independent channels, 8 QDMA channels)                                                                                                                             |  |  |  |

|                                 | Timers                                                                 | 2 64-bit General Purpose<br>(configurable as 2 64-bit <b>or</b> 4 32-bit)<br>1 64-bit Watch Dog                                                                          |  |  |  |

| Parinharals                     | UARTs                                                                  | 2 (one with RTS and CTS flow control)                                                                                                                                    |  |  |  |

|                                 | I2C                                                                    | 1 (Master/Slave)                                                                                                                                                         |  |  |  |

| are available at the same       | McBSP                                                                  | 1                                                                                                                                                                        |  |  |  |

| time (For more detail, see      | McASP                                                                  | 1 (4 serailizers)                                                                                                                                                        |  |  |  |

| section).                       | 10/100 Ethernet MAC (EMAC) with<br>Management Data Input/Output (MDIO) | 1                                                                                                                                                                        |  |  |  |

| Asynchronous EMIF [EMIFA]   RA  | 1                                                                      |                                                                                                                                                                          |  |  |  |

|                                 | General-Purpose Input/Output Port (GPIO)                               | Up to 111 pins                                                                                                                                                           |  |  |  |

|                                 | PWM                                                                    | 3 outputs                                                                                                                                                                |  |  |  |

|                                 | HPI (16-bit)                                                           | 1                                                                                                                                                                        |  |  |  |

|                                 | Configurable Video Port                                                | 1 Input (VPFE)                                                                                                                                                           |  |  |  |

|                                 | HECC                                                                   | 1                                                                                                                                                                        |  |  |  |

|                                 | Size (Bytes)                                                           | 240KB RAM, 64KB ROM                                                                                                                                                      |  |  |  |

| On-Chip Memory                  | Organization                                                           | 32K-Byte (32KB) L1 Program (L1P) RAM/Cache (Cache up to 32KB)<br>80KB L1 Data (L1D) RAM/Cache (Cache up to 32KB)<br>128KB Unified Mapped RAM/Cache (L2)<br>64KB Boot ROM |  |  |  |

| MegaModule Rev ID               |                                                                        | See the TMS320DM6437/35/33/31 Digital Media<br>Processor (DMP) [Silicon Revisions 1.1 and 1.0]                                                                           |  |  |  |

| CPU ID + CPU Rev ID             | Control Status Register (CSR.[31:16])                                  | Silicon Errata (literature number SPRZ250).                                                                                                                              |  |  |  |

| JTAG BSDL_ID                    |                                                                        | See Section 6.23.1, JTAG ID (JTAGID) Register<br>Description(s)                                                                                                          |  |  |  |

| CPU Frequency <sup>(1)(2)</sup> | MHz                                                                    | 700 (-7)<br>660 (-Q6)<br>600 (-6/-L)<br>500 (-5/-Q5)<br>400 (-4/-Q4)                                                                                                     |  |  |  |

| Cycle Time <sup>(1)(2)</sup>    | ns                                                                     | 2.5 ns (-4/-Q4)<br>2 ns (-5/-Q5)<br>1.67 ns (-6/-L)<br>1.51 ns (-Q6)<br>1.43 ns (-7)                                                                                     |  |  |  |

<sup>(1)</sup> Performance numbers assume core voltage is set to 1.2V.

<sup>(2)</sup> Applies to "tape and reel" part number counterparts as well. For more information, see Section 2.8, Device and Development-Support Tool Nomenclature.

|                                   | HARDWARE FEATURES                                                       | DM6435                                  |  |  |

|-----------------------------------|-------------------------------------------------------------------------|-----------------------------------------|--|--|

|                                   | Coro (V)                                                                | 1.2 V<br>(-7/ -6/-5/ -4/-L/-Q6/-Q5/-Q4) |  |  |

| BGA Package(s) Process Technology | Core (V)                                                                | 1.05 V<br>(-7/-6/-5/-4/-L/-Q5)          |  |  |

|                                   | I/O (V)                                                                 | 1.8 V, 3.3 V                            |  |  |

| PLL Options                       | MXI/CLKIN frequency multiplier<br>(27 MHz reference)                    | x1 (Bypass), x14 to x 30                |  |  |

| DCA Deales as (a)                 | 16 x 16 mm, 0.8 mm pitch                                                | 361-Pin BGA (ZWT)                       |  |  |

| BGA Package(s)                    | 23 x 23 mm, 1.0 mm pitch                                                | 376-Pin BGA (ZDU)                       |  |  |

| Process Technology                | μm                                                                      | 0.09 μm                                 |  |  |

| Product Status <sup>(3)</sup>     | Product Preview (PP), Advance Information (AI), or Production Data (PD) | PD                                      |  |  |

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

### 2.2 CPU (DSP Core) Description

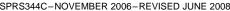

The C64x+ Central Processing Unit (CPU) consists of eight functional units, two register files, and two data paths as shown in Figure 2-1. The two general-purpose register files (A and B) each contain 32 32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be data address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit data, 40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are stored in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or 32 MSBs in the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from memory to the register file and store results from the register file into memory.

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x 32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four 16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The 32 x 32 bit multiply instructions provide the extended precision necessary for audio and other high-precision algorithms on a variety of signed and unsigned 32-bit data types.

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2 comparisons were only available on the .L units. On the C64x+ core they are also available on the .S unit which increases the performance of algorithms that do searching and sorting. Finally, to increase data packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack instructions return parallel results to output precision including saturation support.

Other new features include:

- SPLOOP A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

- Compact Instructions The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

- Instruction Set Enhancement As noted above, there are new instructions such as 32-bit multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field multiplication.

- Exceptions Handling Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and from system events (such as a watchdog time expiration).

- Privilege Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

- Time-Stamp Counter Primarily targeted for Real-Time Operating System (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following documents:

- TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732)

- TMS320C64x+ DSP Megamodule Reference Guide (literature number SPRU871)

- TMS320C64x to TMS320C64x+ CPU Migration Guide Application Report (literature number SPRAA84)

- TMS320C64x+ DSP Cache User's Guide (literature number SPRU862)

- A. On .M unit, dst2 is 32 MSB.

- B. On .M unit, dst1 is 32 LSB.

- On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

- D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

Figure 2-1. TMS320C64x+™ CPU (DSP Core) Data Paths

#### 2.3 C64x+ CPU

The C64x+ core uses a two-level cache-based architecture. The Level 1 Program memory/cache (L1P) consists of 32 KB memory space that can be configured as mapped memory or direct mapped cache. The Level 1 Data memory/cache (L1D) consists of 80 KB—48 KB of which is mapped memory and 32 KB of which can be configured as mapped memory or 2-way set associated cache. The Level 2 memory/cache (L2) consists of a 128 KB memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or a combination of both.

Table 2-2 shows a memory map of the C64x+ CPU cache registers for the device.

Table 2-2. C64x+ Cache Registers

| Table 2-2. C04x+ Cache Registers |                  |                                                |  |  |  |  |  |  |  |

|----------------------------------|------------------|------------------------------------------------|--|--|--|--|--|--|--|

| HEX ADDRESS RANGE                | REGISTER ACRONYM | DESCRIPTION                                    |  |  |  |  |  |  |  |

| 0x0184 0000                      | L2CFG            | L2 Cache configuration register                |  |  |  |  |  |  |  |

| 0x0184 0020                      | L1PCFG           | L1P Size Cache configuration register          |  |  |  |  |  |  |  |

| 0x0184 0024                      | L1PCC            | L1P Freeze Mode Cache configuration register   |  |  |  |  |  |  |  |

| 0x0184 0040                      | L1DCFG           | L1D Size Cache configuration register          |  |  |  |  |  |  |  |

| 0x0184 0044                      | L1DCC            | L1D Freeze Mode Cache configuration register   |  |  |  |  |  |  |  |

| 0x0184 0048 - 0x0184 0FFC        | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 1000                      | EDMAWEIGHT       | L2 EDMA access control register                |  |  |  |  |  |  |  |

| 0x0184 1004 - 0x0184 1FFC        | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 2000                      | L2ALLOC0         | L2 allocation register 0                       |  |  |  |  |  |  |  |

| 0x0184 2004                      | L2ALLOC1         | L2 allocation register 1                       |  |  |  |  |  |  |  |

| 0x0184 2008                      | L2ALLOC2         | L2 allocation register 2                       |  |  |  |  |  |  |  |

| 0x0184 200C                      | L2ALLOC3         | L2 allocation register 3                       |  |  |  |  |  |  |  |

| 0x0184 2010 - 0x0184 3FFF        | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 4000                      | L2WBAR           | L2 writeback base address register             |  |  |  |  |  |  |  |

| 0x0184 4004                      | L2WWC            | L2 writeback word count register               |  |  |  |  |  |  |  |

| 0x0184 4010                      | L2WIBAR          | L2 writeback invalidate base address register  |  |  |  |  |  |  |  |

| 0x0184 4014                      | L2WIWC           | L2 writeback invalidate word count register    |  |  |  |  |  |  |  |

| 0x0184 4018                      | L2IBAR           | L2 invalidate base address register            |  |  |  |  |  |  |  |

| 0x0184 401C                      | L2IWC            | L2 invalidate word count register              |  |  |  |  |  |  |  |

| 0x0184 4020                      | L1PIBAR          | L1P invalidate base address register           |  |  |  |  |  |  |  |

| 0x0184 4024                      | L1PIWC           | L1P invalidate word count register             |  |  |  |  |  |  |  |

| 0x0184 4030                      | L1DWIBAR         | L1D writeback invalidate base address register |  |  |  |  |  |  |  |

| 0x0184 4034                      | L1DWIWC          | L1D writeback invalidate word count register   |  |  |  |  |  |  |  |

| 0x0184 4038                      | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 4040                      | L1DWBAR          | L1D Block Writeback                            |  |  |  |  |  |  |  |

| 0x0184 4044                      | L1DWWC           | L1D Block Writeback                            |  |  |  |  |  |  |  |

| 0x0184 4048                      | L1DIBAR          | L1D invalidate base address register           |  |  |  |  |  |  |  |

| 0x0184 404C                      | L1DIWC           | L1D invalidate word count register             |  |  |  |  |  |  |  |

| 0x0184 4050 - 0x0184 4FFF        | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 5000                      | L2WB             | L2 writeback all register                      |  |  |  |  |  |  |  |

| 0x0184 5004                      | L2WBINV          | L2 writeback invalidate all register           |  |  |  |  |  |  |  |

| 0x0184 5008                      | L2INV            | L2 Global Invalidate without writeback         |  |  |  |  |  |  |  |

| 0x0184 500C - 0x0184 5027        | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 5028                      | L1PINV           | L1P Global Invalidate                          |  |  |  |  |  |  |  |

| 0x0184 502C - 0x0184 5039        | -                | Reserved                                       |  |  |  |  |  |  |  |

| 0x0184 5040                      | L1DWB            | L1D Global Writeback                           |  |  |  |  |  |  |  |

| 0x0184 5044                      | L1DWBINV         | L1D Global Writeback with Invalidate           |  |  |  |  |  |  |  |

| 0x0184 5048                      | L1DINV           | L1D Global Invalidate without writeback        |  |  |  |  |  |  |  |

## Table 2-2. C64x+ Cache Registers (continued)

| HEX ADDRESS RANGE         | REGISTER ACRONYM | DESCRIPTION                                                                                  |

|---------------------------|------------------|----------------------------------------------------------------------------------------------|

| 0x0184 8000 - 0x0184 80BC | MAR0 - MAR47     | Reserved (corresponds to byte address 0x0000 0000 - 0x2FFF FFFF)                             |

| 0x0184 80C0 - 0x0184 80FC | MAR48 - MAR63    | Reserved (corresponds to byte address 0x3000 0000 - 0x3FFF FFFF)                             |

| 0x0184 8100 - 0x0184 8104 | MAR64 - MAR65    | Reserved (corresponds to byte address 0x4000 0000 - 0x41FF FFFF)                             |

| 0x0184 8108 - 0x0184 8124 | MAR66 - MAR73    | Memory Attribute Registers for EMIFA (corresponds to byte address 0x4200 0000 - 0x49FF FFFF) |

| 0x0184 8128 - 0x0184 812C | MAR74 - MAR75    | Reserved (corresponds to byte address 0x4A00 0000 - 0x4BFF FFFF)                             |

| 0x0184 8130 - 0x0184 813C | MAR76 - MAR79    | Memory Attribute Registers for VLYNQ (corresponds to byte address 0x4C00 0000 - 0x4FFF FFFF) |

| 0x0184 8140- 0x0184 81FC  | MAR80 - MAR127   | Reserved (corresponds to byte address 0x5000 0000 - 0x7FFF FFFF)                             |

| 0x0184 8200 - 0x0184 823C | MAR128 - MAR143  | Memory Attribute Registers for DDR2 (corresponds to byte address 0x8000 0000 - 0x8FFF FFFF)  |

| 0x0184 8240 - 0x0184 83FC | MAR144 - MAR255  | Reserved (corresponds to byte address 0x9000 0000 - 0xFFFF FFFF)                             |

## 2.4 Memory Map Summary

Table 2-3 shows the memory map address ranges of the device. Table 2-4 depicts the expanded map of the Configuration Space (0x0180 0000 through 0x0FFF FFFF). The device has multiple on-chip memories associated with its two processors and various subsystems. To help simplify software development a unified memory map is used where possible to maintain a consistent view of device resources across all bus masters.

### **Table 2-3. Memory Map Summary**

| START<br>ADDRESS | END<br>ADDRESS | SIZE<br>(Bytes) | C64x+<br>MEMORY MAP          | EDMA PERIPHERAL<br>MEMORY MAP | VPSS<br>MEMORY MAP     |

|------------------|----------------|-----------------|------------------------------|-------------------------------|------------------------|

| 0x0000 0000      | 0x000F FFFF    | 1M              | Reserved                     |                               |                        |

| 0x0010 0000      | 0x0010 FFFF    | 64K             | Boot ROM                     |                               |                        |

| 0x0011 0000      | 0x007F FFFF    | 7M-64K          | Reserved                     |                               |                        |

| 0x0080 0000      | 0x0081 FFFF    | 128K            | L2 RAM/Cache <sup>(1)</sup>  |                               |                        |

| 0x0082 0000      | 0x00E0 7FFF    | 6048K           | Reserved                     |                               |                        |

| 0x00E0 8000      | 0x00E0 FFFF    | 32K             | L1P RAM/Cache <sup>(1)</sup> | Reserved                      |                        |

| 0x00E1 0000      | 0x00F0 3FFF    | 976K            | Reserved                     |                               |                        |

| 0x00F0 4000      | 0x00F0 FFFF    | 48K             | L1D RAM                      |                               |                        |

| 0x00F1 0000      | 0x00F1 7FFF    | 32K             | L1D RAM/Cache <sup>(1)</sup> |                               |                        |

| 0x00F1 8000      | 0x017F FFFF    | 9120K           | Reserved                     |                               |                        |

| 0x0180 0000      | 0x01BF FFFF    | 4M              | CFG Space                    |                               |                        |

| 0x01C0 0000      | 0x01FF FFFF    | 4M              | CFG Bus Peripherals          | CFG Bus Peripherals           |                        |

| 0x0200 0000      | 0x100F FFFF    | 225M            | Reserved                     |                               |                        |

| 0x1010 0000      | 0x1010 FFFF    | 64K             | Boot ROM                     | Reserved                      |                        |

| 0x1011 0000      | 0x107F FFFF    | 7M-48K          | Reserved                     |                               |                        |

| 0x1080 0000      | 0x1081 FFFF    | 128K            | L2 RAM/Cache <sup>(1)</sup>  | L2 RAM/Cache <sup>(1)</sup>   |                        |

| 0x1082 0000      | 0x10E0 7FFF    | 6048K           | Reserved                     | Reserved                      |                        |

| 0x10E0 8000      | 0x10E0 FFFF    | 32K             | L1P RAM/Cache <sup>(1)</sup> | L1P RAM/Cache <sup>(1)</sup>  |                        |

| 0x10E1 0000      | 0x10F0 3FFF    | 976K            | Reserved                     | Reserved                      | <b>_</b>               |

| 0x10F0 4000      | 0x10F0 FFFF    | 48K             | L1D RAM                      | L1D RAM                       | Reserved               |

| 0x10F1 0000      | 0x10F1 7FFF    | 32K             | L1D RAM/Cache <sup>(1)</sup> | L1D RAM/Cache <sup>(1)</sup>  |                        |

| 0x10F1 8000      | 0x10FF FFFF    | 1M-96K          | Reserved                     | Reserved                      |                        |

| 0x1100 0000      | 0x1FFF FFFF    | 240M            | Reserved                     | Reserved                      |                        |

| 0x2000 0000      | 0x2000 7FFF    | 32K             | DDR2 Control Regs            | DDR2 Control Regs             |                        |

| 0x2000 8000      | 0x2FFF FFFF    | 256M-32K        | Reserved                     | Reserved                      |                        |

| 0x3000 0000      | 0x3FFF FFFF    | 256M            | Reserved                     | Reserved                      |                        |

| 0x4000 0000      | 0x41FF FFFF    | 32M             | Reserved                     | Reserved                      |                        |

| 0x4200 0000      | 0x42FF FFFF    | 16M             | EMIFA Data (CS2)(2)          | EMIFA Data (CS2)(2)           |                        |

| 0x4300 0000      | 0x43FF FFFF    | 16M             | Reserved                     | Reserved                      |                        |

| 0x4400 0000      | 0x44FF FFFF    | 16M             | EMIFA Data (CS3)(2)          | EMIFA Data (CS3)(2)           |                        |

| 0x4500 0000      | 0x45FF FFFF    | 16M             | Reserved                     | Reserved                      |                        |

| 0x4600 0000      | 0x46FF FFFF    | 16M             | EMIFA Data (CS4)(2)          | EMIFA Data (CS4)(2)           |                        |

| 0x4700 0000      | 0x47FF FFFF    | 16M             | Reserved                     | Reserved                      |                        |

| 0x4800 0000      | 0x48FF FFFF    | 16M             | EMIFA Data (CS5)(2)          | EMIFA Data (CS5)(2)           |                        |

| 0x4900 0000      | 0x49FF FFFF    | 16M             | Reserved                     | Reserved                      |                        |

| 0x4A00 0000      | 0x4BFF FFFF    | 32M             | Reserved                     | Reserved                      |                        |

| 0x4C00 0000      | 0x4FFF FFFF    | 64M             | VLYNQ (Remote Data)          | VLYNQ (Remote Data)           |                        |

| 0x5000 0000      | 0x7FFF FFFF    | 768M            | Reserved                     | Reserved                      |                        |

| 0x8000 0000      | 0x8FFF FFFF    | 256M            | DDR2 Memory Controller       | DDR2 Memory Controller        | DDR2 Memory Controller |

|                  | 1              | 1               | <u> </u>                     |                               | 1                      |

For all bootmodes that default to DSPBOOTADDR = 0x0010 0000 (i.e., all boot modes except the EMIFA ROM Direct Boot, BOOTMODE[3:0] = 0100, FASTBOOT = 0), the bootloader code disables all C64x+ cache (L2, L1P, and L1D) so that upon exit from the bootloader code, all C64x+ memories are configured as all RAM (L2CFG.L2MODE = 0h, L1PCFG.L1PMODE = 0h, and L1DCFG.L1DMODE = 0h). If cache use is required, the application code must explicitly enable the cache. For more information on boot modes, see Section 3.4.1, Boot Modes. For more information on the bootloader, see the Using the TMS320DM643x Bootloader Application Report (literature number SPRAAGO). For the EMIFA ROM Direct Boot (BOOTMODE[3:0] = 0100, FASTBOOT = 0), the bootloader is not executed—that is, L2 RAM/Cache defaults to all RAM (L2CFG.L2MODE = 0h); L1P RAM/Cache defaults to all cache (L1PCFG.L1PMODE = 7h); and L1D RAM/Cache defaults to all cache (L1DCFG.L1DMODE = 7h).

The EMIFA CS0 and CS1 are *not* functionally supported on the DM6435 device, and therefore, are *not* pinned out.

### **Table 2-4. Configuration Memory Map Summary**

| Table 2-4. Configuration Memory Map Summary |                |                 |                               |  |  |  |  |  |  |

|---------------------------------------------|----------------|-----------------|-------------------------------|--|--|--|--|--|--|

| START<br>ADDRESS                            | END<br>ADDRESS | SIZE<br>(Bytes) | C64x+                         |  |  |  |  |  |  |

| 0x0180 0000                                 | 0x0180 FFFF    | 64K             | C64x+ Interrupt Controller    |  |  |  |  |  |  |

| 0x0181 0000                                 | 0x0181 0FFF    | 4K              | C64x+ Powerdown Controller    |  |  |  |  |  |  |

| 0x0181 1000                                 | 0x0181 1FFF    | 4K              | C64x+ Security ID             |  |  |  |  |  |  |

| 0x0181 2000                                 | 0x0181 2FFF    | 4K              | C64x+ Revision ID             |  |  |  |  |  |  |

| 0x0182 0000                                 | 0x0182 FFFF    | 64K             | C64x+ EMC                     |  |  |  |  |  |  |

| 0x0183 0000                                 | 0x0183 FFFF    | 64K             | Reserved                      |  |  |  |  |  |  |

| 0x0184 0000                                 | 0x0184 FFFF    | 64K             | C64x+ Memory System           |  |  |  |  |  |  |

| 0x0185 0000                                 | 0x0187 FFFF    | 192K            | Reserved                      |  |  |  |  |  |  |

| 0x0188 0000                                 | 0x01BB FFFF    | 3328K           | Reserved                      |  |  |  |  |  |  |

| 0x01BC 0000                                 | 0x01BC 00FF    | 256             | Reserved                      |  |  |  |  |  |  |

| 0x01BC 0100                                 | 0x01BC 01FF    | 256             | Pin Manager and Trace         |  |  |  |  |  |  |

| 0x01BC 0400                                 | 0x01BF FFFF    | 255K            | Reserved                      |  |  |  |  |  |  |

| 0x01C0 0000                                 | 0x01C0 FFFF    | 64K             | EDMA CC                       |  |  |  |  |  |  |

| 0x01C1 0000                                 | 0x01C1 03FF    | 1K              | EDMA TC0                      |  |  |  |  |  |  |

| 0x01C1 0400                                 | 0x01C1 07FF    | 1K              | EDMA TC1                      |  |  |  |  |  |  |

| 0x01C1 0800                                 | 0x01C1 0BFF    | 1K              | EDMA TC2                      |  |  |  |  |  |  |

| 0x01C1 0C00                                 | 0x01C1 FFFF    | 29K             | Reserved                      |  |  |  |  |  |  |

| 0x01C2 0000                                 | 0x01C2 03FF    | 1K              | UART0                         |  |  |  |  |  |  |

| 0x01C2 0400                                 | 0x01C2 07FF    | 1K              | UART1                         |  |  |  |  |  |  |

| 0x01C2 0800                                 | 0x01C2 0FFF    | 2K              | Reserved                      |  |  |  |  |  |  |

| 0x01C2 1000                                 | 0x01C2 13FF    | 1K              | 12C                           |  |  |  |  |  |  |

| 0x01C2 1400                                 | 0x01C2 17FF    | 1K              | Timer0                        |  |  |  |  |  |  |

| 0x01C2 1800                                 | 0x01C2 1BFF    | 1K              | Timer1                        |  |  |  |  |  |  |

| 0x01C2 1C00                                 | 0x01C2 1FFF    | 1K              | Timer2 (Watchdog)             |  |  |  |  |  |  |

| 0x01C2 2000                                 | 0x01C2 23FF    | 1K              | PWM0                          |  |  |  |  |  |  |

| 0x01C2 2400                                 | 0x01C2 27FF    | 1K              | PWM1                          |  |  |  |  |  |  |

| 0x01C2 2800                                 | 0x01C2 2BFF    | 1K              | PWM2                          |  |  |  |  |  |  |

| 0x01C2 2C00                                 | 0x01C2 2FFF    | 1K              | Reserved                      |  |  |  |  |  |  |

| 0x01C2 3000                                 | 0x01C2 3FFF    | 4K              | HECC Control <sup>(1)</sup>   |  |  |  |  |  |  |

| 0x01C2 4000                                 | 0x01C2 53FF    | 5K              | HECC RAM                      |  |  |  |  |  |  |

| 0x01C2 5400                                 | 0x01C3 FFFF    | 107K            | Reserved                      |  |  |  |  |  |  |

| 0x01C4 0000                                 | 0x01C4 07FF    | 2K              | System Module                 |  |  |  |  |  |  |

| 0x01C4 0800                                 | 0x01C4 0BFF    | 1K              | PLL Controller 1              |  |  |  |  |  |  |

| 0x01C4 0C00                                 | 0x01C4 0FFF    | 1K              | PLL Controller 2              |  |  |  |  |  |  |

| 0x01C4 1000                                 | 0x01C4 1FFF    | 4K              | Power and Sleep Controller    |  |  |  |  |  |  |

| 0x01C4 2000                                 | 0x01C6 6FFF    | 148K            | Reserved                      |  |  |  |  |  |  |

| 0x01C6 7000                                 | 0x01C6 77FF    | 2K              | GPIO                          |  |  |  |  |  |  |

| 0x01C6 7800                                 | 0x01C6 7FFF    | 2K              | HPI                           |  |  |  |  |  |  |

| 0x01C6 8000                                 | 0x01C6 FFFF    | 32K             | Reserved                      |  |  |  |  |  |  |

| 0x01C7 0000                                 | 0x01C7 3FFF    | 16K             | VPSS Registers                |  |  |  |  |  |  |

| 0x01C7 4000                                 | 0x01C7 FFFF    | 48K             | Reserved                      |  |  |  |  |  |  |

| 0x01C8 0000                                 | 0x01C8 0FFF    | 4K              | EMAC Control Registers        |  |  |  |  |  |  |

| 0x01C8 1000                                 | 0x01C8 1FFF    | 4K              | EMAC Control Module Registers |  |  |  |  |  |  |

| 0x01C8 2000                                 | 0x01C8 3FFF    | 8K              | EMAC Control Module RAM       |  |  |  |  |  |  |

| 0x01C8 4000                                 | 0x01C8 47FF    | 2K              | MDIO Control Registers        |  |  |  |  |  |  |

| 000 TOO TOO                                 | 0.0100 4711    | ۲۱۱             | METO CONTROL Registers        |  |  |  |  |  |  |

Software must not access "Reserved" locations of the HECC. Access to HECC "Reserved" locations may hang the device. (1)

www.ti.com

# Table 2-4. Configuration Memory Map Summary (continued)

| START<br>ADDRESS | END<br>ADDRESS | SIZE<br>(Bytes) | C64x+                   |

|------------------|----------------|-----------------|-------------------------|

| 0x01C8 4800      | 0x01CF FFFF    | 494K            | Reserved                |

| 0x01D0 0000      | 0x01D0 07FF    | 2K              | McBSP0                  |

| 0x01D0 0800      | 0x01D0 0FFF    | 2K              | Reserved                |

| 0x01D0 1000      | 0x01D0 13FF    | 1K              | McASP0 Control          |

| 0x01D0 1400      | 0x01D0 17FF    | 1K              | McASP0 Data             |

| 0x01D0 1800      | 0x01DF FFFF    | 1018K           | Reserved                |

| 0x01E0 0000      | 0x01E0 0FFF    | 4K              | EMIFA Control           |

| 0x01E0 1000      | 0x01E0 1FFF    | 4K              | VLYNQ Control Registers |

| 0x01E0 2000      | 0x0FFF FFFF    | 226M-8K         | Reserved                |

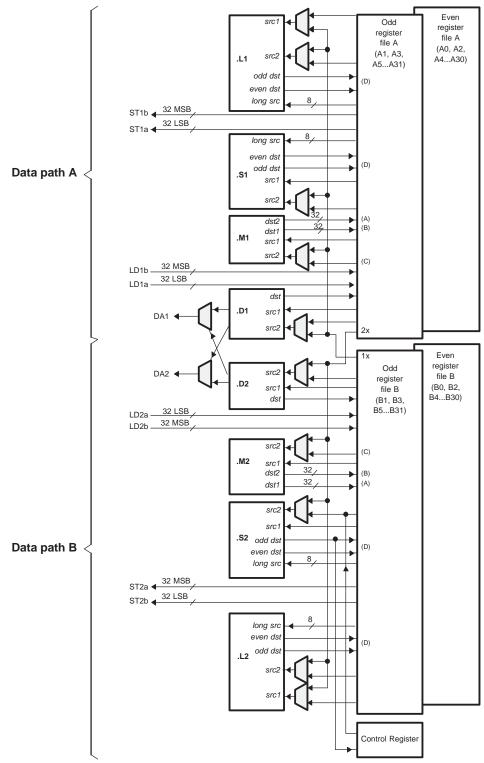

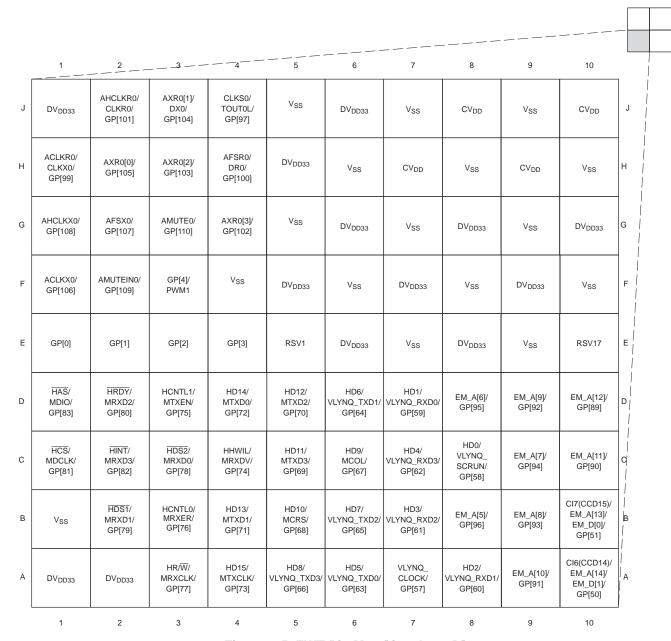

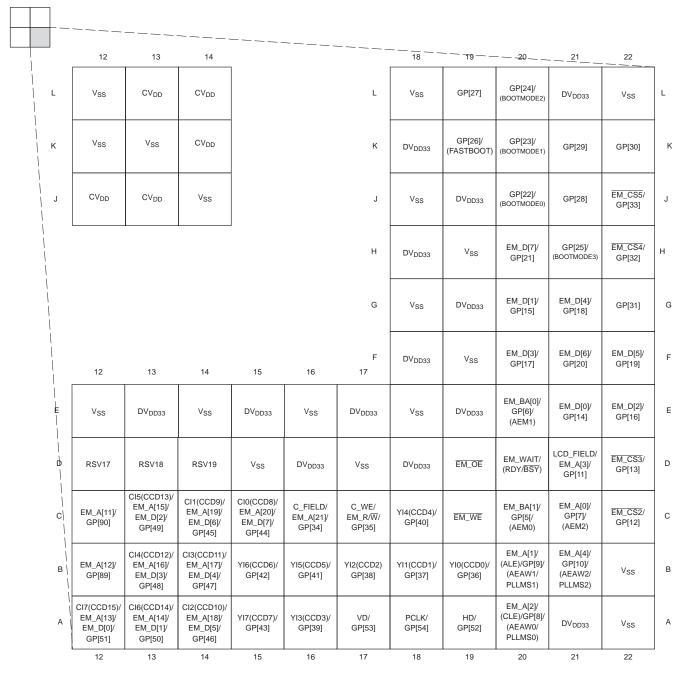

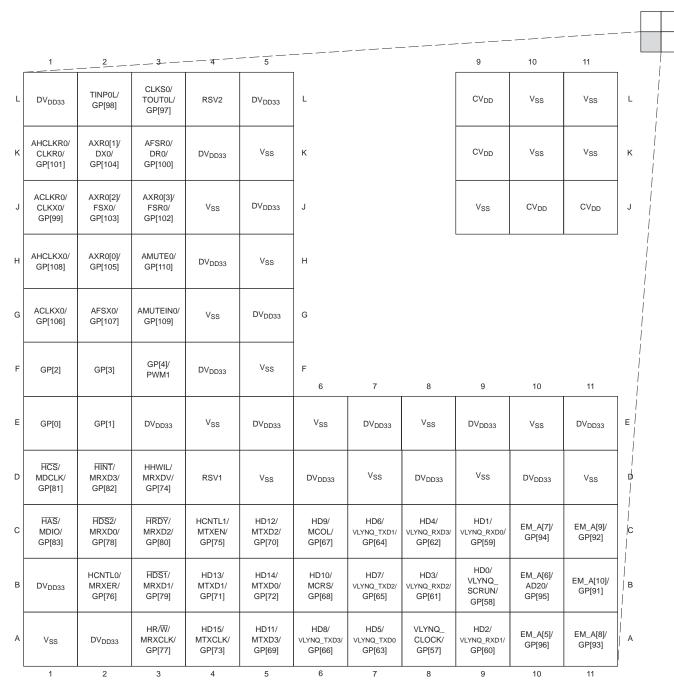

### 2.5 Pin Assignments

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. For more information on pin muxing, see Section 3.7, Multiplexed Pin Configurations of this document.

### 2.5.1 Pin Map (Bottom View)

Figure 2-2 through Figure 2-5 show the bottom view of the ZWT package pin assignments in four quadrants (A, B, C, and D). Figure 2-6 through Figure 2-9 show the bottom view of the ZDU package pin assignments in four quadrants (A, B, C, and D).

|   | 1                           | 2                 | 3                         | 4                                       | 5                  | 6                  | 7                  | 8                  | 9                  | 10                 |                     |

|---|-----------------------------|-------------------|---------------------------|-----------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|

|   | V <sub>SS</sub>             | V <sub>SS</sub>   | DDR_D[7]                  | DDR_D[9]                                | DDR_D[12]          | DDR_D[14]          | DDR_CLK            | DDR_CLK            | DDR_A[12]          | DDR_A[11]          | <br>  w<br>         |

|   | DV <sub>DDR2</sub>          | DDR_D[4]          | DDR_D[6]                  | DDR_D[8]                                | DDR_D[11]          | DDR_D[13]          | DDR_D[15]          | DDR_CKE            | DDR_BA[1]          | DDR_A[8]           | <br> <br>  v        |

|   | DDR_D[2]                    | DDR_D[3]          | DDR_D[5]                  | DDR_DQS[0]                              | DDR_D[10]          | DDR_DQS[1]         | DDR_RAS            | DDR_BA[0]          | DDR_BA[2]          | DDR_A[10]          | <br> <br> <br> <br> |

|   | DDR_D[0]                    | DDR_D[1]          | RSV16                     | DDR_DQM[0]                              | DV <sub>DDR2</sub> | DDR_DQM[1]         | DDR_CAS            | DDR_WE             | DDR_CS             | DDR_ZN             | 1  <br>   <br>      |

|   | V <sub>SS</sub>             | TRST              | TMS                       | DV <sub>DDR2</sub>                      | V <sub>SS</sub>    | DV <sub>DDR2</sub> | V <sub>SS</sub>    | DV <sub>DDR2</sub> | V <sub>SS</sub>    | DV <sub>DDR2</sub> | R                   |

| , | DV <sub>DD33</sub>          | EMU0              | TDO                       | TDI                                     | DV <sub>DDR2</sub> | V <sub>SS</sub>    | DV <sub>DDR2</sub> | V <sub>SS</sub>    | DV <sub>DDR2</sub> | V <sub>SS</sub>    | P                   |

|   | тск                         | EMU1              | RESETOUT                  | POR                                     | V <sub>SS</sub>    | DV <sub>DD33</sub> | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | CV <sub>DD</sub>   | N                   |

|   | CLKOUT0/<br>PWM2/<br>GP[84] | SCL               | SDA                       | RESET                                   | DV <sub>DD33</sub> | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | М                   |

|   | UCTS0<br>GP[87]             | URXD0/<br>GP[85]  | URTS0/<br>PWM0/<br>GP[88] | HECC_RX/<br>TINP1L/<br>URXD1/<br>GP[56] | RSV3               | DV <sub>DD33</sub> | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | CV <sub>DD</sub>   | L                   |

|   | V <sub>SS</sub>             | TINPOL/<br>GP[98] | UTXD0/<br>GP[86]          | HECC_TX/<br>TOUT1L/<br>UTXD1/<br>GP[55] | RSV2               | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | К                   |

|   | 1                           |                   |                           | 4                                       | <sub>5</sub>       | — — 6— — -         |                    | 8                  | 9                  | 10                 |                     |

Figure 2-2. ZWT Pin Map [Quadrant A]

www.ti.com

|                |                   | 11                 | 12                 | 13                 | 14                 | 15                 | 16                   | 17                 | 18                 | 19                 |   |

|----------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------|--------------------|--------------------|--------------------|---|

|                | w                 | DDR_A[6]           | DDR_A[5]           | DDR_A[0]           | DDR_D[16]          | DDR_D[18]          | DDR_D[21]            | DDR_D[27]          | DV <sub>DDR2</sub> | DV <sub>DDR2</sub> | w |

|                | <br> <br> <br>    | DDR_A[7]           | DDR_A[4]           | DDR_A[2]           | DDR_D[17]          | DDR_D[19]          | DDR_D[22]            | DDR_D[24]          | DDR_D[29]          | V <sub>SS</sub>    | V |

|                | ↓<br>↓<br>        | DDR_A[9]           | DDR_A[3]           | DDR_A[1]           | DDR_DQS[2]         | DDR_D[20]          | DDR_DQS[3]           | DDR_D[25]          | DDR_D[28]          | DDR_D[30]          | U |

|                | ј<br>  т<br> <br> | DDR_ZP             | DDR_VDDDLL         | DDR_VSSDLL         | DDR_DQM[2]         | DDR_VREF           | DDR_DQM[3]           | DDR_D[23]          | DDR_D[26]          | DDR_D[31]          | Т |

|                | <br>  R<br>       | V <sub>SS</sub>    | DV <sub>DDR2</sub> | RSV5               | DV <sub>DDR2</sub> | V <sub>SS</sub>    | DV <sub>DDR2</sub>   | $V_{SS}$           | V <sub>SS</sub>    | V <sub>SS</sub>    | R |

| <br> <br>      | Р                 | DV <sub>DDR2</sub> | Vss                | DV <sub>DDR2</sub> | V <sub>SS</sub>    | RSV14              | RSV11                | RSV12              | RSV8               | RSV7               | Р |

| <br> <br> <br> | N                 | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | V <sub>SS</sub>    | RSV13              | RSV15                | RSV10              | RSV9               | RSV6               | N |

| <br> <br> <br> | М                 | CV <sub>DD</sub>   | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | DV <sub>DD33</sub> | V <sub>SS</sub>      | $V_{SS}$           | V <sub>SS</sub>    | V <sub>SS</sub>    | М |

| <br> <br>      | L                 | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | DV <sub>DDR2</sub> | RSV4               | PLL <sub>PWR18</sub> | V <sub>SS</sub>    | MXV <sub>DD</sub>  | V <sub>SS</sub>    | L |

| <br> <br>      | К                 | CV <sub>DD</sub>   | V <sub>SS</sub>    | CV <sub>DD</sub>   | V <sub>SS</sub>    | DV <sub>DD33</sub> | V <sub>SS</sub>      | DV <sub>DD33</sub> | MXV <sub>SS</sub>  | MXI/<br>CLKIN      | К |

|                |                   | 11                 | 12                 | 13                 | 14 — —             |                    |                      | 17                 | 18                 | 19                 | = |

|                |                   |                    |                    |                    |                    |                    |                      |                    |                    |                    |   |

Figure 2-3. ZWT Pin Map [Quadrant B]

SPRS344C-NOVEMBER 2006-REVISED JUNE 2008

Figure 2-4. ZWT Pin Map [Quadrant C]

Figure 2-5. ZWT Pin Map [Quadrant D]

SPRS344C-NOVEMBER 2006-REVISED JUNE 2008 www.ti.com 3 5 6 7 8 9 11 10 DDR\_CLK0  $V_{SS}$  $V_{SS}$ DDR\_D[6] DDR\_D[8] DDR\_D[12] DDR\_D[15] DDR\_CLK0 DDR\_BS[1] DDR\_BS[2] DDR\_A[10] AB AB DDR\_D[4] DDR\_DQS[1] DDR\_A[12] AA  $DV_{DDR2}$ DDR\_D[3] DDR\_DQS[0] DDR\_D[10] DDR\_D[13] DDR\_CKE DDR\_BS[0] DDR\_A[11] AA DDR\_DQM[0] DDR\_DQM[1] DDR\_D[14] DDR\_RAS DDR\_CAS DDR\_CS DDR\_D[11] DDR\_WE DDR\_D[0] DDR\_D[1] DDR\_D[5] Vss DDR\_D[2] RSV17 DDR\_D[7] DDR\_D[9]  $V_{SS}$  $\mathsf{DV}_{\mathsf{DDR2}}$  $V_{SS}$  $DV_{DDR2}$  $V_{SS}$  $DV_{DDR2}$ W  $\mathsf{DV}_{\mathsf{DDR2}}$ TRST TMS  $V_{SS}$  $DV_{DDR2}$  $V_{SS}$  $V_{SS}$  $V_{\text{SS}}$  $DV_{DDR2}$  $DV_{DDR2}$  $DV_{DDR2}$ ٧ 9 10 6 8 11 U TCK TDO TDI DV<sub>DDR2</sub>  $V_{SS}$ RESETOUT EMU0 EMU1  $DV_{DD33}$  $\mathsf{V}_{\mathsf{SS}}$ Т Т CLKOUT0/ PWM2/ POR RESET  $\mathsf{V}_{\mathsf{SS}}$  $\mathsf{DV}_{\mathsf{DD33}}$ R R GP[84] HECC\_RX/ UCTS0/ TINP1L/  $DV_{DD33}$ Р Р  $\mathsf{CV}_\mathsf{DD}$  $\mathsf{CV}_\mathsf{DD}$ SDA  $V_{SS}$  $V_{SS}$ GP[87] URXD1/ Р GP[56] HECC\_TX/ UTXD0/ TOUT1L/ Ν SCL  $\mathsf{DV}_{\mathsf{DD33}}$ Ν  $V_{\text{SS}}$ Ν  $\mathsf{CV}_\mathsf{DD}$  $V_{\text{SS}}$  $\mathsf{V}_{\mathsf{SS}}$ UTXD1/ GP[86] GP[55] URTS0/ URXD0/  $V_{\text{SS}}$ PWM0/ RSV3  $V_{\text{SS}}$ М  $\mathsf{CV}_\mathsf{DD}$  $CV_{DD}$ M Μ  $\mathsf{V}_{\mathsf{SS}}$ GP[85] GP[88] 3 1 2 9 10 11

Figure 2-6. ZDU Pin Map [Quadrant A]

www.ti.com

12 13 15 16 17 18 14 19 DDR\_A[7] DDR\_A[4] DDR\_A[1] DDR\_A[0] DDR\_D[18] DDR\_D[21] DDR\_D[22] DDR\_D[25] DDR\_D[28]  $\mathsf{DV}_{\mathsf{DDR2}}$  $DV_{DDR2}$ ΑB AB DDR\_A[6] DDR\_A[9] DDR\_A[3] DDR\_DQS[2] DDR\_D[16] DDR\_D[19] DDR\_DQS[3] DDR\_D[23] DDR\_D[26] DDR\_D[30] AA  $\mathsf{V}_{\mathsf{SS}}$ AA Υ DDR\_A[8] DDR\_A[5] DDR\_A[2] DDR\_DQM[2] DDR\_D[17] DDR\_D[20] DDR\_DQM[3] DDR\_D[24] DDR\_D[27] DDR\_D[29] DDR\_D[31] Υ DDR\_ZN DDR\_ZP RSV5 DDR\_VREF W Ϋ́  $\mathsf{DDR}\_\mathsf{VDDDLL}$ DDR\_VSSDLL  $\mathsf{DV}_{\mathsf{DDR2}}$  $DV_{DDR2}$  $\mathsf{V}_{\mathsf{SS}}$  $\mathsf{V}_{\mathsf{SS}}$  $\mathsf{V}_{\mathsf{SS}}$  $\mathsf{V}_{\mathsf{SS}}$  $\mathsf{V}_{\mathsf{SS}}$ DV<sub>DDR2</sub> DV<sub>DDR2</sub> RSV12 RSV7 RSV6 ٧  $V_{SS}$  $DV_{DDR2}$  $\mathsf{DV}_{\mathsf{DDR2}}$  $V_{SS}$ 12 13 14 16 17 15 U  $V_{SS}$  $V_{SS}$ RSV11 RSV15 RSV8 U RSV14 RSV13 RSV9 RSV10 Т Т  $\mathsf{V}_{\mathsf{SS}}$ R  $V_{SS}$  $V_{SS}$ R  $V_{SS}$  $V_{SS}$  $V_{SS}$ Ρ Ρ  $DV_{DD33}$ RSV4  $\mathsf{DV}_{\mathsf{DD33}}$  $V_{\text{SS}}$  $\mathsf{DV}_{\mathsf{DD33}}$ Ρ  $\mathsf{CV}_\mathsf{DD}$  $\mathsf{CV}_\mathsf{DD}$  $\mathsf{V}_{\mathsf{SS}}$ MXI/ Ν  $\mathsf{CV}_\mathsf{DD}$  $V_{SS}$  $DV_{DD33}$ PLL<sub>PWR18</sub>  $MXV_{DD}$ Ν  $V_{SS}$  $\mathsf{V}_{\mathsf{SS}}$ CLKIN  $\mathsf{MXV}_{\mathsf{SS}}$ Μ  $V_{SS}$  $\mathsf{CV}_\mathsf{DD}$ М  $DV_{DD33}$  $V_{SS}$ MXO М  $V_{\text{SS}}$  $\mathsf{DV}_{\mathsf{DD33}}$ 18 — — — 19 — 12 13 14 20 21 22

Figure 2-7. ZDU Pin Map [Quadrant B]

Figure 2-8. ZDU Pin Map [Quadrant C]

Figure 2-9. ZDU Pin Map [Quadrant D]

#### 2.6 Terminal Functions

The terminal functions tables (Table 2-5 through Table 2-28) identify the external signal names, the associated pin (ball) numbers along with the mechanical package designator, the pin type, whether the pin has any internal pullup or pulldown resistors, and a functional pin description. For more detailed information on device configuration, peripheral selection, multiplexed/shared pin, and debugging considerations, see the Device Configurations section of this data manual.

All device boot and configuration pins are multiplexed configuration pins— meaning they are multiplexed with functional pins. These pins function as device boot and configuration pins only during device reset. The input states of these pins are sampled and latched into the BOOTCFG register when device reset is deasserted (see Note below). After device reset is deasserted, the values on these multiplexed pins no longer have to hold the configuration.

For proper device operation, external pullup/pulldown resistors may be required on these device boot and configuration pins. Section 3.9.1, Pullup/Pulldown Resistors discusses situations where external pullup/pulldown resistors are required.

Note: Internal to the chip, the two device reset pins RESET and POR are logically AND'd together for the purpose of latching device boot and configuration pins. The values on all device boot and configuration pins are latched into the BOOTCFG register when the logical AND of RESET and POR transitions from low-to-high.

**Table 2-5. BOOT Terminal Functions**

| SIGNAL                                 | SIGNAL     |            |                     |                           |                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------|------------|------------|---------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                   | ZWT<br>NO. | ZDU<br>NO. | TYPE <sup>(1)</sup> | OTHER (2)(3)              | DESCRIPTION                                                                                                                                                                                                                                                                                 |  |

|                                        |            |            |                     | воот                      |                                                                                                                                                                                                                                                                                             |  |

| GP[25]/<br>(BOOTMODE3)                 | G16        | H21        |                     |                           | Destroyed configuration hits. These heatmode functions along                                                                                                                                                                                                                                |  |

| GP[24]/<br>(BOOTMODE2)                 | G15        | L20        | I/O/Z               | IPD                       | Bootmode configuration bits. These bootmode functions along with the FASTBOOT function determine what device bootmode configuration is selected.                                                                                                                                            |  |

| GP[23]/                                | F15        | K20        | 1/0/2               | DV <sub>DD33</sub>        | The DM6435 device supports several types of bootmodes along with a FASTBOOT option; for more details on the types/options,                                                                                                                                                                  |  |

| (BOOTMODE1)                            | F18        | J20        |                     |                           | see Section 3.4.1, Boot Modes.                                                                                                                                                                                                                                                              |  |

| GP[22]/<br>(BOOTMODE0)                 |            |            |                     |                           |                                                                                                                                                                                                                                                                                             |  |

| GP[26]/<br>(FASTBOOT)                  | G17        | K19        | I/O/Z               | IPD<br>DV <sub>DD33</sub> | Fast Boot<br>0 = Not Fast Boot<br>1 = Fast Boot                                                                                                                                                                                                                                             |  |

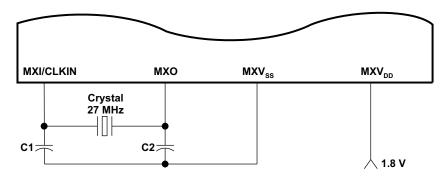

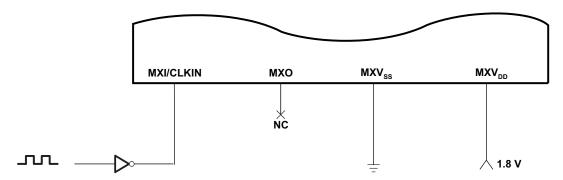

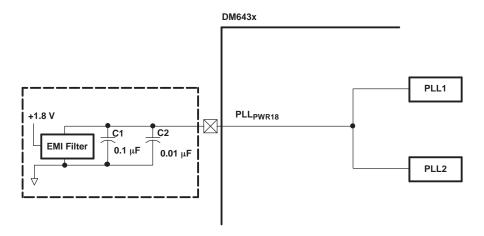

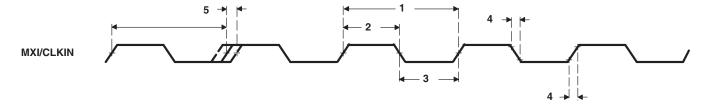

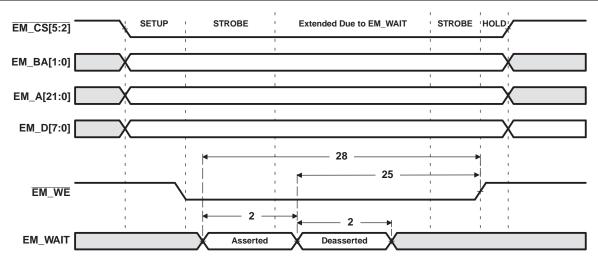

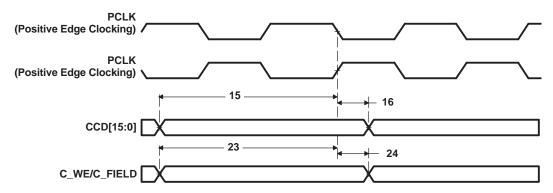

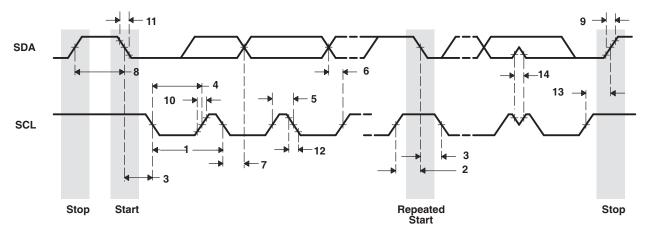

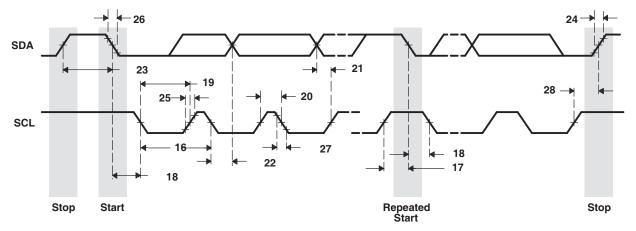

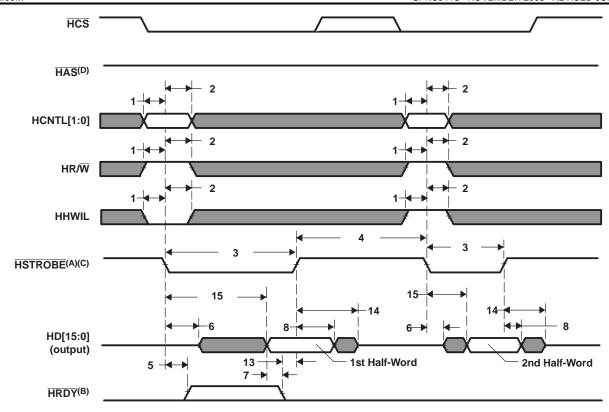

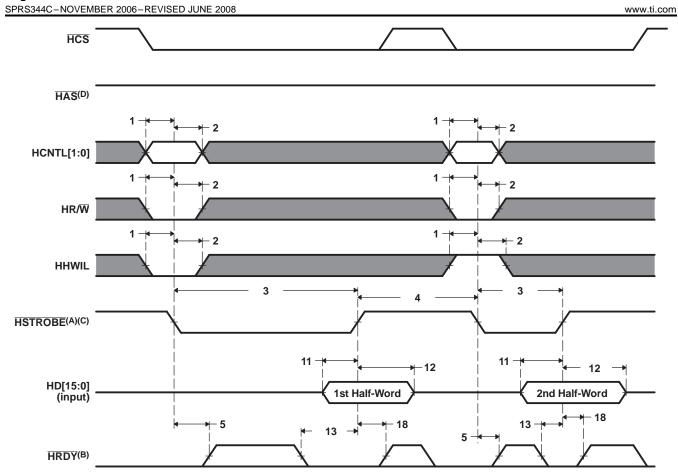

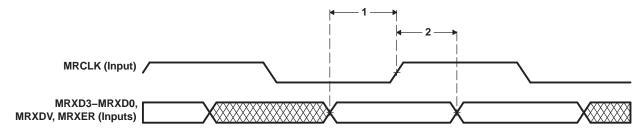

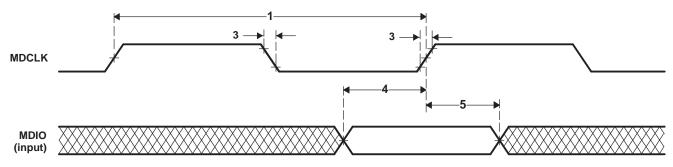

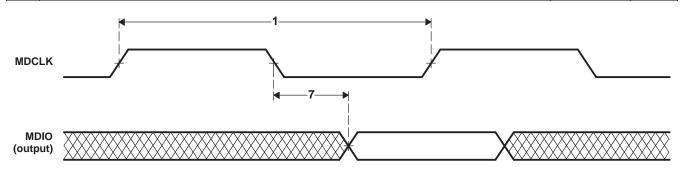

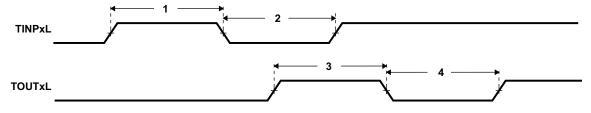

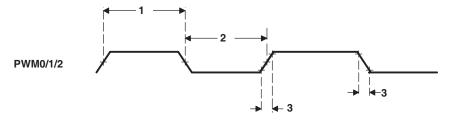

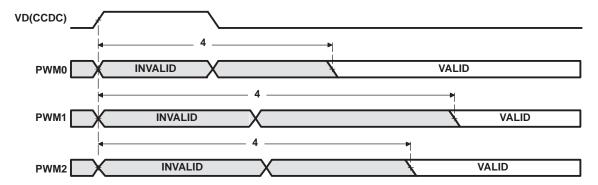

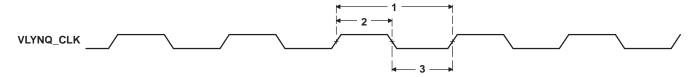

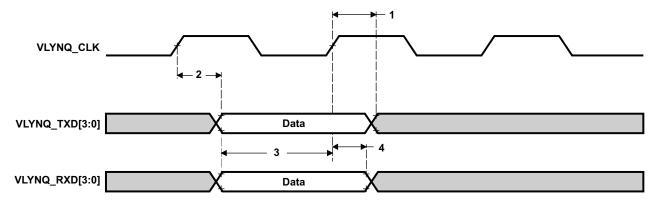

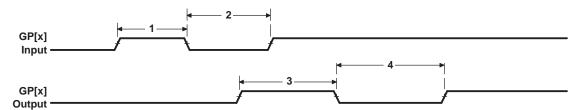

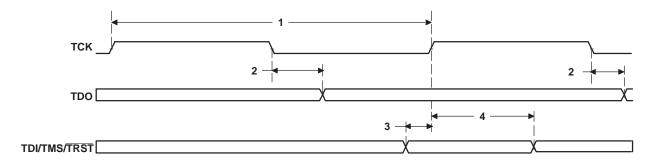

| EM_A[4]/GP[10]/<br>(AEAW2/PLLMS2)      | A17        | B21        | I/O/Z               | IPD<br>DV <sub>DD33</sub> | EMIFA Address Bus Width (AEAW) and Fast Boot PLL Multiplier Select (PLLMS).                                                                                                                                                                                                                 |  |