SLUSCR7-MAY 2017

TPS92518

# TPS92518 Dual Channel Buck LED Controller with SPI Interface, Analog and PWM Dimming

#### 1 Features

- Wide Input Voltage Range 6.5 V to 65 V

- · Two independent Buck LED Controllers

- High Bandwidth, Quasi-Hysteretic Control

- Adjustable High-Side Sense

- Direct PWM Dimming Input

- Cycle-by-Cycle Current Limit

- SPI Communications Interface

- Software configurable Set Points (8-bit)

- Digital Calibration and Binning

- Fault Monitoring and Reporting

- Advanced, High Precision Dimming

- 10,000:1 PWM Dimming Range

- 255:1 Analog Dimming Range

- High Frequency Shunt FET Dimming

### 2 Applications

- · Color Mixing Applications

- Aftermarket Lighting Applications

- LED General Lighting

- Projector Applications

### 3 Description

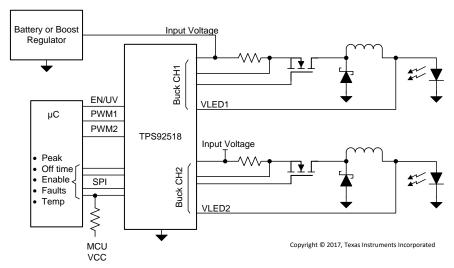

The TPS92518 family of parts are dual channel buck LED current controllers with a SPI communications interface. The serial communication interface provides a singular communication path for multichannel and platform lighting driver module (LDM) applications.

The TPS92518 uses a quasi-hysteretic control method that supports switching frequencies ranging from 1 kHz to 2 MHz. This control method enables superior, high frequency shunt FET dimming and also handles the demanding dynamic loads of adaptive LED matrix based headlamp systems.

Software programmable SPI set points (Precision Peak Current, Controlled Off-Time and Output Voltage Sense) enables designers to develop a single LED driver solution for multiple load configurations that can be quickly reconfigured for future LED driver design requirements.

The TPS92518 device has an input range up to 42 V. The TPS92518HV is a high-voltage option with an input range up to 65 V.

#### Device Information<sup>(1)</sup>

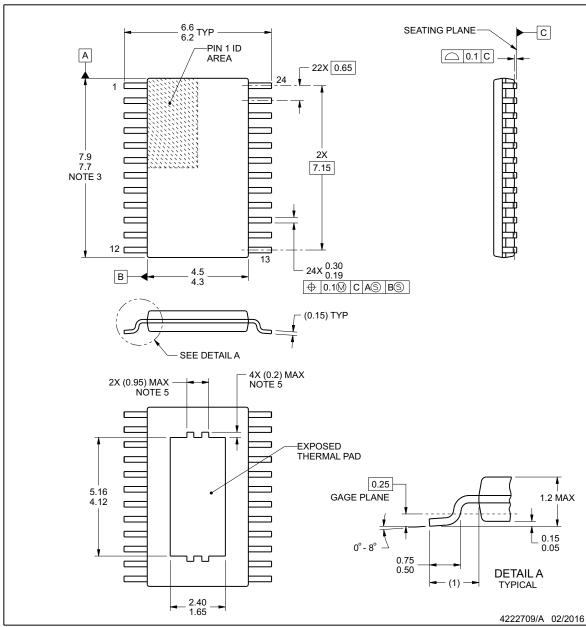

| PART NUMBER | PACKAGE      | BODY SIZE (NOM) |

|-------------|--------------|-----------------|

| TPS92518    | LITECOD (24) | 77 4.4          |

| TPS92518HV  | HTSSOP (24)  | 7.7 mm x 4.4 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

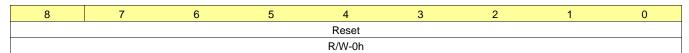

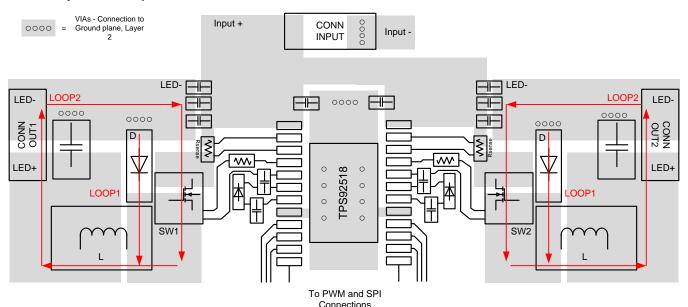

#### Simplified Schematic

## **Table of Contents**

| 1 | Features 1                                    | 8.5 Registers29                                        |

|---|-----------------------------------------------|--------------------------------------------------------|

| 2 | Applications 1                                | 8.6 Programming 4                                      |

| 3 | Description 1                                 | 9 Application and Implementation 43                    |

| 4 | Revision History2                             | 9.1 Application Information4                           |

| 5 | Pin Configuration and Functions               | 9.2 Typical Application4                               |

| 6 | Specifications                                | 9.3 Dos and Don'ts4                                    |

| • | 6.1 Absolute Maximum Ratings                  | 10 Power Supply Recommendations 46                     |

|   | 6.2 ESD Ratings                               | 10.1 Input Source Direct from Battery 4                |

|   | 6.3 Recommended Operating Conditions          | 10.2 Input Source from a Boost Stage4                  |

|   | 6.4 Thermal Information                       | 11 Layout 4                                            |

|   | 6.5 Electrical Characteristics                | 11.1 Layout Guidelines4                                |

|   | 6.6 Typical Characteristics                   | 11.2 Layout Example4                                   |

| 7 | Parameter Measurement Information 9           | 12 Device and Documentation Support 48                 |

|   | 7.1 CSN Pin Falling Delay (t <sub>DFI</sub> ) | 12.1 Receiving Notification of Documentation Updates 4 |

|   | 7.2 Off-Timer (t <sub>OFF</sub> )             | 12.2 Community Resources 4                             |

| 8 | Detailed Description 10                       | 12.3 Trademarks 4                                      |

| • | 8.1 Overview                                  | 12.4 Electrostatic Discharge Caution 4                 |

|   | 8.2 Functional Block Diagram                  | 12.5 Glossary                                          |

|   | 8.3 Feature Description                       | 13 Mechanical, Packaging, and Orderable                |

|   | 8.4 Serial Interface                          | Information 48                                         |

## 4 Revision History

| DATE     | REVISION | NOTES            |

|----------|----------|------------------|

| May 2017 | *        | Initial release. |

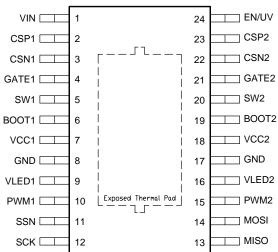

## 5 Pin Configuration and Functions

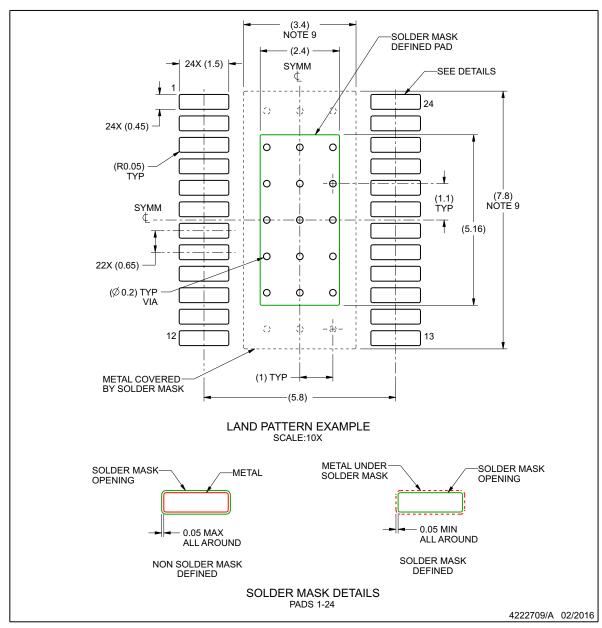

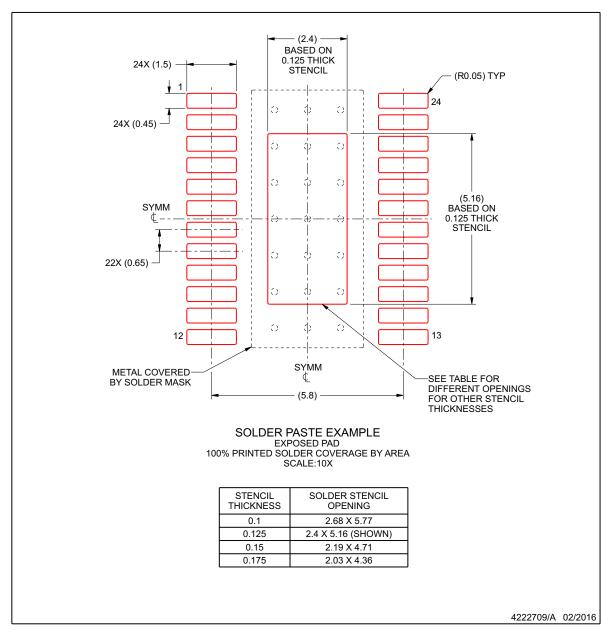

## PWP Package 24-Pin HTTSOP Top View

#### **Pin Functions**

| PINS           |        |     |                                                                                                                                                                  |  |

|----------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO.       |        | 1/0 | DESCRIPTION                                                                                                                                                      |  |

| BOOT1          | 6      | ı   | Channel 1 bootstrap voltage input                                                                                                                                |  |

| BOOT2          | 19     | 1   | Channel 2 bootstrap voltage input                                                                                                                                |  |

| CSN1           | 3      | ı   | Channel 1 negative current sense input                                                                                                                           |  |

| CSN2           | 22     | 1   | Channel 2 negative current sense input                                                                                                                           |  |

| CSP1           | 2      | 1   | Channel 1 positive current sense input                                                                                                                           |  |

| CSP2           | 23     | ı   | Channel 2 positive current sense input                                                                                                                           |  |

| EN/UV          | 24     | I   | Device enable. If not configured as under voltage lock out or enable, tie to VCCx. Tie to >23.6V to bypass SPI communication and enable default register values. |  |

| GATE1          | 4      | 0   | Channel 1 gate drive output. Connect to FET gate                                                                                                                 |  |

| GATE2          | 21     | 0   | Channel 2 gate drive output. Connect to FET gate                                                                                                                 |  |

| CNID           | 8      | 0   | 0                                                                                                                                                                |  |

| GND            | 17     | G   | System ground                                                                                                                                                    |  |

| MISO           | 13     | 0   | SPI data output                                                                                                                                                  |  |

| MOSI           | 14     | ı   | SPI data input                                                                                                                                                   |  |

| PWM1           | 10     | ı   | Channel 1 PWM dimming input. Tie to VCCx if PWM pin control is not required.                                                                                     |  |

| PWM2           | 15     | 1   | Channel 2 PWM dimming input. Tie to VCCx if PWM pin control is not required.                                                                                     |  |

| SCK            | 12     | ı   | SPI clock input                                                                                                                                                  |  |

| SSN            | 11     | 1   | SPI slave select input                                                                                                                                           |  |

| SW1            | 5      | ı   | Channel 1 switch node connection                                                                                                                                 |  |

| SW2            | 20     | 1   | Channel 2 switch node connection                                                                                                                                 |  |

| VCC1           | 7      | 0   | Channel 1 supply voltage output. May be used to power low current external circuits. See <i>Application and Implementation</i> section.                          |  |

| VCC2           | 18     | 0   | Channel 2 supply voltage output. May be used to power low current external circuits. See <i>Application and Implementation</i> section.                          |  |

| VIN            | 1      | I   | Device power supply voltage input. May be common to CSP1, CSP2 or an independent supply.                                                                         |  |

| VLED1          | 9      | - 1 | Channel 1 output voltage sense.                                                                                                                                  |  |

| VLED2          | 16     | ı   | Channel 2 output voltage sense.                                                                                                                                  |  |

| Exposed therma | al pad | G   | Connect to ground. Add vias to improve thermal performance.                                                                                                      |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                           |            | MIN  | MAX | UNIT |

|-------------------------------------------|------------|------|-----|------|

| VIN ENVIN CODY CONY OWN VI EDV to CND     | TPS92518HV | -0.3 | 67  |      |

| VIN, EN/UV, CSPx, CSNx, SWx, VLEDx to GND | TPS92518   | -0.3 | 44  |      |

| MOSI, MISO, SCK, SSN to GND               |            | -0.3 | 5.5 |      |

| PWMx, VCCx to GND                         |            | -0.3 | 8.8 |      |

| GATEx, BOOTx to SWx                       |            | -0.3 | 8.8 | V    |

| CATE POOT IS OND                          | TPS92518HV | -0.3 | 75  |      |

| GATEx, BOOTx to GND                       | TPS92518   | -0.3 | 52  |      |

| CSPx to CSNx                              |            | -0.3 | 5.5 |      |

| SWx to GND, 10ns transient                |            | -2   |     |      |

| Junction temperature, T <sub>J</sub>      |            | -40  | 150 | °C   |

| Storage temperature , T <sub>stg</sub>    |            | -65  | 165 | 10   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                          |                                                         | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------|-------|------|

| .,                 | Floatroatatia dia aharra | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Charged-device model (CDM), per V AEC Q100-011          | ±750  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                   |            | MIN | MAX | UNIT |

|----------------|-----------------------------------|------------|-----|-----|------|

| VINI           | N Input Voltage                   | TPS92518HV | 6.5 | 65  | V    |

| VIN            |                                   | TPS92518   | 6.5 | 42  | V    |

| T <sub>A</sub> | Operating ambient temperature (1) |            | -40 | 125 | °C   |

| TJ             | Operating junction temperature    |            | -40 | 150 | °C   |

<sup>(1)</sup> The TPS92518-Q1 can operate at an ambient temperature of up to +125°C as long as the junction temperature maximum of +150°C is not exceeded.

### 6.4 Thermal Information

|                      |                                              | TPS92518     |      |

|----------------------|----------------------------------------------|--------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                      |                                              | 24 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 32.5         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 17.9         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 15.7         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.4          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 15.5         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.8          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

$V_{VIN} = 14 \text{ V}$ , -40 °C  $\leq T_{IJ} \leq 150 \text{ °C}$ , unless otherwise specified

|                            | PARAMETER                                                     | TEST CONDITIONS                                                                     | MIN   | TYP  | MAX   | UNIT |

|----------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|------|-------|------|

| VCCx, VIN                  |                                                               |                                                                                     |       |      |       |      |

| V <sub>CCx</sub>           | VCCx Voltage                                                  | V <sub>VIN</sub> = 40 V or V <sub>VIN</sub> = 65 V, 0 A ≤<br>External Load ≤ 500 μA | 6.9   | 7.5  | 8.25  | V    |

| V <sub>CCx2</sub>          | VCCx Voltage with External Load                               | External Load = 500 µA                                                              | 6.9   | 7.5  | 8.25  | V    |

| V <sub>CCx_UVLO</sub>      | VCCx undervoltage lockout                                     | Falling threshold, V <sub>VIN</sub> = 10 V                                          | 5.65  | 5.9  | 6.1   | V    |

| V <sub>CCx_UVHYS</sub>     | VCCx undervoltage lockout Hysteresis                          |                                                                                     |       | 0.25 |       | V    |

| VCCx-LIM                   | VCCx regulator current limit                                  | V <sub>CC</sub> shorted to GND.                                                     | 25    | 38   | 48    | mA   |

| l <sub>vin</sub>           | Operating Current                                             | Not Switching                                                                       |       | 3    | 4     | mA   |

| V <sub>DO</sub>            | LDO drop-out voltage                                          | I <sub>VCC</sub> = 5 mA, V <sub>VIN</sub> = 5 V                                     |       | 90   | 225   | mV   |

| Peak Current Comp          | arator (CSPx, CSNx)                                           |                                                                                     |       |      |       |      |

|                            |                                                               | LEDx_PKTH_DAC = 255                                                                 | 245   | 255  | 265   | mV   |

| $V_{CSTx}$                 | $V_{CSPx}$ - $V_{CSNx}$ peak current threshold                | LEDx_PKTH_DAC = 127                                                                 | 118.5 | 127  | 135.5 | mV   |

|                            |                                                               | LEDx_PKTH_DAC = 10                                                                  |       | 10   |       | mV   |

| l <sub>CSN</sub>           | CSN input bias current                                        |                                                                                     |       | 0.4  | 1.5   | μA   |

| DEL                        | CSN pin falling delay                                         | CSNx fall to GATEx fall (1V/us stimulus)                                            |       | 58   | 110   | ns   |

| LEB                        | Leading edge blanking (minimum ontime)                        | Minimum Pulse Width                                                                 | 165   | 200  | 235   | ns   |

| CSP <sub>UVLO</sub>        | CSPx UVLO Falling Threshold                                   |                                                                                     | 4.65  | 4.90 | 5.15  | V    |

| CSP <sub>UVLO-H</sub>      | CSPx UVLO Hysteresis                                          |                                                                                     |       | 520  |       | mV   |

| Gate Drivers (GATE         | x, SWx and BOOTx)                                             |                                                                                     |       |      |       |      |

| R <sub>DSP</sub>           | GATEx PFET ( R <sub>DS High</sub> )                           |                                                                                     |       | 7.3  |       | Ω    |

| R <sub>DSN</sub>           | GATEx NFET ( R <sub>DS Low</sub> )                            |                                                                                     |       | 2.8  |       | Ω    |

| V <sub>BOOT-UVLO</sub>     | Voltage where gate drive is disabled                          | V <sub>BOOT</sub> to V <sub>SW</sub> , V <sub>BOOT</sub> falling                    | 3.6   | 4.4  | 5.2   | V    |

| V <sub>BOOT-UVLO-HYS</sub> | Hysteresis on BOOTx UVLO                                      | V <sub>BOOTx</sub> to V <sub>SWx</sub>                                              |       | 200  |       | mV   |

| PD PWMx                    | Pull down from SWx when PWMx Low                              | PWMx low, (BOOTx to SWx) = 5V,<br>V <sub>SWx</sub> = 8V                             |       | 200  | 260   | μΑ   |

| PD BOOTx                   | V <sub>BOOTx</sub> -V <sub>SWx</sub> < V <sub>BOOT-UVLO</sub> | PWMx high, (BOOTx to SWx) < BOOT_UVLO, V <sub>SWx</sub> = 8 V                       |       | 5    | 7     | mA   |

| BOOT_Q                     | BOOTx quiescent current                                       | (BOOTx to SWx) = 5.5 V, 0 V ≤ V <sub>SWx</sub> ≤ 65 V                               |       | 100  | 200   | μA   |

| OFF-TIMER                  |                                                               |                                                                                     |       |      |       |      |

| toff                       | Off-time                                                      | V <sub>LEDx</sub> = 30 V, t <sub>OFFX</sub> DAC = 255                               | 3.2   | 4.1  | 4.8   | μs   |

| t <sub>D-OFF</sub>         | COFF threshold to gate rising delay                           | Specified by design                                                                 |       | 50   |       | ns   |

| t <sub>OFF-MAX</sub>       | Maximum off-time                                              | t <sub>OFF-MAX</sub> DAC = 255                                                      |       | 65   |       | μs   |

## **Electrical Characteristics (continued)**

$V_{VIN}$  = 14 V, -40 °C ≤  $T_J$  ≤ 150 °C, unless otherwise specified

|                          | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                 | MIN  | TYP  | MAX                 | UNIT |

|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------------------|------|

| Enable and Input UVLO    |                                              |                                                                                                                                                                                 |      |      |                     |      |

| V <sub>EN/UV1</sub>      | EN/UV pin threshold                          | EN/UV pin rising                                                                                                                                                                | 1.18 | 1.24 | 1.30                | V    |

| V <sub>EN/UV-HYS1</sub>  | EN/UV pin hysteresis                         | Difference between rising and falling threshold                                                                                                                                 |      | 100  |                     | mV   |

| t <sub>EN/UV1</sub>      | EN/UV pin delay                              | EN/UV pin rising to GATEx pin rising.<br>LEDx_MAXOFF_DAC = 0                                                                                                                    |      | 300  |                     | ns   |

| EN/OV1                   | 2.00 pm dolay                                | EN/UV pin falling to GATEx pin falling                                                                                                                                          |      | 470  |                     | ns   |

| I <sub>EN/UV-HYST1</sub> | EN/UV Hysteresis Current                     | EN/UV = 2 V                                                                                                                                                                     | 12   | 16   | 28                  | μA   |

| V <sub>EN/UV2</sub>      | EN/UV LED1_EN and LED2_EN override threshold | EN/UV pin rising writes LED1_EN and LED2_EN = 1                                                                                                                                 |      | 23.4 |                     | V    |

| V <sub>EN/UV-HYS2</sub>  | EN/UV pin hysteresis                         | Difference between rising and falling threshold                                                                                                                                 |      | 3    |                     | V    |

| t <sub>EN/UV2</sub>      | EN/UV pin delay 2                            | EN/UV pin rising to GATEx pin rising.<br>LEDx_MAXOFF_DAC = 0                                                                                                                    |      | 520  |                     | ns   |

| PWM, MOSI, SCK, SSN      |                                              |                                                                                                                                                                                 |      |      |                     |      |

| I <sub>LKG</sub>         | Leakage current                              |                                                                                                                                                                                 |      |      | 1                   | μΑ   |

| $V_{IL}$                 | Low level input voltage threshold            |                                                                                                                                                                                 | 0.8  |      |                     | V    |

| V <sub>IH</sub>          | High level input voltage threshold           |                                                                                                                                                                                 |      |      | 1.8                 | V    |

| <u></u>                  | PWM nin delay                                | PWM pin rising to GATE pin rising                                                                                                                                               |      | 68   | 105                 | ns   |

| t <sub>PWM</sub>         | PWM pin delay                                | PWM pin falling to GATE pin falling                                                                                                                                             |      | 55   | 100                 | ns   |

| MISO                     |                                              |                                                                                                                                                                                 |      |      |                     |      |

| V <sub>OL</sub>          | MISO low, I <sub>MISO</sub> applied          | I <sub>MISO</sub> = 10 mA                                                                                                                                                       |      | 0.26 | 0.51                | V    |

| R <sub>DS</sub>          | MISO Pull-down resistance                    | I <sub>MISO</sub> = 10 mA                                                                                                                                                       |      | 26   |                     | Ω    |

| ADC                      |                                              |                                                                                                                                                                                 |      |      |                     |      |

|                          | ADC Reading T = -40°C                        |                                                                                                                                                                                 |      | 104  |                     | Code |

| $ADC_{TEMP}$             | ADC Reading T = 25°C                         |                                                                                                                                                                                 |      | 130  |                     | Code |

|                          | ADC Reading T= 150°C                         |                                                                                                                                                                                 |      | 171  |                     | Code |

|                          | ADC Reading V <sub>LEDx</sub> = 60 V         |                                                                                                                                                                                 | 226  | 230  | 240                 | Code |

| $ADC_{LEDx}$             | ADC Reading V <sub>LEDx</sub> = 10 V         |                                                                                                                                                                                 | 37   | 38   | 39                  | Code |

| LLDX                     | ADC Reading V <sub>LEDx</sub> = 1 V          |                                                                                                                                                                                 | 2    | 3    | 4                   | Code |

| SPI Interface            | O LEBA                                       |                                                                                                                                                                                 |      |      |                     |      |

| t <sub>ss_su</sub>       | SSN Setup Time                               | Falling edge of SSN to 1st SCK rising edge                                                                                                                                      | 500  |      |                     | ns   |

| t <sub>SS_H</sub>        | SSN Hold Time                                | Falling edge of 16th SCK to SSN rising edge                                                                                                                                     | 250  |      |                     | ns   |

| t <sub>SCK</sub>         | SCK Period                                   | Clock period                                                                                                                                                                    | 500  |      |                     | ns   |

| D <sub>SCK</sub>         | SCK Duty Cycle                               | Clock duty cycle                                                                                                                                                                | 40   |      | 60                  | %    |

| t <sub>SU</sub>          | MOSI Setup Time                              | MOSI valid to rising edge SCK                                                                                                                                                   | 250  |      |                     | ns   |

| t <sub>H</sub>           | MOSI Hold Time                               | MOSI valid after rising edge SCK                                                                                                                                                | 275  |      |                     | ns   |

| t <sub>HI_Z</sub>        | MISO Tri-State Time                          | Time to tri-state (deactivate low-side switch) MISO after SSN rising edge                                                                                                       | 110  |      | 320                 | ns   |

| t <sub>MISO_HL</sub>     | MISO Valid High-to-Low                       | Time to place valid "0" on MISO after falling SCK edge                                                                                                                          |      |      | 320                 | ns   |

| t <sub>MISO_LH</sub>     | MISO Valid Low-to-High                       | Time to tri-state (deactivate the internal low-side switch) MISO after falling SCK edge. t <sub>RC</sub> is the time added by the application total capacitance and resistance. |      |      | 320+t <sub>RC</sub> | ns   |

| t <sub>ZO_HL</sub>       | MISO Drive Time High-to-Low                  | SSN Falling Edge to MISO Falling                                                                                                                                                |      |      | 320                 | ns   |

| t <sub>SS</sub>          | SSN High Time                                | How long SSN must remain high between transactions                                                                                                                              | 1000 |      |                     | ns   |

| THERMAL SHUTDOWN         |                                              |                                                                                                                                                                                 |      |      | U.                  |      |

| TSD                      | Thermal shutdown temperature                 |                                                                                                                                                                                 |      | 175  |                     | 00   |

| TSD HYST                 | Thermal shutdown hysteresis                  |                                                                                                                                                                                 |      | 10   |                     | °C   |

Product Folder Links: TPS92518

EXAS NSTRUMENTS

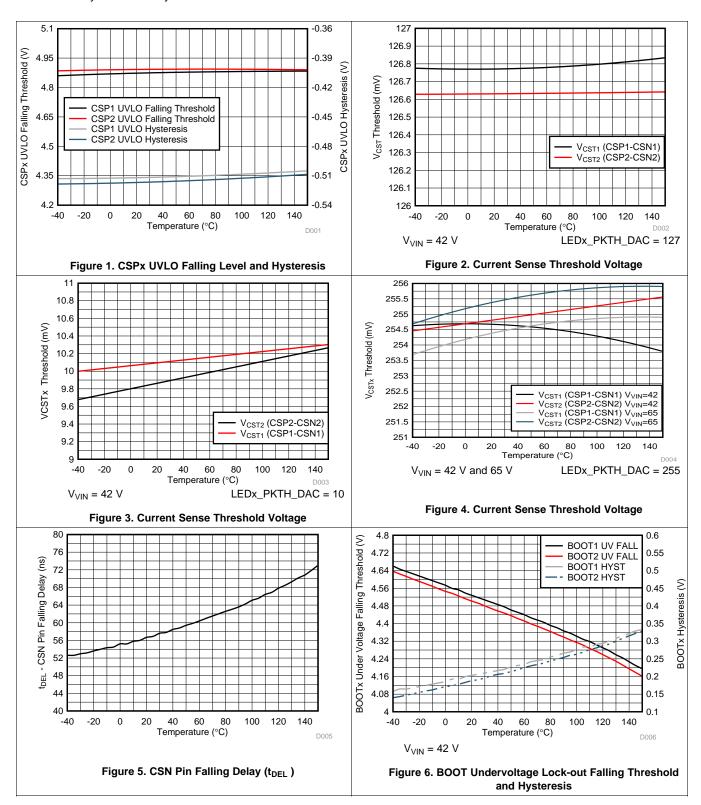

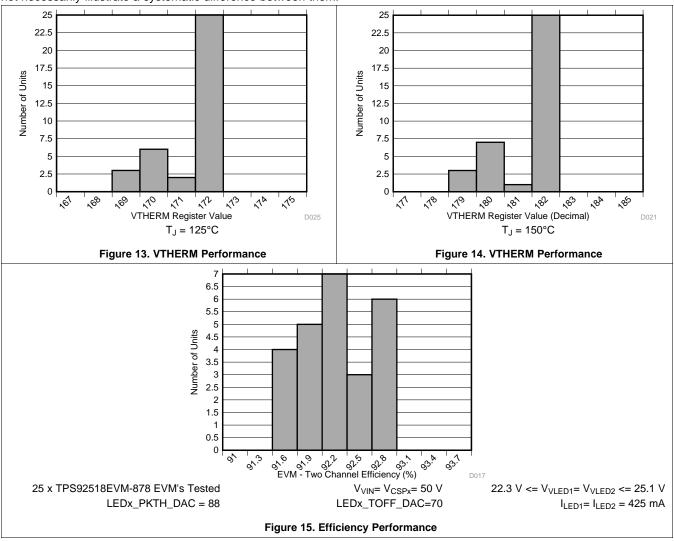

## 6.6 Typical Characteristics

$V_{VIN}$  = 14 V unless otherwise specified. Temperature = Junction Temperature. Note: Any difference between channels does not necessarily illustrate a systematic difference between them.

Copyright © 2017, Texas Instruments Incorporated

Submit Documentation Feedback

## TEXAS INSTRUMENTS

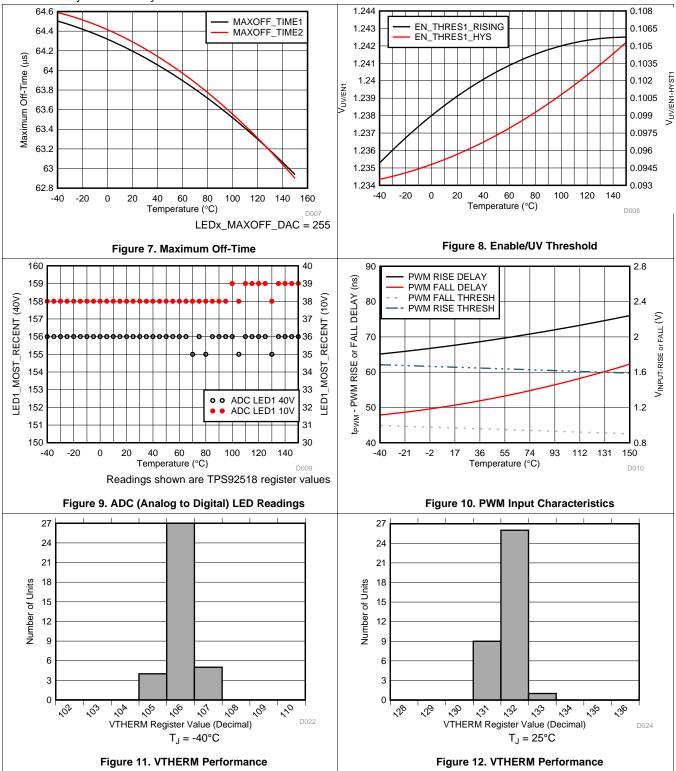

## **Typical Characteristics (continued)**

$V_{VIN}$  = 14 V unless otherwise specified. Temperature = Junction Temperature. Note: Any difference between channels does not necessarily illustrate a systematic difference between them.

### **Typical Characteristics (continued)**

$V_{VIN}$  = 14 V unless otherwise specified. Temperature = Junction Temperature. Note: Any difference between channels does not necessarily illustrate a systematic difference between them.

#### 7 Parameter Measurement Information

## 7.1 CSN Pin Falling Delay (t<sub>DEL</sub>)

A voltage is applied between CSP to CSN to trip the Peak Current threshold. The difference in time between the peak current activation and the Gate signal turning off is measured.

#### 7.2 Off-Timer (t<sub>OFF</sub>)

A voltage is applied to the VLEDx pin. The peak current comparator is tripped and the time between the gate falling and rising is measured.

#### 8 Detailed Description

#### 8.1 Overview

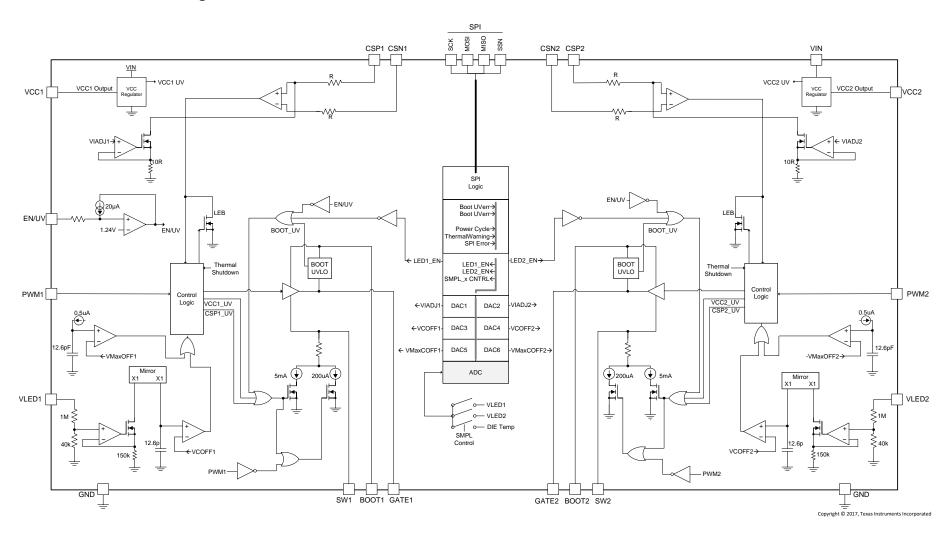

The TPS92518 is a Dual Channel Buck LED controller with SPI Interface. Quasi-hysteretic operation allows a high control bandwidth and is ideal for Shunt FET and Matrix applications (series LED switched network). Internal DACs control the high-side differential peak current sense threshold, the peak-to-peak ripple (off-time) and the maximum off-time.

The high-side differential peak current sense threshold trip voltage is set via a 10:1 divider. The divider allows a lower sense voltage for improved efficiency while still allowing a practical control voltage. The device uses a controlled off-time (COFT) architecture to allow the converter to operate in both continuous conduction mode (CCM) and discontinuous conduction mode (DCM) with no external control loop compensation, and provides an inherent cycle-by-cycle current limit because of the peak current detection each cycle. Once an off-time (us·V) target is digitally programmed, analog circuitry adjusts the off-time to maintain a constant peak-to-peak ripple. Since the peak and ripple are fixed, regulation is maintained. The programmable off-time also controls the switching frequency target.

The digitally controlled analog peak current sense threshold allows analog dimming of the LED current over the full output range. The PWM dimming input allows for high-frequency PWM dimming control requiring no external components. An internal configurable maximum off-timer allows for easy implementation of external shunt FET dimming. Refer to *shunt FET dimming information*. This simple regulator contains all the features necessary to implement a high-efficiency, versatile, digitally controlled, high-performance LED driver.

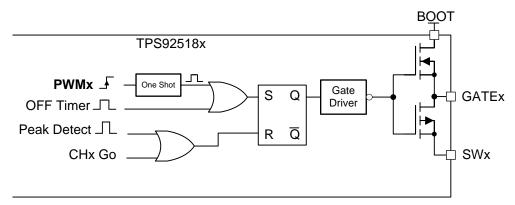

## 8.2 Functional Block Diagram

Submit Documentation Feedback

11

## TEXAS INSTRUMENTS

#### 8.3 Feature Description

#### 8.3.1 General Operation

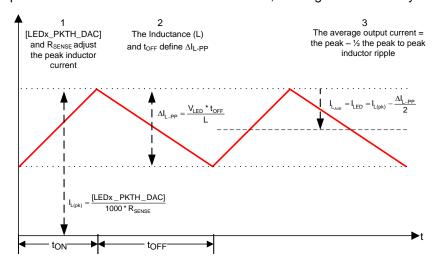

The TPS92518 operates using a peak-current, constant off-time control as described in Figure 16. Two states dictate the high-side FET control. The switch turns on and stays on until the programmed peak current is reached. The peak current is controlled by monitoring the voltage across the sense resistor. When the voltage drop is higher than the programmed threshold, the peak current is reached. The switch is then turned OFF, which initiates an off-time period. An internal capacitor is then charged by a current source which varies in relation to the VLEDx pin voltage. When the capacitor voltage reaches the DAC controlled threshold, the off-time ends. The off-time capacitor resets and the main switch turns ON, starting the next ON cycle.

Figure 16. Hysteretic Operation

#### 8.3.1.1 Constant Off-Time vs. Constant µs×V operation

Although commonly referred to as *constant off-time*, the off-time does vary with the output voltage in the standard TPS92518 configuration. This relation ensures constant peak-to-peak inductor current ripple ( $\Delta I_{L-PP}$ ). Although not common, the VLEDx pin can be set to a fixed value to generate a truly constant off-time and limit changes in frequency, however current regulation degrades. To maintain regulation and a constant ripple over various output voltages, the converter off-time must become shorter or longer as VLEDx pin voltage changes. This results in a change in frequency. In this regard, the off-time register can be considered as a seconds-times-volts setting (s x V) for the converter. The TPS92518 *Electrical Characteristics* table specification for off-time specifies a certain off time duration for a certain register value. The time is also dependent on the VLEDx pin voltage. For example, the off-time is specified at 4 µs for a  $V_{VLEDx}$ = 30 V and LEDx\_TOFF\_DAC = 255. The internal analog circuitry operates to keep the ripple and µs·V (micro-second volt) product constant. If the LEDx voltage changes to 15 V, the off time adjusts to 8 µs. If the LEDx voltage changes to 60 V the off time adjusts to 2 µs, and so on.

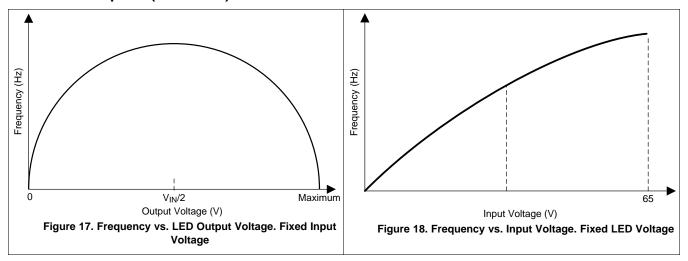

Two general cases can be examined: If the input voltage and output voltage are relatively constant, the frequency also remains constant. If either the input voltage or the output voltage changes, the frequency changes. For a fixed input voltage, the device operates at the maximum frequency at 50% duty cycle and the frequency reduces as the duty cycle becomes shorter or longer. A graphical representation is shown in Figure 17.

For a fixed output voltage ( $V_{VLEDx}$ ), the off-time stays fixed. The frequency then increases as the duty cycle becomes smaller with an increasing VIN voltage. This relation is shown in Figure 18.

#### **Feature Description (continued)**

#### 8.3.1.2 Output Equation

By maintaining the off-time proportional to the output voltage (constant µs·V), it is possible to illustrate how the LED voltage (VLEDx) can be removed from the output current equation.

Starting with the inductor ripple derived from:

$$V = L \frac{di}{dt}$$

(1)

and the equation for the off-time:

$$t_{OFF} = \frac{LEDx\_TOFF\_DAC[7:0]}{2.136 \times 10^6 \times VLEDx}$$

(2)

the VLEDx term is then eliminated and the peak-to-peak inductor current ripple is defined by:

$$\Delta I_{L-PP} = \frac{\text{Vdt}}{L} = \frac{\text{VLEDx} \times \text{t}_{OFF}}{L} = \frac{\text{VLEDx} \times \frac{\text{LEDx}\_\text{TOFF}\_\text{DAC[7:0]}}{2.136 \times 10^6 \times \text{VLEDx}}}{L} = \frac{\text{LEDx}\_\text{TOFF}\_\text{DAC[7:0]}}{\text{L} \times 2.136 \times 10^6}$$

(3)

The final equation for the average LED current is then:

$$I_{LED} = \left[ \frac{LEDx\_PKTH\_DAC[7:0]}{1000 \times R_{SENSE}} \right] - \left[ \frac{LEDx\_TOFF\_DAC[7:0]}{2 \times L \times 2.136 \times 10^6} \right]$$

(4)

Because the control method relies on thresholds to control the main switch, offsets and delays must also be considered when examining the output accuracy. The  $I_{LED}$  equation can be expanded to include these error sources as shown in Equation 5.  $I_{LED}$  equations include several passive components, so it is important to consider the tolerance of each component. In this case the components are the main inductor and the sense resistor. The  $V_{CSTx\text{-}OFFSET}$  parameter is the variation in the  $V_{CSTx}$  threshold between the typical and maximum or minimum values as defined in the Electrical Characteristics. The peak current threshold delay ( $t_{DEL}$ ) and off timer trip point delay ( $t_{D-OFF}$ ) specifications are also shown in the Electrical Characteristics.

$$I_{LED} = \left(\frac{\frac{\text{LEDx\_PKTH\_DAC[7:0]}}{1000} \pm V_{CSTx-OFFSET}}{R_{SENSE}} \pm \frac{(V_{IN} - VLEDx) \times t_{DEL}}{L}\right) - \left(\frac{\frac{\text{LEDx\_TOFF\_DAC[7:0]}}{2.136 \times 10^6 \times VLEDx}}{2 \times L} \pm t_{D-OFF}\right) \times VLEDx}{2 \times L}$$

(5)

#### TEXAS INSTRUMENTS

#### **Feature Description (continued)**

#### 8.3.1.3 OFF Timer

The converter Off-time is controlled via the LEDx\_TOFF\_DAC[7:0] register and VLEDx pin. The VLEDx pin voltage is converted to a current that charges an internal capacitor to a voltage set by the LEDx\_TOFF\_DAC creating a delay. Details of this circuit are shown in the Functional Block Diagram. Deriving the off-time from the output voltage creates a ramp representing the inductor current.

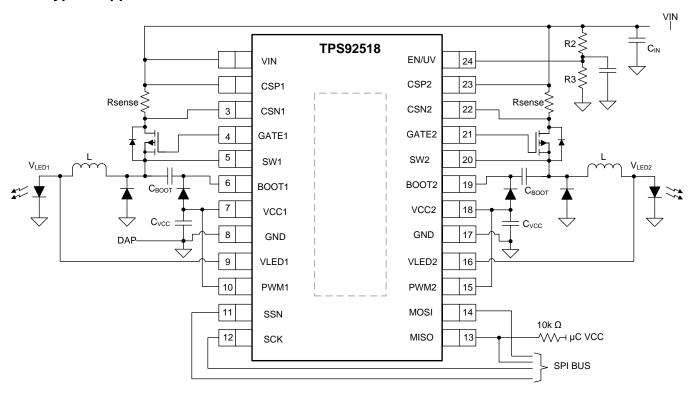

When the TPS92518 is first enabled (All UVLO levels are cleared) both timer capacitor pull-downs are disabled allowing voltage to increase on the internal timer capacitors. When either capacitor reaches the matching DAC control voltage, the high-side FET is turned on, starting a switching cycle. The maximum off-time timer is always dominant at start-up when the output is completely discharged or when shunt FET dimming and the shunt FET shunts the output for the required period.

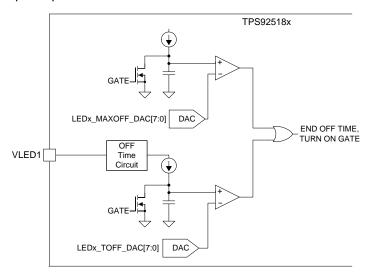

Figure 19. TPS92518 Simplified Internal Off-Timers Detail

#### 8.3.1.3.1 Off-time and Maximum Off-time Calculations

Circuitry in the TPS92518 adjusts the off-time to ensure a constant peak-to-peak ripple. The off-time follows the relationship defined by Equation 6

$$t_{OFF} = \frac{\text{LEDx}\_\text{TOFF}\_\text{DAC}[7:0]}{2.136 \times 10^6 \times \text{VLEDx}}$$

(6)

Or

$$t_{OFF} \times VLEDx = \frac{LEDx\_TOFF\_DAC[7:0]}{2.136 \times 10^{6}}$$

(7)

The maximum off-time circuit operates from its own independent current source that is not related to the VLEDx pin voltage. The equation for the maximum off-time is defined by Equation 8

$$Maximum Off-time (s) = LEDx \_MAXOFF \_DAC[7:0] \times \left(251 \times 10^{-9}\right)$$

(8)

#### 8.3.2 Important System Considerations: Off-Timer and Maximum Peak Threshold Values

To allow full application flexibility, controls have not been implemented to limit values written to any SPI register. The system firmware must ensure control of all register values, but these two in particular must have safeguards in place.

Two potential application architectures that may allow a register modification after system engineering is complete are:

A system has been engineered to allow firmware updates at a later time creating a situation where the Peak Current Threshold [LEDx\_PKTH\_DAC] value may be modified. The system LEDs can not support any higher

## **Feature Description (continued)**

than the designed current.

A system has been engineered to allow fine tuning of the register values during a calibration step in manufacturing.

Section Peak Current Sense Comparator and Off-Time Thresholds - LEDx\_TOFF\_DAC and LEDx MAXOFF DAC discuss a few of many system approaches to ensure values remain correct.

#### 8.3.2.1 Peak Current Sense Comparator

A comparator, two resistors and a current source create a peak current detection circuit block. See the *Functional Block Diagram* for details. A current source controlled by LEDx \_PKTH\_DAC[7:0] draws a current across a resistor in series with the comparator, forcing a proportional offset. The resistor in the current source (10 R) and in series with the comparator (R) are sized with a 10:1 ratio. This ratio allows for a practical voltage range of operation for the IADJ pin and maintains a small current sense voltage for low losses and less impact on efficiency. The ON cycle begins with the offset in place via IADJ across the resistor R at the VIN pin. When the current rises enough to create a voltage across the sense resistor to match the offset, the comparator trips. The end of the on-time period starts an off-time cycle.

Trace resistance can have an impact on accuracy, so care must be used when routing the traces to CSPx and CSNx from the sense resistor. Because the sense resistor value is typically in milli-ohms, use a short kelvin connection if possible.

#### 8.3.2.2 Peak Current Threshold - LEDx PKTH DAC

- Always use a current sense resistor sized so the full scale current occurs at or close to the maximum value of 255. This is also a good practice for accuracy.

- Impose a limit in firmware. Monitor the LEDxPKTH\_DAC variable before each write and ensure a maximum

value is maintained.

#### 8.3.2.3 Off-Time Thresholds - LEDx\_TOFF\_DAC and LEDx\_MAXOFF\_DAC

- Do not write '0' to the LEDx\_TOFF\_DAC or LEDx\_MAXOFF\_DAC registers. Writing a '0' to the LEDx\_TOFF\_DAC or LEDx\_MAXOFF\_DAC registers is the equivalent to: do not turn the FET off. Damage occurs to the device when a value of 0 is written to this register.

- Do not write an off-time value that causes the TPS92518 to operate beyond the maximum frequency possible for the conversion voltage ranges. For example: for a given application switching frequency and V<sub>IN</sub> to V<sub>LED</sub> conversion, there is a required duty cycle. If the duty cycle requirement is shorter than the TPS92518 minimum on-time (t<sub>LEB</sub>) current can not regulate. If the Off-time is made sufficiently short such that the inductor current is not able to reset given the V-s reached during the leading edge blanking time, the inductor current continues to increase until the inductor is saturated and the system may be damaged. The maximum frequency can be estimated, starting with Equation 9

$$\frac{V_{LED}}{V_{IN}} = \frac{t_{ON}}{T} = t_{ON} \times f_{SW}$$

(9)

Then the maximum frequency can be derived using the minimum on-time (t<sub>IFR</sub> leading edge blanking)

$$\frac{V_{\text{LED-MIN}}}{V_{\text{IN-MAX}}} = \frac{t_{\text{LEB}}}{T_{\text{MIN}}} = t_{\text{LEB}} \times f_{\text{SW-MAX}}$$

(10)

Using an example condition:  $V_{IN}$ = 65 V,  $V_{LED}$ = 6 V,  $t_{LEB}$ = 250 ns,  $\Delta I_{L-PP}$ = 250 mA, we can find the maximum switching frequency and an Off-time minimum value.

$$\frac{V_{LED-MIN}}{V_{IN-MAX}} = \frac{6 \text{ V}}{65 \text{ V}} = 250 \text{ ns x } f_{SW-MAX} \text{ then } f_{SW-MAX} = 369 \text{ kHz}$$

(11)

$$t_{OFF-MIN} = \frac{\Delta I_{L-PP} \ x \ L}{V_{LED}} = \frac{0.25 \ x \ 100 \ \mu H}{6} = 4.17 \ \mu s \quad \ then$$

LEDx\_TOFF\_DAC[7:0]<sub>MIN</sub> =

$$t_{OFF-MIN} \times V_{LED} \times 2.136 \times 10^6 = 53$$

(12)

## TEXAS INSTRUMENTS

#### **Feature Description (continued)**

The system controller must be programmed with a minimum LEDx\_TOFF\_DAC value of 55 allowing for some margin above the computed value of 53. (a smaller value = higher switching frequency) Note this is the correct value for this example. Each application is different. All register values, minimums and maximums must be considered for each application separately.

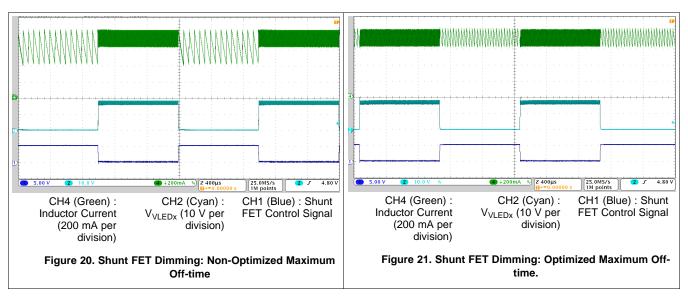

#### 8.3.3 Shunt FET or Matrix dimming: Maximum Off-timer Calculation

Shunt FET or Matrix dimming is typically used where precise control of the LED current is required. For the LED current and light output to most accurately match the control signal, the current source supplying the LEDs must be as close to ideal as possible. With the TPS92518 hysteretic control and maximum off-time setting, the LED current can approach ideal. Two waveforms show the result during shunt FET dimming with and without optimized maximum off-time control. The result with maximum off-time control is superior and approaches an ideal current source.

To ensure the correct maximum off-time when shunt dimming it is necessary to calculate the off-time required when the output is in the shunted condition. The following procedure may be used:

1. Estimate or measure the output voltage during the shunted condition.

$$V_{SHUNT} = FET_{RDS-ON_{MAX}} \times I_{LED}$$

(13)

Or for the Matrix approach:

$$V_{SHUNT} = R_{ALL(on)} \times I_{LED}$$

(14)

2. Compute the off-time required (t<sub>OFF-Shunt</sub>) when the output is shunted.

$$t_{OFF-Shunt} = \frac{\Delta I_{Lpk-pk} \times L}{V_{SHUNT} + (0.7)}$$

(15)

3. Compute the Maximum Off-time Register Value.

$$LEDx \_MAXOFF \_DAC[7:0] = \frac{Maximum \ Off-time(s)}{251 \times 10^{-9}}$$

(16)

#### 8.3.3.1 Output Ringing and TPS92518 Protection

During shunt dimming, ringing may occur at the channel output due to PCB and device parasitic capacitances and inductances. This should be checked as part of the design process. If the ringing approaches the absolute maximum of any pin, a clamping diode must be added to the design. Connect the diode anode to the output at VLEDx and the cathode to the input voltage. This protection must also be used if the LED load is ever to be connected or removed while the output is enabled.

**Feature Description (continued)**

## 8.3.3.2 Live Peak and Off-Time Threshold Changes

All TPS92518 thresholds may be changed at any time. Once the SPI transaction completes, the change is seen in operation in ~100ns.

#### 8.3.4 VIN and the VCC Internal Regulators

The device incorporates a linear regulator for each channel to generate the 7.5-V (typ) VCC voltage. Both VCC rails are powered from the VIN pin. VIN may be connected to the input of either channel or to a separate external supply. The VCC output voltages are internally monitored to implement undervoltage lockout (UVLO) protection for the respective channel. For example, if UVLO is reached on CH1, CH2 remains active. The VCC undervoltage lockout thresholds are fixed and cannot be adjusted.

The device has been designed to supply current for the device operation as well as additional power for external circuitry. If a 7.5-V rail is required in an application, the device can allow up to 500  $\mu$ A to be drawn in addition to the device load. A capacitance of 1  $\mu$ F or  $\geq$  10× the BOOT capacitance to a maximum of 10  $\mu$ F is recommended.

The device requires adequate input decoupling in order to lower  $\Delta V_{\text{IN-PP}}$  ripple for the best VCC supply voltage performance.  $\Delta V_{\text{IN-PP}}$  must not exceed 10% of the input voltage or 3V, whichever is lower.

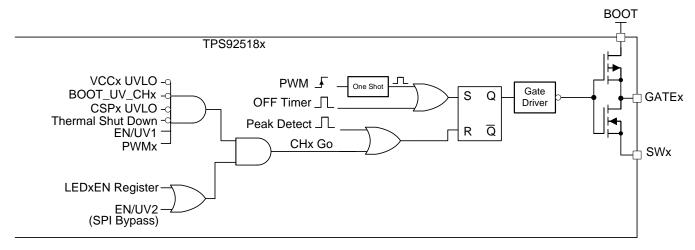

#### 8.3.5 Output Enable Control Logic

Several safeguards and control states must be satisfied before switching can begin as shown in Figure 22. VCC, BOOT and the CSP input must not be in under voltage lock-out. The device must not be in thermal shut-down and the EN/UV pin must be high. The PWM pin for the channel must also be high. It is not possible to override the PWM pin logic via the SPI interface. If PWM dimming is not required, tie the pins to VCC.

Figure 22. TPS92518 Output Enable Control

## 8.3.5.1 EN/UV2 - SPI Control Bypass

Note that the TPS92518 does allow a means to enable the part without SPI communication. By applying a voltage above the second threshold level, EN/UV2 (23.6 V typical), the state of the LEDxEN register is bypassed. This allows a TPS92518 to be powered and operated using the default register values (see Registers. A quick summary is that peak and off-time thresholds are set to 127 out of 255) without SPI communication. All other required operation points must still be satisfied as shown in Figure 22.

This could be useful in a manufacturing flow or during system troubleshooting. The logic path is highlighted again in Figure 23.

## TEXAS INSTRUMENTS

#### **Feature Description (continued)**

Figure 23. Output Enable Control Logic

#### 8.3.6 BOOT Capacitor and BOOT UVLO

The BOOT capacitor provides the power for the high-side gate drive circuitry. The capacitor is charged each cycle from VCC during the off-time phase of the switching cycle. During the off-time, the free-wheeling diode conducts, pulling the switchnode (SW) low and providing a conduction path to charge the capacitor. During the on-time, the current required to charge the high-side FET gate and power the driver are supplied by the capacitor.

A minimum boot capacitor can be calculated by considering: the MOSFET Qg, the driver quiescent current, and the desired nominal maximum on-time. Other factors include: the BOOT diode Vf, the minimum BOOT operation voltage, and the level of the switchnode (SWx) during the off-time. A rough estimate can be calculated using Equation 17: or just use  $0.1\mu F$ .

$$C_{\text{BOOT}} \ge \frac{Q_{\text{g}} + (I_{\text{Q}} \times T_{\text{ON}})}{V_{\text{CC}} - V_{\text{f(bd)}} - V_{\text{BOOT-UVLO(MAX)}} - V_{\text{SW(OFF)}}}$$

(17)

The variables are defined by:

Table 1. C<sub>BOOT</sub> Variables

| Variable                    | Description                                                         |

|-----------------------------|---------------------------------------------------------------------|

| $Q_g$                       | High-side FET total gate charge (Qg) as shown in the FET datasheet. |

| V <sub>CC</sub>             | 7.5 V                                                               |

| V <sub>SW(off)</sub>        | The switchnode voltage when the high-side FET is off. Use 0 V.      |

| V <sub>BOOT-UVLO(MAX)</sub> | 5.2 V                                                               |

| I <sub>BOOT-Q</sub>         | 200 μΑ                                                              |

| t <sub>ON</sub>             | Estimate your worst case on-time or use 500 µs                      |

| $V_{f(bd)}$                 | Forward drop of the boot diode                                      |

A typical solution calculates a minimum C<sub>BOOT</sub> of approximately 60 nF, justifying the 100 nF selection.

If conditions are created which cause the boot capacitor to become depleted (see *Drop-out Operation*) and reach  $V_{BOOT-UVLO}$ , switching is disabled until  $V_{BOOT}$  increases by  $V_{BOOT-UVLO-HYST}$ .

#### 8.3.7 Drop-out Operation

If the input or output voltage change such that they become close to the same value, a condition known as drop-out is created. During drop-out conditions the output LED current may fall out of regulation. If the input reaches the target output voltage or below, the LED current can drop to zero. There are two stages of drop-out when operating with a hysteretic device like the TPS92518. The two stages are described in Early Drop-Out (Boot Capacitor Voltage >>  $V_{BOOT-UVLO}$ ) and Early Drop-Out (Boot Capacitor Voltage reaching Early Drop-Out).

#### 8.3.7.1 Early Drop-Out (Boot Capacitor Voltage >> $V_{BOOT-UVLO}$ )

the first effects of drop-out can be seen when the input voltage approaches a few volts above the output voltage. Unless there is sufficient output capacitance, the change in the LED voltage during the ramp up of the inductor and output current can cause a non-linearity in the ramp.

www.ti.com SLUSCR7 – MAY 2017

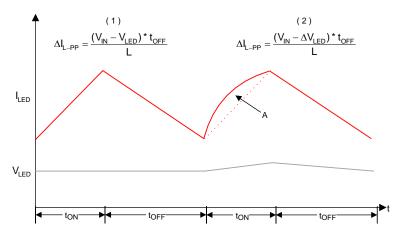

Figure 24. Inductor on-time Current Non-linearity

In case (1) shown in ,  $V_{IN}$ - $V_{LED}$  is sufficiently large that variations in  $V_{LED}$  are not relevant and/or not present because of sufficient output capacitance.

In case (2),  $V_{IN}$  and  $V_{LED}$  are closer in value making the difference lower and more easily affected by variations in  $V_{LED}$ .  $\Delta V_{LED}$  is the total variation in the voltage across the inductor and includes the  $I_{LED}$  x  $R_{L-DCR}$  voltage drop which also changes with  $I_L$  and impacts the inductor current linearity. The combination of factors leads to an inductor current on-time non-linearity which increases the average value of the inductor current, and hence the LED current. This means the first affect of approaching drop-out is always an increase in LED current.

It is important to note that the output current is always limited to the peak limit set by the internal programmed reference and the sense resistor. (The peak current threshold) This means a design having a smaller overall inductor current ripple (smaller  $\Delta I_{L-PP}$ ) will have less error when a drop-out condition occurs.

## 8.3.7.2 Full Drop-Out (Boot Capacitor Voltage reaching V<sub>BOOT-UVLO</sub>)

If  $V_{\text{IN}}$  and  $V_{\text{LED}}$  are sufficiently close the duty cycle demand increases. Because of the TPS92518 hysteretic control method, the high-side FET attempts to remain ON until the programmed peak current is reached. Keeping the high-side FET ON requires energy from the BOOT capacitor which depletes the BOOT capacitor voltage. If the high-side FET is ON for sufficient duration, the BOOT capacitor voltage eventually reaches  $V_{\text{BOOT-UVLO}}$  level at which point the high-side FET is turned off. This allows for long on-times and duty cycles >99.5%, since the time the high-side FET can remain ON is long (>1 ms) compared to the time required the recharge the BOOT capacitor (approximately 100 ns). The typical maximum on-time can be estimated by Equation 18

$$t_{ON-MAX_{(TYP)}} = \frac{C \, dv}{i} = \frac{C_{BOOT} \, x \, (V_{CC} - V_{BOOT-UVLO})}{I_{BOOT-Q}} \approx \frac{0.1 \, \mu F \, x \, (7.5 - 4.6)}{100 \, \mu A} \approx 2.9 \, ms \tag{18}$$

#### 8.3.7.3 Minimum BOOT Voltage and FET Control

The minimum  $V_{BOOT\text{-}UVLO}$  is also the minimum voltage available to drive the external FET. Check the FET Output Characteristics ( $I_D$  versus  $V_{DS}$ ) at the minimum BOOT voltage and ensure the FET is sufficiently enhanced under this condition. If the turn-on is marginal, the FET may operate in the linear region causing increased losses and possibly damage the device.

#### 8.3.7.4 BOOT Controlled internal Pull-Down

Copyright © 2017, Texas Instruments Incorporated

Each time  $V_{BOOT-UVLO} \le V_{BOOT-UVLO}$  an internal pull-down ( $I_{PD} \ BOOT_x = 5$  mA typical) from the SWx pin to ground is enabled. This behavior occurs during drop-out conditions such as *Full Drop-Out (Boot Capacitor Voltage reaching V\_{BOOT-UVLO})*. This behavior also occurs at Start-Up if the output is pre-charged.

If the TPS92518 application uses an output capacitor and the output is disabled and re-enabled before the output voltage reduces (or is otherwise pre-charged) a condition can be created where the SWx pin voltage is not low enough for the BOOT capacitor to charge. ( $V_{SWx} << V_{CC}$ ) BOOT-UV is then activated and the internal pull-down circuitry enabled. The pull-down circuitry reduces the time required to deplete the output voltage to allow the BOOT capacitor to be charged. Note that the internal pull-down circuitry can not act as a synchronous FET.

#### 8.3.8 Analog and PWM Dimming

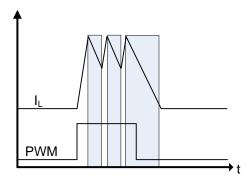

#### 8.3.8.1 Dimming Methods

The TPS92518 has been designed to support three dimming methods. Analog, PWM and Shunt-FET or Matrix (TPS92661/TPS92662 device family) dimming. Analog dimming is still accomplished via the SPI interface through adjustment of the LEDx\_PKTH\_DAC register. PWM dimming is accomplished by using the PWMx pin. Shunt-FET or Matrix Dimming is optimized by using the LEDx\_MAXOFF\_DAC register. One or more dimming methods may also be combined to obtain extreme contrast ratios. To obtain an ultra-fine adjustment, the LEDxTOFF\_DAC register may be also adjusted allowing average output current modifications in the range of 100 µA per LSB.

#### 8.3.8.2 PWMx Pin Operation

PWM dimming can be used to adjust the output brightness by changing the applied PWM duty cycle to a channels' corresponding PWM pin. Each channel can be controlled with an independent frequency and duty cycle.

When the PWM pin signal is < 0.8 V, the corresponding channel's gate logic is disabled. When PWM rises above 1.6 V the rising edge sets the gate drive latch and turns on the FET. If PWM dimming is not required, PWMx be tied to VCC.

Treat the PWM pin as a digital input. Avoid slow transitions of the pin voltage level around the logic thresholds. Ensure the signal edge rate is adequate (<100ns) when measured at the device PWMx pin to prevent false level interpretations. If the edge is too slow, a small capacitor may be required. If the PWM pin edge rate is too slow and is not adequately decoupled, the TPS92518 PWM pin logic may interpret one transition as multiple ON-OFF transitions. This can cause the output current to ratchet beyond the desired set-point and possibly cause the system to be damaged.

Figure 25. Gate Control Logic

#### 8.3.8.3 PWM Dimming - Current Rise Performance

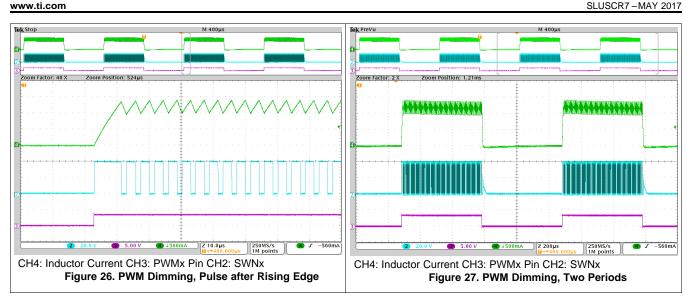

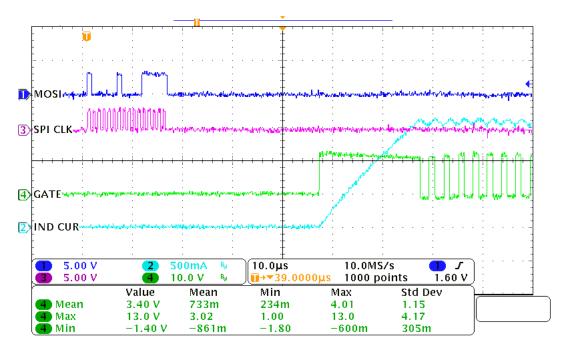

A unique feature of the TPS92518 hysteretic control allows the first switching pulse of a PWM dimming on-time to rise completely to the correct peak current in one switching cycle. An example is shown in Figure 26. When the rising edge of the PWM signal is seen by the PWMx pin the main FET is turned on. The FET remains ON until the programmed peak current threshold is reached. Once reached, switching continues until the PWMx pin voltage goes low. The TPS92518 can also operate when using pulse widths that are sufficiently narrow that the programmed peak is not reached. The on-time is terminated at the end of the PWM pulse and another on-time initiated when the PWMx pin goes high again.

!~

#### 8.3.8.4 PWM and Analog Dimming - Linearity Limitations and Buck Converters

#### 8.3.8.4.1 PWM:

A linearity limitation occurs at very small PWM duty cycles; the PWM dimming on-time becomes short enough that it contains only one or a few switching cycles. If the PWMx pulse falls during an off-time (see Figure 28), the pulse length is not able to change because the switch is already off. This can lead to a small 'stair-case' dimming curve in this region as the duty cycle affects the average current during on-times and then not during off-times. This situation can be improved by increasing the switching frequency. This limitation is common to all Buck converters during very small PWM dimming duty cycles.

Shunt FET PWM dimming avoids this issue as the average current is affected during switching ON and OFF times. Shunt FET PWM dimming can out-perform PWM dimming, but is more complicated to implement.

Figure 28. PWM Dimming Limitation

#### 8.3.8.4.2 ANALOG:

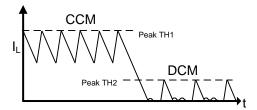

Another impact on linearity can occur when analog dimming (LEDx\_PKTH\_DAC threshold adjustment) and the inductor current becomes discontinuous. Discontinuous conduction mode (DCM) occurs when the inductor current reaches 0 A each off-time. When the device enters DCM, the output current is no longer the peak current minus half the ripple current (as shown in Figure 16) and is no longer a linear relationship between the LEDx PKTH DAC value and the average output current. The linear range can be extended by lowering the ripple,  $\Delta I_{1-PP}$  to extend the natural linear region of operation.

Figure 29. Analog Dimming Limitation

Another approach can be used by first analyzing the system operation. The point at which DCM is entered can be calculated as well as the average current value when in DCM. The micro-controller writing the LEDx PKTH DAC values can simply write alternate values in the DCM area to ensure net linear response to the LED average current. See DCM Current Calculation for information on calculating the average current when in DCM.

#### 8.3.8.5 DCM Current Calculation

The converter is considered to be operating in DCM (Discontinuous conduction mode) when the peak current is less than the peak-to-peak inductor current ripple. ( $I_{L(pk)} < \Delta I_{L-PP}$ ). Equations Equation 20 through Equation 25 define the calculation described by Equation 19. Note that the value of the LED voltage is different when operating in DCM.

Starting with the basic equation for a buck converter in DCM:

$$I_{LED_{DCM}} = \frac{D_1 \times T}{2 \times L} \times (D_1 + D_2) \times (V_{IN} - VLEDx)$$

(19)

followed by: ( $\eta$  is the estimated converter efficiency):

$$D_{1} = \frac{1}{1 + \left[\frac{t_{OFF} \times ((V_{IN} \times \eta) - VLEDx)}{L \times I_{Lx-peak}}\right]}$$

(20)

$$D_2 = \frac{I_{Lx-peak} \times L}{T_{DCM} \times VLEDx}$$

(21)

Where T defines the switching converter period.

$$T_{DCM} = t_{ON-DCM} + t_{OFF}$$

(22)

$$t_{ON-DCM} = \frac{I_{Lx-peak} \times L}{V_{IN} - VLEDx}$$

(23)

$$t_{OFF} = \frac{LEDx\_TOFF\_DAC[7:0]}{2.136 \times 10^6 \times VLEDx}$$

$$l_{Lx-peak} = \frac{LEDx\_PKTH\_DAC[7:0]}{1000 \times R_{SENSE}}$$

(24)

$$I_{Lx-peak} = \frac{1000 \times R_{SENSE}}{1000 \times R_{SENSE}}$$

(25)

See Equation 4 for the CCM (continuous current mode) equation.

#### 8.3.8.6 Current Sharing

The TPS92518 can be configured to operate as a Two Channel, Single Output converter by configuring each channel identically and connecting the outputs together. Figure 30 illustrates the current sharing capability with each channel handling approximately the equal share of the output current load. Statistics are enabled and the average inductor current of each channel is also shown. The total output current for this configuration is 438 mA. Note that both channels must be enabled at the same time to allow charging of the boot capacitors. When a channel is paralleled, it may not be enabled after the first channel is enabled.

TPS92518 Channel 1 and 2 Outputs Connected in Parallel.

216.0mA

CH4 (Green): Inductor Current (100 mA per division) CH1 (Blue): SW1 Node (50 V per division)

212.0m

220.0m

2.112m 380µ

CH2 (Cyan): Inductor Current (100 mA per division)

Max

Figure 30. TPS92518 Channels Connected to Current Share

#### 8.3.9 VIN and CSPx Pin Configuration

The TPS92518 has been designed to support single or dual input voltage sources. The VIN pin connection is also flexible and may be connected to the input supply of either channel or from a third independent channel.

The Electrical Characteristics table defines  $CSP_{UVLO}$  as the minimum voltage required by a channel to continue operating. This limit is set regardless of the VIN and VCCx voltages. The VIN pin does not have an under voltage lock-out level, but must support the VCCx voltage for the channel. The minimum VIN pin voltage is limited to 6.5 V because two items depend on the voltage level for operation that have their own UVLO (under voltage lock-out) levels: VCCx and BOOTx. The 6.5-V level is derived from the maximum  $V_{CCx\_UVLO}$  level with some added margin. Alternately the maximum  $V_{BOOT-UVLO}$  level may be used. If we consider this level and add the drop of the boot diode, we obtain the same value and with some margin obtain the same VIN pin minimum level of 6.5 V.

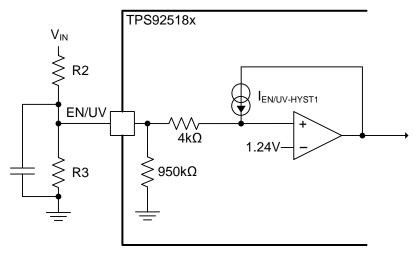

#### 8.3.10 Enable and Undervoltage Lock-out Configuration

If drop-out operation is not desired, configure a resistor divider to disable switching of both channels at the desired input voltage.

The value of resistors R2 and R3 establish the undervoltage lockout level as shown in Figure 31. Include a small level of capacitance (approximately 0.1  $\mu$ F) at the UVLO pin for noise immunity. If the application does not require drop-out operation (operation when  $V_{VIN}$  approximates  $V_{VLEDx}$ ) program a UVLO level that allows no switching to occur until there is adequate input voltage available.

Figure 31. EN/UV Programming Resistors

Select the desired amount of voltage hysteresis and the desired turn-ON threshold ( $V_{IN-RISE\_THRESHOLD}$ ). Because of the small amount of fixed-voltage hysteresis and fixed-hysteresis current, some combinations of turn-ON and turn-OFF thresholds are not possible. If the calculation results in values that are zero or negative, the combinations selected are not possible. After selecting a turn-ON point and desired amount of voltage hysteresis ( $V_{HYST}$ ) use Equation 26 and Equation 27 to calculate R3 and R2.

$$R_{2} = \frac{V_{\text{HYST}} - \left[ \frac{0.1 \, \text{x} \, V_{\text{IN-RISE\_THRESHOLD}} - 0.124}{1.24} \right] - 0.1}{18 \, \text{x} \, 10^{-6}}$$

$$R_{3} = \frac{1.24 \, (R_{2})}{V_{\text{IN-RISE\_THRESHOLD}} - 1.24}$$

(26)

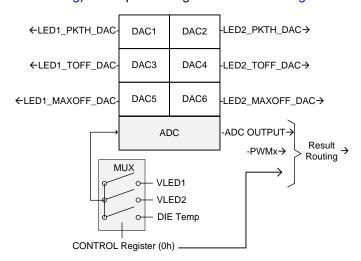

## 8.3.11 Voltage Sampling and DAC Operation

The TPS92518 integrates an ADC (analog to digital converter) and 6 DACs (digital to analog converters). The single ADC is multiplexed to provide the VLEDx pin voltages (starting with: *LED1 Voltage*) and the TPS92518 die temperature (*Die Temperature Reading*). A simplified diagram is shown in Figure 32.

Figure 32. TPS92518 Internal Digital Blocks

#### 8.3.11.1 ADC Control and LED Voltage Updating

Each of the analog outputs are controlled via their own individual DAC. The DAC's operate asynchronously and changes to controlling register values are updated immediately (~1 µs).

The ADC (analog to digital converter) sampling intervals are asynchronous to the incoming PWM1 and PWM2 signals. The TPS92518 logic determines which register(s) to update based on the state of the corresponding PWM signal at the time of ADC sampling. There are three LED voltage registers per channel:

- LEDx MOST RECENT

- LEDx LAST ON

- LEDx LAST OFF

The LEDx\_MOST\_RECENT registers are updated periodically every time the ADC has a new sample. Sampling a single input increases the sampling frequency. For example: an ADC sample and conversion requires ~100us. If one item is selected it is sampled at roughly 10 kHz. If all three inputs are selected each is sampled at ~3.3 kHz.

The LEDx\_LAST\_ON registers are only updated when the corresponding PWM input has toggled from high to low, and the LEDx\_LAST\_OFF registers are only updated when the corresponding PWM input has toggled from low to high. This allows the last sample before the falling edge of PWM to be saved as the LAST\_ON value, and the last sample before the rising edge of PWM to be saved as the LAST\_OFF value ensuring the most consistent LED voltage reading.

#### 8.3.12 Device Functional Modes

#### 8.3.12.1 Analog Dimming

Analog dimming refers to the method of controlling the peak inductor current as the method to set the continuous average output current. Analog dimming is controlled digitally via the SPI interface. The register control value is converted via a digital to analog converter and the peak inductor current is compared to this analog voltage level. The level can be updated at any time during operation.

#### 8.3.12.2 **PWM Dimming**

PWM Dimming is accomplished via a channel's corresponding PWM pin. A 1.6-V (typical) rising threshold and a 0.8-V (typical) falling threshold are required.

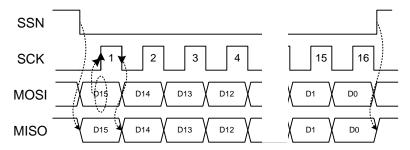

#### 8.4 Serial Interface

The 4-wire control interface is compatible with the Serial Peripheral Interface (SPI) bus. The control bus consists of four signals: SSN, SCK, MOSI, and MISO. The SSN, SCK, and MOSI pins are TTL inputs into the TPS92518 while the MISO pin is an open-drain output. The SPI bus can be configured for both star-connect and daisy chain hardware connections.

A bus transaction is initiated by a MCU on a falling edge of SSN. While SSN is low, the input data present on the MOSI pin is sampled on the rising edge of SCK, MSbit first. The output data is asserted on the MISO pin at the falling edge of SCK. The figure below shows the data transition and sampling edges of SCK.

A valid transfer requires a non-zero integer multiple of 16 SCK cycles (i.e., 16, 32, 48, etc.). If SSN is pulsed low and no SCK pulses are issued before SSN rises, a SPI error is reported. Similarly, if SSN is raised before the 16th rising edge of SCK, the transfer is aborted and a SPI error is reported. If SSN is held low after the 16th falling edge of SCK and additional SCK edges occur, the data continues to flow through the TPS92518 shift register and out the MISO pin. When SSN transitions from low-to-high, the internal digital block decodes the most recent 16 bits that were received prior to the SSN rising edge.

SSN must transition high only after a multiple of 16 SCK cycles for a transaction to be valid and not set the SPI error bit. In the case of a write transaction, the TPS92518 logic performs the requested operation when SSN transitions high. In the case of a read transaction, the read data is transferred during the next frame, regardless of whether a SPI error has occurred.

## TEXAS INSTRUMENTS

#### Serial Interface (continued)

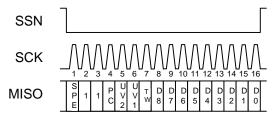

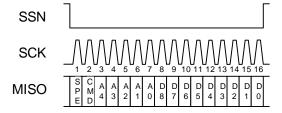

Figure 33. SPI Data Format

The data bit on MOSI is shifted into an internal 16-bit shift register (MSbit first) while data is simultaneously shifted out the MISO pin. While SSN is high (bus idle), MISO is tri-stated by the open-drain driver. While SSN is low, MISO is driven according to the 16-bit data pattern being shifted out based on the prior received command. At the falling edge of SSN to begin a new transaction, MISO is driven to the MSbit of the outbound data, and is updated on each subsequent falling edge of SCK.

#### **NOTE**

The first MISO transition happens on the first falling edge AFTER the first rising edge of SCK.

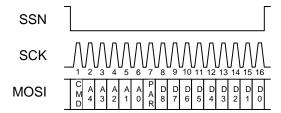

#### 8.4.1 Command Frame

There is only one defined format for frames coming in on MOSI from the master. These are called Command frames. A Command frame can be either a read command or a write command.

A Command frame consists of a CMD bit, five bits of ADDRESS, a PARITY bit (odd parity), and nine bits of DATA. The format of the Command frame is shown in Figure 34. The bit sequence is as follows:

- 1. The COMMAND bit (CMD). CMD = 1 means the transfer is a write command; CMD = 0 means it is a read command.

- 2. The five-bit read or write ADDRESS (A4..A0).

- 3. The PARITY bit (PAR). This bit is set by the following equation: PARITY = XNOR(CMD, A4..A0, D8..D0).

- 4. Nine bits of read or write DATA (D8..D0). For a read, all data bits must be 0.

Both the Read Command and the Write Command follow the Command frame format as shown in Figure 34.

Figure 34. Command Frame Format

#### 8.4.2 Response Frame Formats

There are three possible response frame formats: Read Response, Write Response and Write Error/POR. These formats are further described below.

## Serial Interface (continued)

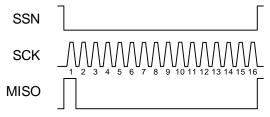

#### 8.4.2.1 Read Response Frame Format

The Read Response frame has the following format. The read response frame contains the state of the four fault bits. A special command is not required to poll the status of the bits, they are returned in every read response.!—

- 1. The SPI Error bit (SPE).

- 2. Two reserved bits (always 1).

- 3. The POWER CYCLED bit PC).

- 4. The LED2 BOOTUV ERROR bit (UV2).

- 5. The LED1 BOOTUV ERROR bit "UV1).

- 6. The THERMAL WARNING bit (TW).

- 7. Nine bits of DATA (D8..D0).

This is shown in Figure 35 below. This frame is sent out by the TPS92518 following a read command.

Figure 35. Read Response Frame Format

#### 8.4.2.2 Write Response Frame Format

The Write Response frame has the following format:

- 1. The SPI Error bit (SPE).

- 2. The COMMAND bit (CMD).

- 3. Five bits of ADDRESS (A4..A0).

- 4. Nine bits of DATA (D8..D0).

This is shown in Figure 36. This frame is sent out following a write command if the previously received frame was a write command and no SPI Error occurred during that frame.

Figure 36. Write Response Frame Format

## TEXAS INSTRUMENTS

#### Serial Interface (continued)

#### 8.4.2.3 Write Error/POR Frame Format

The Write Error/POR frame is simply a '1' in the MSB, followed by all zeroes (see Figure 37) This frame is sent out by the TPS92518 Internal digital block during the first SPI transfer following power-on reset, or following a write command with a SPI Error.

Figure 37. Write Error/POR

#### 8.4.2.4 SPI Error

The TPS92518 records a SPI Error if any of the following conditions occur:

- The SPI command has a non-integer multiple of 16 SCK pulses.

- Any of the DATA bits during a read command are non-zero.

- There is a parity error in the previously received command.

If any of these conditions are true, the TPS92518 sets the SPI\_ERROR bit in the Status Register. This is reported by setting the SPE (MSbit) in the next response frame. A write command with a SPI Error (not 16-bit aligned or bad parity) does NOT write to the register being addressed. The bad write is ignored and discarded. The TPS92518 attempts to respond to read requests regardless of SPI Error status since there is no danger to the system.

The SPI\_ERROR bit can be cleared by reading the STATUS register.

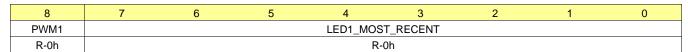

#### 8.5 Registers