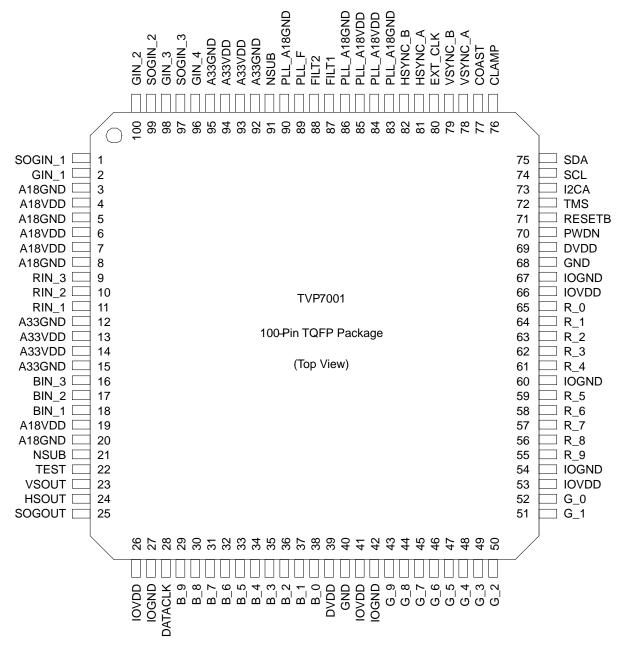

TVP7001

SLES164-FEBBRUARY 2006

## **FEATURES**

**Analog Channels**

ISTRUMENTS www.ti.com

- -6 dB to 6 dB Analog Gain

- Analog Input MUXs

- Auto Video Clamp

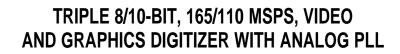

- Three Digitizing Channels, Each With Independently Controllable Clamp, PGA, and ADC

- Clamping: Selectable Clamping Between Bottom Level and Mid-level

- Offset: 1024-Step Programmable RGB or YPbPr Offset Control

- PGA: 8-Bit Programmable Gain Amplifier

- ADC: 8/10-Bit 165/110 MSPS A/D Converter

- Automatic Level Control Circuit

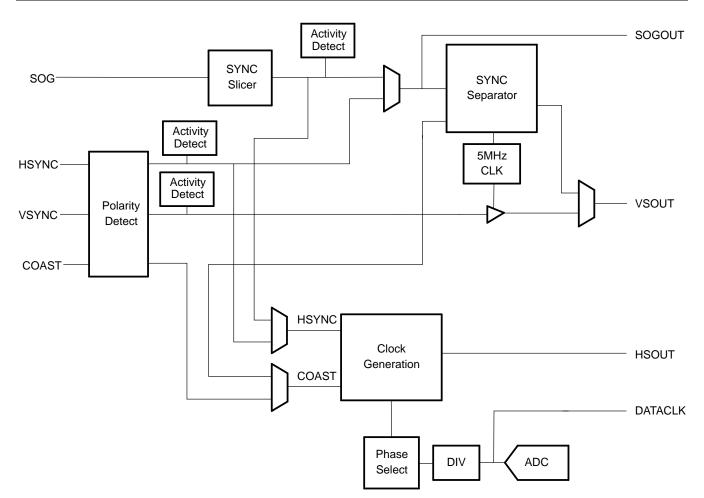

- Composite Sync: Integrated Sync-on-Green Extraction From GreenLuminance Channel

- Support for DC and AC-Coupled Input Signals

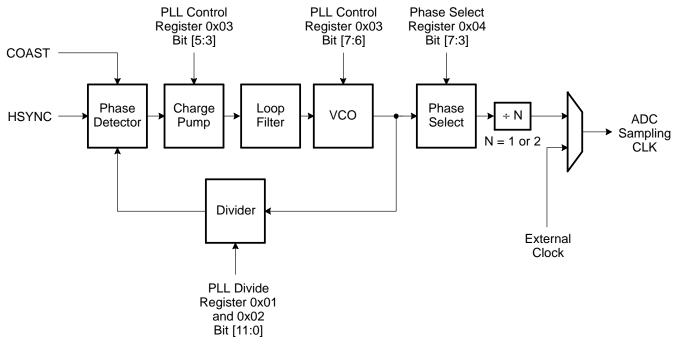

- PLL

- Fully Integrated Analog PLL for Pixel Clock Generation

- 12-165 MHz Pixel Clock Generation From **HSYNC Input**

- Adjustable PLL Loop Bandwidth for **Minimum Jitter**

- 5-Bit Programmable Subpixel Accurate **Positioning of Sampling Phase**

- **Output Formatter**

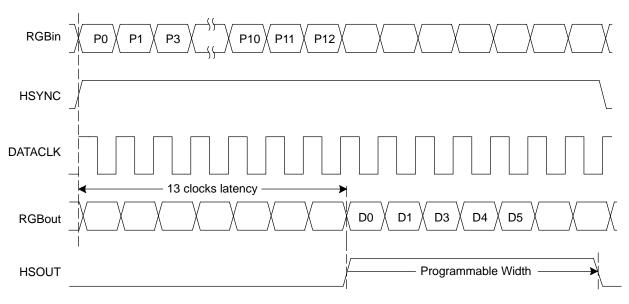

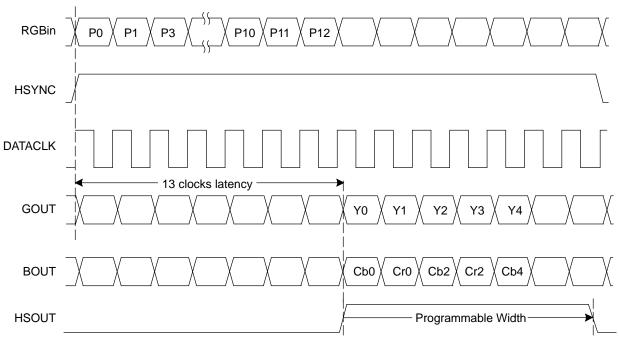

- Support for RGB/YCbCr 4:4:4 and YCbCr 4:2:2 Output Modes to Reduce Board Traces

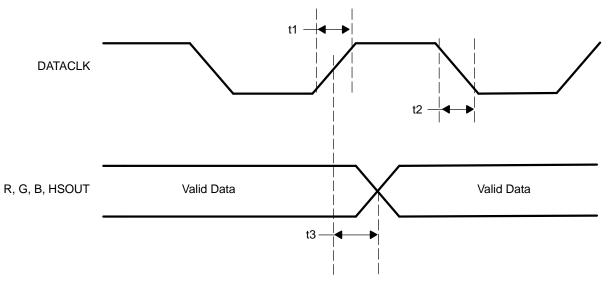

- Dedicated DATACLK Output for Easy Latching of Output Data

- System

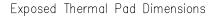

- Industry-Standard Normal/Fast I<sup>2</sup>C Interface With Register Readback Capability

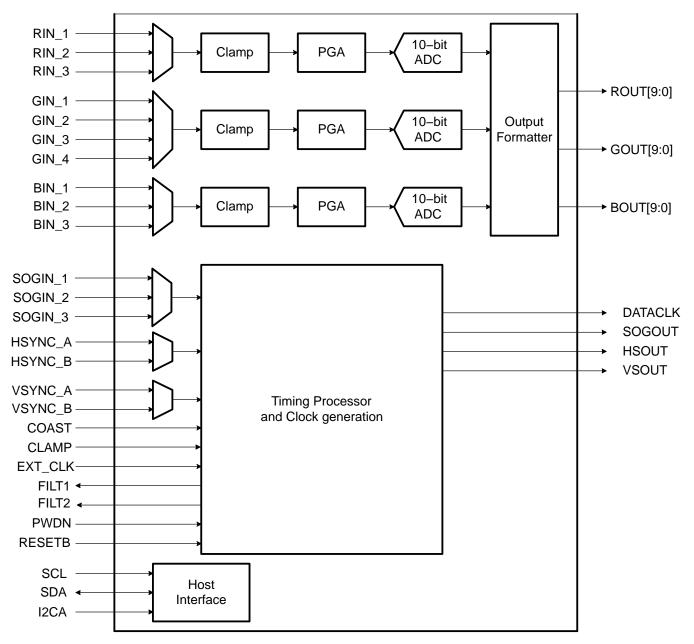

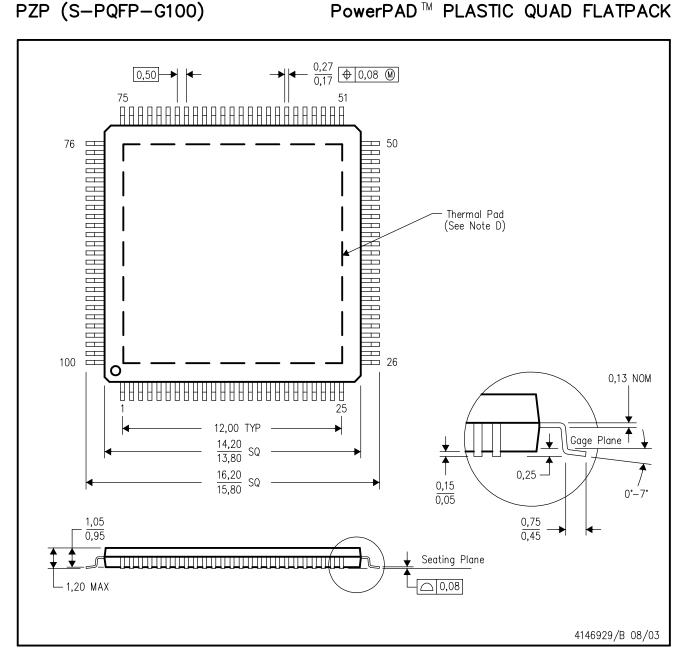

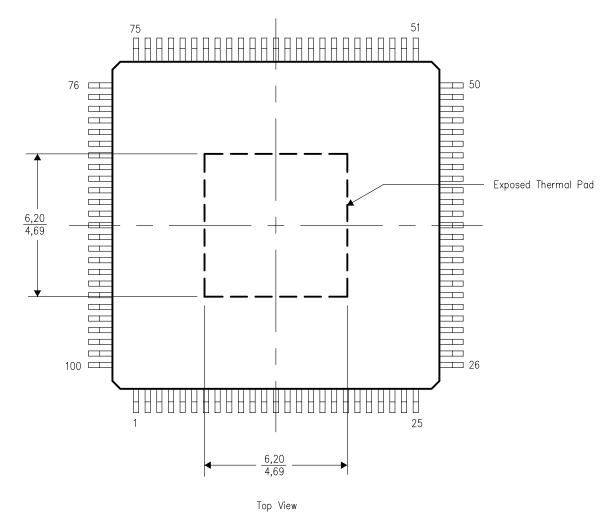

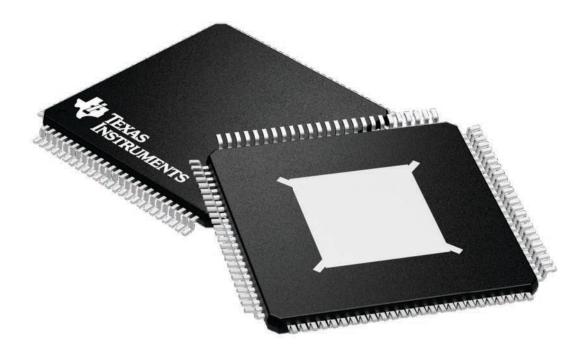

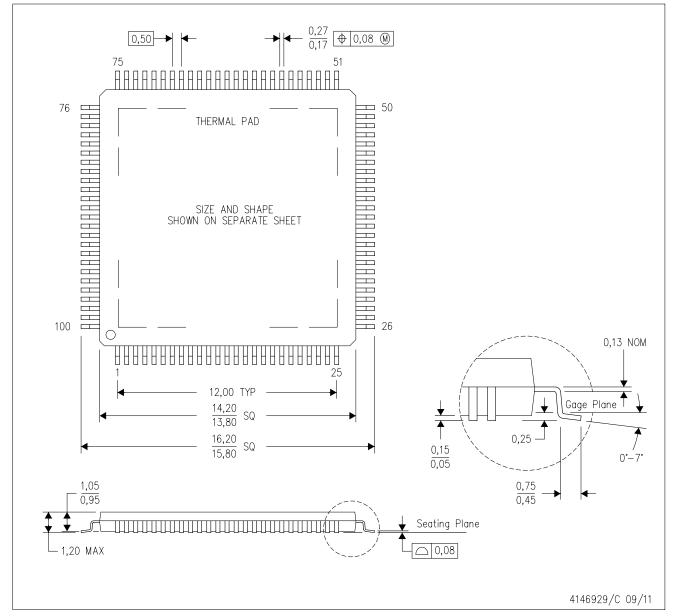

- Space-Saving TQFP-100 Pin Package

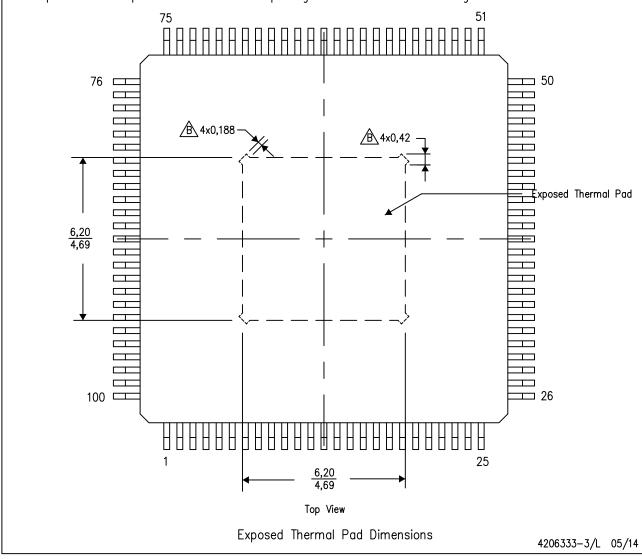

- Thermally-Enhanced PowerPAD<sup>™</sup> Package for Better Heat Dissipation

## APPLICATIONS

- LCD TV/Monitors/Projectors

- **DLP TV/Projectors** •

- **PDP TV/Monitors** .

- **PCTV Set-Top Boxes** •

- **Digital Image Processing**

- Video Capture/Video Editing

- Scan Rate/Image Resolution Converters •

- Video Conferencing •

- **Video/Graphics Digitizing Equipment**

## DESCRIPTION

TVP7001 is a complete solution for digitizing video and graphic signals in RGB or YPbPr color spaces. The device supports pixel rates up to 165 MHz. Therefore, it can be used for PC graphics digitizing up to the VESA standard of UXGA (1600  $\times$  1200) resolution at 60 Hz screen refresh rate, and in video environments for the digitizing of digital TV formats, including HDTV up to 1080p. TVP7001 can be used to digitize CVBS and S-video signal with 10-bit ADCs.

The TVP7001 is powered from 3.3-V and 1.8-V supply and integrates a triple high-performance A/D converter with clamping functions and variable gain, independently programmable for each channel. The clamping timing window is provided by an external pulse or can be generated internally. The TVP7001 includes analog slicing circuitry on the Y or G input to support sync-on-luminance or sync-on-green extraction. In addition, TVP7001 can extract discrete HSYNC and VSYNC from composite sync using a sync slicer.

TVP7001 also contains a complete analog PLL block to generate a pixel clock from the HSYNC input. Pixel clock output frequencies range from 12 MHz to 165 MHz.

All programming of the part is done via an industry-standard I<sup>2</sup>C interface, which supports both reading and writing of register settings. The TVP7001 is available in a space-saving TQFP 100-pin PowerPAD package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

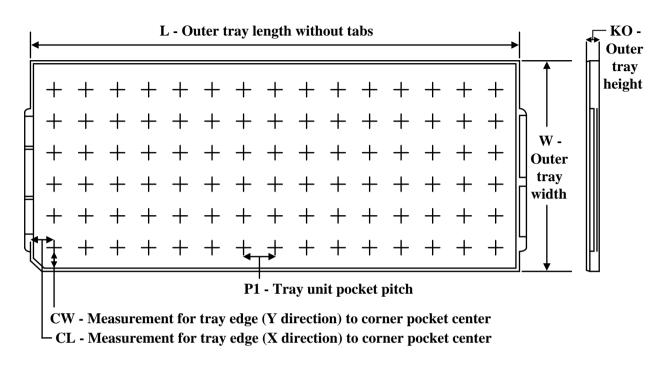

| ORDERING INFORMATION |                                    |                |  |  |  |  |  |  |

|----------------------|------------------------------------|----------------|--|--|--|--|--|--|

| т                    | PACKAGED DEVICES                   | PACKAGE OPTION |  |  |  |  |  |  |

| T <sub>A</sub>       | 100-PIN PLASTIC FLATPACK PowerPAD™ | PACKAGE OPTION |  |  |  |  |  |  |

| 0°C to 70°C          | TVP7001PZP                         | Tray           |  |  |  |  |  |  |

|                      | TVP7001PZPR                        | Reel           |  |  |  |  |  |  |

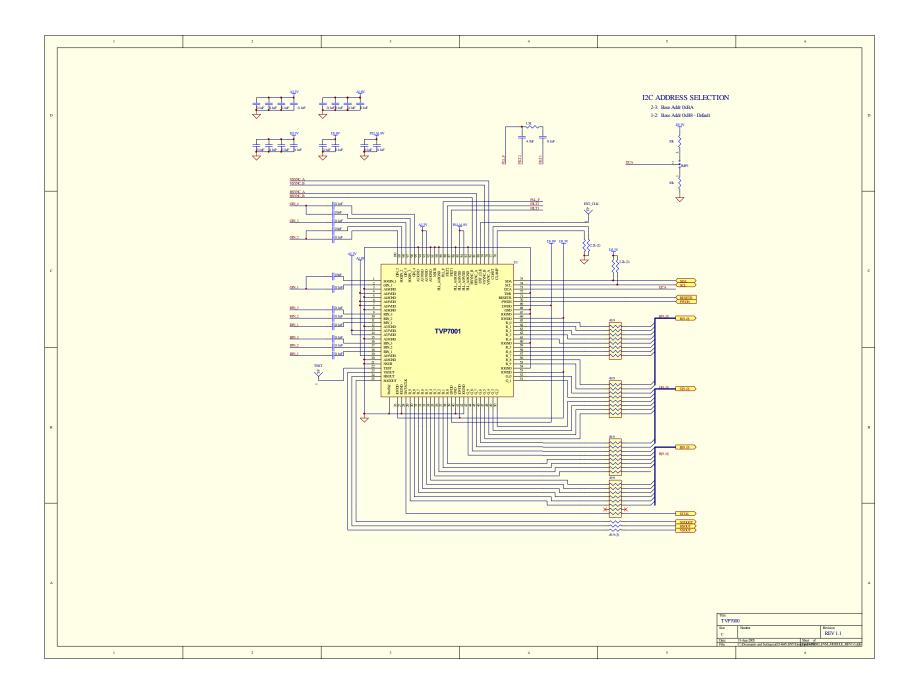

#### FUNCTIONAL BLOCK DIAGRAM

## TEXAS INSTRUMENTS www.ti.com

#### **TERMINAL FUNCTIONS**

| TERMINAL                                                                                              |                                                         |             | DECODIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                  | NO.                                                     | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ANALOG VIDE                                                                                           | D                                                       | I.          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

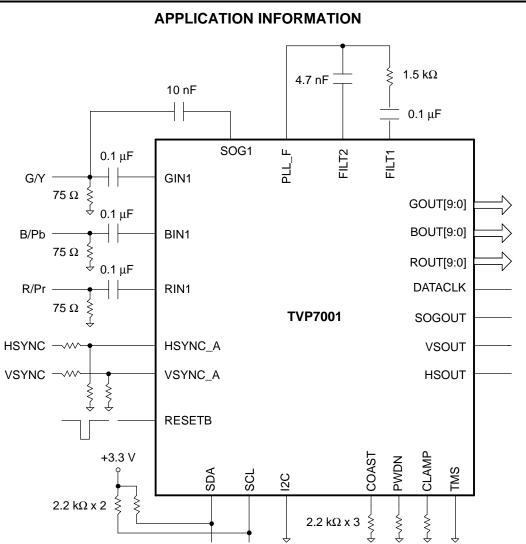

| RIN_1<br>RIN_2<br>RIN_3<br>GIN_1<br>GIN_2<br>GIN_3<br>GIN_4<br>BIN_1<br>BIN_2<br>BIN_3<br>CLOCK SIGNA | 11<br>10<br>9<br>2<br>100<br>98<br>96<br>18<br>17<br>16 |             | Analog video input for R/Pr 1<br>Analog video input for R/Pr 2<br>Analog video input for R/Pr 3<br>Analog video input for G/Y 1<br>Analog video input for G/Y 2<br>Analog video input for G/Y 3<br>Analog video input for G/Y 4<br>Analog video input for B/Pb 1<br>Analog video input for B/Pb 2<br>Analog video input for B/Pb 3<br>The inputs must be AC coupled. The recommended coupling capacitor is 0.1 µF. Unused analog<br>inputs should be connected to ground using a 10 nF capacitor. |

| DATACLK                                                                                               | 28                                                      | 0           | Data clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EXT_CLK                                                                                               | 80                                                      | 1           | External clock input for free running mode                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TEST                                                                                                  | 22                                                      | 0           | Internal 5 MHz clock output, coast output, high-Z, or SOG output                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DIGITAL VIDEO                                                                                         |                                                         | _           | ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ROUT [9:0]<br>GOUT [9:0]<br>BOUT [9:0]                                                                | 55–59, 61–65<br>43-52<br>29-38                          | 0<br>0<br>0 | Digital video output of R/Cr, ROUT [9] is MSB.<br>Digital video output of G/Y, GOUT [9] is MSB.<br>Digital video output of B/Cb, BOUT [9] is MSB. For a 4:2:2 mode BOUT outputs CbCr data.<br>Unused outputs can be left unconnected.                                                                                                                                                                                                                                                             |

| MISCELLANEO                                                                                           | US SIGNALS                                              | Į.          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PWDN                                                                                                  | 70                                                      | Ι           | Power down input. 1: Power down 0: Normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

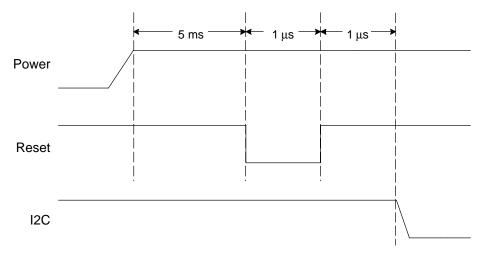

| RESETB                                                                                                | 71                                                      | Ι           | Reset input, active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TMS                                                                                                   | 72                                                      | I           | Connect to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

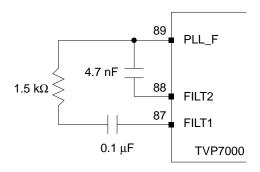

| FILT1                                                                                                 | 87                                                      | 0           | External filter connection for PLL. The recommended capacitor is 0.1 $\mu\text{F}.$ see Figure 4                                                                                                                                                                                                                                                                                                                                                                                                  |

| FILT2                                                                                                 | 88                                                      | 0           | External filter connection for PLL. The recommended capacitor is 4.7 nF. See Figure 4                                                                                                                                                                                                                                                                                                                                                                                                             |

| HOST INTERFA                                                                                          | CE                                                      | 1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sup>2</sup> C A                                                                                    | 73                                                      | I           | I <sup>2</sup> C Address input                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SCL                                                                                                   | 74                                                      | I           | I <sup>2</sup> C Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SDA                                                                                                   | 75                                                      | I/O         | I <sup>2</sup> C Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| POWER SUPPL                                                                                           | -                                                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NSUB                                                                                                  | 21, 91                                                  | <br>        | Substrate ground. Connect to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A33VDD                                                                                                | 13, 14, 93, 94                                          |             | Analog power. Connect to 3.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A33GND                                                                                                | 12, 15, 92, 95                                          | 1           | Analog 3.3 V return. Connect to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A18GND                                                                                                | 3, 5, 8, 20                                             | 1           | Analog 1.8V return. Connect to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A18VDD                                                                                                | 4, 6, 7, 19                                             | 1           | Analog power. Connect to 1.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PLL_A18VDD<br>PLL_F                                                                                   | 84, 85<br>89                                            | 1           | PLL analog power. Connect to 1.8 V.<br>PLL filter internal supply connection                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PLL_A18GND                                                                                            | 83, 86, 90                                              | 1           | PLL analog power return. Connect to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND                                                                                                   | 40, 68                                                  | 1           | Digital return. Connect to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DVDD                                                                                                  | 39, 69                                                  |             | Digital power. Connect to 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IOGND                                                                                                 | 27, 42, 54, 60,<br>67                                   |             | Digital power return. Connect to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IOVDD                                                                                                 | 26, 41, 53, 66                                          | I           | Digital power. Connect to 3.3 V or less for reduced noise.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SYNC SIGNALS                                                                                          |                                                         | I           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLAMP                                                                                                 | 76                                                      | Ι           | External Clamp input. Unused inputs can be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| COAST                                                                                                 | 77                                                      | Ι           | External PLL COAST signal input. Unused inputs can be connected to ground                                                                                                                                                                                                                                                                                                                                                                                                                         |

## **TERMINAL FUNCTIONS (continued)**

| TERM                       | TERMINAL      |       | DESCRIPTION                                                                                                                                   |

|----------------------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                       | NO.           | - I/O | DESCRIPTION                                                                                                                                   |

| VSYNC_A<br>VSYNC_B         | 78<br>79      | I     | Vertical sync input A<br>Vertical sync input B. Unused inputs can be connected to ground.                                                     |

| HSYNC_A<br>HSYNC_B         | 81<br>82      | l     | Horizontal Sync input A<br>Horizontal Sync input B. Unused inputs can be connected to ground.                                                 |

| SOGIN1<br>SOGIN2<br>SOGIN3 | 1<br>99<br>97 |       | Sync-on-green input 1<br>Sync-on-green input 2<br>Sync-on-green input 3. Unused inputs should be connected to ground using a 10 nF capacitor. |

| VSOUT                      | 23            | 0     | Vertical sync output                                                                                                                          |

| HSOUT                      | 24            | 0     | Horizontal sync output                                                                                                                        |

| SOGOUT                     | 25            | 0     | Sync-on-green slicer output                                                                                                                   |

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|      |                                |                                               | UNIT             |  |  |

|------|--------------------------------|-----------------------------------------------|------------------|--|--|

|      |                                | IOVDD to IOGND                                | –0.5 V to 4.5 V  |  |  |

|      |                                | DVDD to GND                                   | –0.5 V to 2.3 V  |  |  |

|      | Supply voltage range           | PLL_A18VDD to PLL_A18GND and A18VDD to A18GND | –0.5 V to 2.3 V  |  |  |

|      |                                | A33VDD to A33GND                              | – 0.5 V to 4.5 V |  |  |

|      | Digital input voltage range    | VI to GND                                     | –0.5 V to 4.5 V  |  |  |

|      | Analog input voltage range     | AI to A33GND                                  | –0.2 V to 2.3 V  |  |  |

|      | Digital output voltage range   | VO to GND                                     | –0.5 V to 4.5 V  |  |  |

| ТА   | Operating free-air temperature | Operating free-air temperature                |                  |  |  |

| Tstg | Storage temperature            |                                               | –65°C to 150°C   |  |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$  (unless otherwise noted)

|                         |                                              | MIN       | NOM | МАХ       | UNIT |

|-------------------------|----------------------------------------------|-----------|-----|-----------|------|

| IOVDD                   | Digital I/O supply voltage                   | 3.0       | 3.3 | 3.6       | V    |

| DVDD                    | Digital supply voltage                       | 1.70      | 1.8 | 2.0       | V    |

| PLL_A18VDD              | Analog PLL supply voltage                    | 1.8       | 1.9 | 2.0       | V    |

| A18VDD                  | Analog supply voltage                        | 1.8       | 1.9 | 2.0       | V    |

| A33VDD                  | Analog supply voltage                        | 3.0       | 3.3 | 3.6       | V    |

| V <sub>I(P-P)</sub>     | Analog input voltage (ac-coupling necessary) | 0.5       |     | 2.0       | V    |

| VIH                     | Digital input voltage high                   | 0.7 IOVDD |     |           | V    |

| V <sub>IL</sub>         | Digital input voltage low                    |           |     | 0.3 IOVDD | V    |

| I <sub>OH</sub>         | High-level output current                    |           |     | 2         | mA   |

| I <sub>OL</sub>         | Low-level output current                     |           |     | -2        | mA   |

| I <sub>OH_DATACLK</sub> | DATACLK high-level output current            |           |     | 4         | mA   |

| I <sub>OL_DATACLK</sub> | DATACLK low-level output current             |           |     | -4        | mA   |

| T <sub>A</sub>          | Operating free-air temperature               | 0         |     | 70        | °C   |

## **ELECTRICAL CHARACTERISTICS**

$\mathsf{IOVDD} = 3.3 \; \mathsf{V}, \; \mathsf{DVDD} = 1.8 \; \mathsf{V}, \; \mathsf{PLL}\_\mathsf{A18VDD} = 1.9 \; \mathsf{V}, \; \mathsf{A18VDD} = 1.9 \; \mathsf{V}, \; \mathsf{A33VDD} = 3.3 \; \mathsf{V}, \; \mathsf{T}_\mathsf{A} = 25^\circ \mathsf{C}$

|                        | PARAMETER                                | TEST CONDITIONS | MIN TYP <sup>(1)</sup> | MAX <sup>(2)</sup> | UNIT |

|------------------------|------------------------------------------|-----------------|------------------------|--------------------|------|

| POWER SU               | JPPLY                                    |                 |                        |                    |      |

| I <sub>A33VDD</sub>    | 3.3-V supply current                     | 78.75 MHz       | 60                     | 60                 | mA   |

| IIOVDD                 | 3.3-V supply current                     | 78.75 MHz       | 32                     | 78                 | mA   |

| I <sub>A18VDD</sub>    | 1.8-V supply current                     | 78.75 MHz       | 225                    | 225                | mA   |

| I <sub>PLL_18VDD</sub> | 1.8-V supply current                     | 78.75 MHz       | 14                     | 14                 | mA   |

| I <sub>DVDD</sub>      | 1.8-V supply current                     | 78.75 MHz       | 7                      | 9                  | mA   |

| P <sub>TOT</sub>       | Total power dissipation, normal mode     | 78.75 MHz       | 746                    | 901                | mW   |

| I <sub>A33VDD</sub>    | 3.3-V supply current                     | 162 MHz         | 95                     | 95                 | mA   |

| IIOVDD                 | 3.3-V supply current                     | 162 MHz         | 44                     | 125                | mA   |

| I <sub>A18VDD</sub>    | 1.8-V supply current                     | 162 MHz         | 230                    | 230                | mA   |

| I <sub>PLL_18VDD</sub> | 1.8-V supply current                     | 162 MHz         | 20                     | 20                 | mA   |

| I <sub>DVDD</sub>      | 1.8-V supply current                     | 162 MHz         | 17                     | 20                 | mA   |

| P <sub>TOT</sub>       | Total power dissipation, normal mode     | 162 MHz         | 936                    | 1200               | mW   |

| P <sub>DOWN</sub>      | Total power dissipation, power-down mode |                 | 1                      |                    | mW   |

(1) (2)

SMPTE color bar RGB input pattern used. Worst case vertical line RGB input pattern used.

## ELECTRICAL CHARACTERISTICS

IOVDD = 3.3 V, DVDD = 1.8 V $\pm$ 0.1, PLL\_A18VDD = 1.9 V $\pm$ 0.1, A18VDD = 1.9 V $\pm$ 0.1, A33VDD = 3.3 V, T<sub>A</sub> = 0°C to 70°C (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                            | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NTERFACE                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input voltage range                  | By design                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Vpp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Input impedance, analog video inputs | By design                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OGIC INTERFACE                       |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input capacitance                    | By design                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Input impedance                      | By design                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Output voltage high                  | I <sub>OH</sub> = 2 mA                                                                                                                                                                                                                                                                                                                                                                                                     | 0.8 IOVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Output voltage low                   | $I_{OL} = -2 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.2 IOVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DATACLK output voltage high          | I <sub>OH</sub> = 4 mA                                                                                                                                                                                                                                                                                                                                                                                                     | 0.8 IOVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

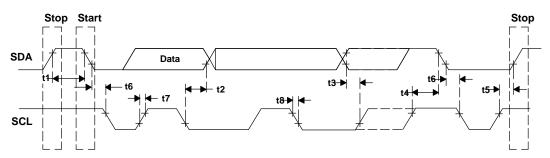

| DATACLK output voltage low           | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.2 IOVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |