# ADVANCED CURRENT-MODE **ACTIVE CLAMP PWM CONTROLLER**

#### **FEATURES**

- Ideal for Active Clamp/Reset Forward, Flyback and Synchronous Rectifier Apps

- **Provides Complementary Auxiliary Driver** with Programmable Deadtime (Turn-On Delay) between AUX and MAIN Switches

- Peak Current-Mode Control with 0.5-V Cycle-by-Cycle Current Limiting

- **Hiccup Mode 0.75-V Current Limit**

- TrueDrive™ 2-A Sink, 2-A Source Outputs

- 110-V Input Startup Device

- **Trimmed Internal Bandgap Reference for** Accurate Line UV and Line OV Threshold

- **Programmable Slope Compensation**

- **High-Performance 1.0-MHz Synchronizable** Oscillator with Internal Timing Capacitor

- **Precise Programmable Maximum Duty Cycle**

- **PB-Free Lead Finish Package**

#### APPLICATIONS

- **High-Efficiency DC/DC Power Supplies**

- Server Power, 48-V Telecom, Datacom, and 42-V Automotive Applications

#### DESCRIPTION

The UCC2897 PWM controller simplifies implementation of the various active clamp/reset and synchronous rectifier switching power topologies.

Based on the UCC2891 active-clamp controller the UCC2897 is a peak current-mode, fixedfrequency, high-performance pulse width modulator. It includes the logic and the drive capability for the P-channel auxiliary switch along with a simple method of programming the critical delays for proper active clamp operation.

Features include an internal programmable slope compensation circuit, precise D<sub>MAX</sub> limit, and a synchronizable oscillator with an internal timing capacitor. An accurate line monitoring function also programs the converter's ON and OFF transitions with regard to the bulk input voltage.

The UCC2897 adds a second level hiccup mode current sense threshold. bi-directional synchronization and the input overvoltage protection functionalities that are not available on the 16-pin UCC2891. The UCC2897 is offered in 20-pin TSSOP (PW) and 20-pin QFN (RTJ) package.

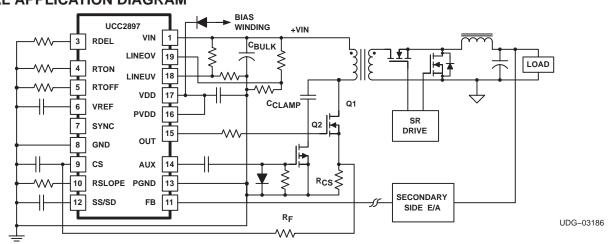

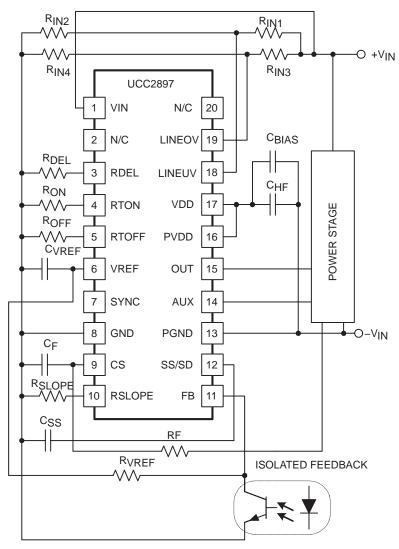

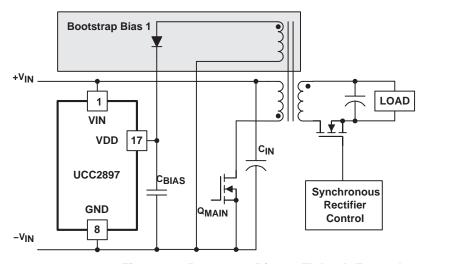

# TYPICAL APPLICATION DIAGRAM

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                                              |                           |                                  | UNIT |

|--------------------------------------------------------------|---------------------------|----------------------------------|------|

| Line input voltage, V <sub>IN</sub>                          |                           | 120                              |      |

| Supply voltage range, V <sub>DD</sub>                        | (I <sub>DD</sub> < 10 mA) | 15                               | V    |

| Analog inputs                                                | FB, CS, SYNC              | -0.3 to (V <sub>REF</sub> + 0.3) |      |

| Output source current (peak), IO_SOURCE                      | OUT ALIV                  | 2.5                              |      |

| Output sink current (peak), IO_SINK                          | OUT, AUX                  | -2.5                             | А    |

| Operating junction temperature range, TJ                     |                           | -55 to 150                       |      |

| Storage temperature, T <sub>Stg</sub>                        | -65 to 150                | °C                               |      |

| Lead temperature, T <sub>SOI</sub> , 1,6 mm (1/16 inch) from | case for 10 seconds       | 300                              |      |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into and negative out of, the specified terminal.

#### RECOMMENDED OPERATING CONDITIONS

|                                                                               | MIN | NOM  | MAX  | UNIT |

|-------------------------------------------------------------------------------|-----|------|------|------|

| Supply voltage, V <sub>DD</sub>                                               | 8.5 | 12.0 | 14.5 | V    |

| Supply bypass capacitance                                                     | 1   |      |      | μF   |

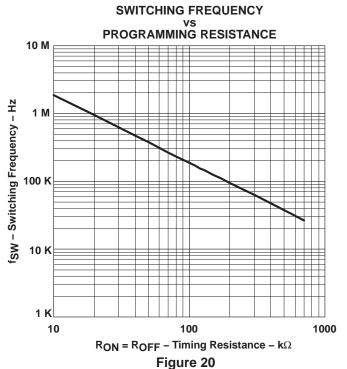

| Timing resistance, R <sub>ON</sub> , R <sub>OFF</sub> (for 250-kHz operation) |     | 75   |      | kΩ   |

| Operating junction temperature, T <sub>J</sub>                                | -40 |      | 125  | °C   |

| Reference bybass capacitance, CREF                                            | 0.1 |      |      | μF   |

#### ORDERING INFORMATION

| TA             | APPLICATION | AUX<br>OUTPUT<br>POLARITY | CYCLE-BY-<br>CYCLE CS<br>THRESHOLD | HICCUP<br>MODE CS<br>THRESHOLD | 110-V HV JFET<br>START-UP<br>CIRCUIT | TSSOP-20<br>(PW)‡ | QFN-20<br>(RTJ)‡ |  |  |  |

|----------------|-------------|---------------------------|------------------------------------|--------------------------------|--------------------------------------|-------------------|------------------|--|--|--|

| 4000 to 40500  | D0/D0       | D. Ohamad                 | 0.5.1/                             | 0.75.1/                        | Voc                                  | UCC2897PW         |                  |  |  |  |

| -40°C to 125°C | DC/DC       | P-Channel                 | 0.5 V                              | 0.75 V                         | Yes                                  |                   | UCC2897RTJ       |  |  |  |

<sup>&</sup>lt;sup>†</sup>The PW package is available taped and reeled. Add R suffix to device type (e.g. UCC2897PWR) to order quantities of 2,000 devices per reel. Bulk quantities are 70 units per tube. The RTJ package is available in two options of tape and reel. The RTJT is orderable in small reels of 250 (e.g. UCC2897RTJT); the RTJR contains 3000 pieces per reel (e.g. UCC2897RTJR).

<sup>&</sup>lt;sup>‡</sup> The TSSOP-20 (PW) and QFN-20 (RTJ) package uses Pb-free lead finish of Pd-Ni-Au which is compatible with MSL level 1 at 255°C to 260°C peak reflow temperature and compatible with either lead free or Sn/Pb soldering operations.

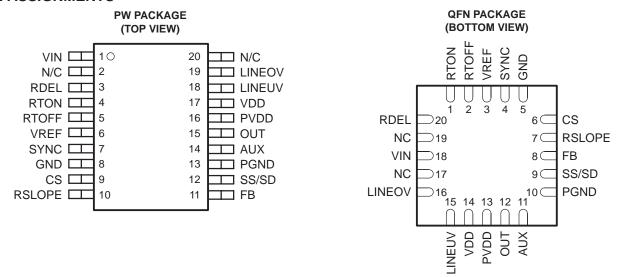

#### **PIN ASSIGNMENTS**

#### **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12 \ V^{(1)}, \ 1-\mu F \ capacitor \ from \ VDD \ to \ GND, \ 0.01-\mu F \ capacitor \ from \ VREF \ to \ GND, \ R_{T(on)} = R_{T(off)} = 75 \ k\Omega, \ R_{DEL} = 10 \ k\Omega, \ R_{SLOPE} = 50 \ k\Omega, \ -40 \ ^{\circ}C \le T_{A} = T_{J} \le 125 \ ^{\circ}C \ (unless \ otherwise \ noted)$

|                 | PARAMETER                             | TEST CONDITIONS                                                            | MIN           | TYP   | MAX                       | UNIT |

|-----------------|---------------------------------------|----------------------------------------------------------------------------|---------------|-------|---------------------------|------|

| OVERALL         |                                       | •                                                                          |               |       |                           |      |

| $V_{DD}$        | Supply voltage range                  |                                                                            |               |       | 14.5                      | V    |

| I <sub>DD</sub> | Operating supply current(1)(2)        | $V_{FB} = 0 \text{ V}, \qquad V_{CS} = 0 \text{ V},$ Outputs not switching |               | 2     | 3                         | mA   |

| HIGH-VOLT/      | AGE BIAS SECTION                      | •                                                                          |               |       |                           |      |

|                 | VDD startup current                   | Current available from VDD during start-<br>up                             | 4             | 10    |                           | mA   |

| UNDERVOL        | TAGE LOCKOUT                          |                                                                            |               |       |                           |      |

|                 | Start threshold voltage(1)            |                                                                            | 12.2          | 12.7  | 13.2                      |      |

|                 | Minimum operating voltage after start |                                                                            | 7.6           | 8.0   | 8.4                       | V    |

|                 | Hysteresis                            |                                                                            | 4.4           | 4.7   | 5.0                       |      |

| LINE MONIT      | OR                                    | •                                                                          | -             |       |                           |      |

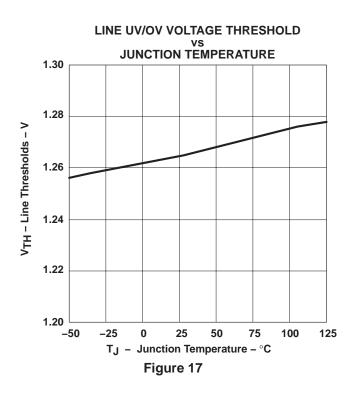

| VLINEU\QV       | Line-on, Line-off voltage thresholds  |                                                                            | 1.243         | 1.268 | 1.294                     | V    |

| LINEHYS         | Line hysteresis                       |                                                                            | 11.8          | 12.5  | 13.2                      | μΑ   |

| SOFT-STAR       | Т                                     | •                                                                          | -             |       |                           |      |

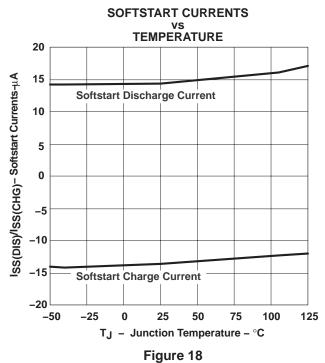

| ISS_CH          | Charge current                        | $I_{RT(on)} = 2.5 \text{ V / R}_{T(on)}$                                   | IRTON<br>-30% | IRTON | I <sub>RTON</sub><br>+30% |      |

| ISS_DSH         | Discharge current                     | $I_{RT(on)} = 2.5 \text{ V / R}_{T(on)}$                                   | IRTON<br>-30% | IRTON | I <sub>RTON</sub><br>+30% | μΑ   |

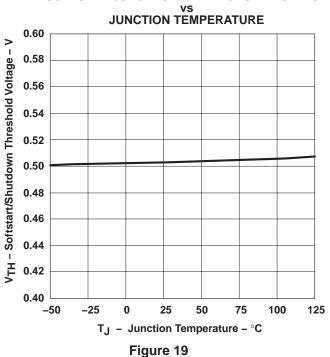

| VSS/SD          | Discharge/shutdown threshold voltage  |                                                                            | 0.4           | 0.5   | 0.6                       | V    |

<sup>(1)</sup> Set VDD above the start threshold before setting at 12 V.

<sup>(2)</sup> Does not include current of the external oscillator network.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12 \ V^{(1)}, \ 1-\mu F \ capacitor \ from \ VDD \ to \ GND, \ 0.01-\mu F \ capacitor \ from \ VREF \ to \ GND, \ R_{T(on)} = R_{T(off)} = 75 \ k\Omega, \ R_{DEL} = 10 \ k\Omega, \ R_{SLOPE} = 50 \ k\Omega, \ -40 \ ^{\circ}C \le T_{A} = T_{J} \le 125 ^{\circ}C \ (unless \ otherwise \ noted)$

|                        | PARAMETER                             | TEST CONDITIONS                                                | MIN  | TYP                        | MAX  | UNIT |

|------------------------|---------------------------------------|----------------------------------------------------------------|------|----------------------------|------|------|

| VOLTAGE                | REFERENCE                             |                                                                |      |                            |      |      |

|                        |                                       | T <sub>J</sub> = 25°C                                          | 4.85 | 5.00                       | 5.15 | .,   |

| V <sub>REF</sub>       | Reference voltage                     | 0 A < IREF < 5 mA, over temperature                            | 4.75 | 5.00                       | 5.25 | V    |

| ISC                    | Short circuit current                 | REF = 0 V, T <sub>J</sub> = 25°C                               | -20  | -11                        |      | mA   |

| INTERNAL               | SLOPE COMPENSATION                    |                                                                |      |                            |      |      |

| m                      | Slope                                 | FB = High                                                      | -10% | $\frac{R_{CS}}{R_{SLOPE}}$ | +10% |      |

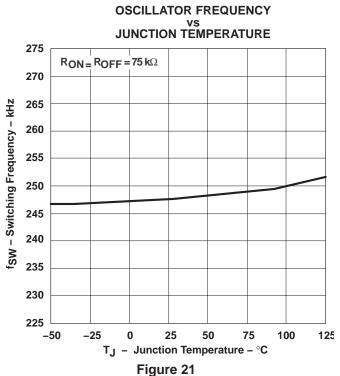

| OSCILLAT               | OR                                    |                                                                |      |                            |      |      |

| fosc                   | Oscillator frequency                  | T <sub>J</sub> = 25°C                                          | 237  | 250                        | 263  |      |

|                        | Total variation                       | Line, Temperature                                              | 225  |                            | 270  | kHz  |

| V <sub>P_P</sub>       | Oscillator amplitude (peak-to-peak)   |                                                                |      | 2                          |      | V    |

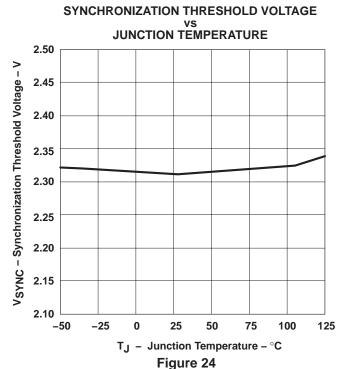

| SYNCHRO                | NIZATION                              |                                                                |      |                            |      |      |

|                        | SYNC input high voltage               |                                                                | 3.0  |                            |      | V    |

|                        | SYNC input low voltage                |                                                                |      |                            | 1.6  | V    |

|                        | SYNC input pulse width <sup>(4)</sup> |                                                                | 50   |                            |      | ns   |

|                        | SYNC pull down output current (3)     |                                                                |      | 600                        |      | μА   |

|                        | SYNC pull up output current(3)        |                                                                |      | -600                       |      | μΑ   |

|                        | SYNC output pulse width(3)            |                                                                |      | 150                        |      | ns   |

| <sup>t</sup> DEL       | SYNC-to-output delay                  |                                                                |      | 50                         |      | ns   |

| PWM                    |                                       |                                                                |      |                            |      |      |

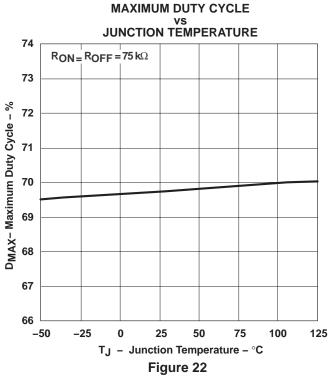

|                        | Maximum duty cycle                    |                                                                | 66%  | 70%                        | 74%  |      |

|                        | Minimum duty cycle                    |                                                                |      |                            | 0%   |      |

|                        | PWM offset                            | CS = 0 V                                                       | 0.43 | 0.52                       | 0.61 | V    |

| OUTPUT (               | OUT AND AUX)                          |                                                                |      |                            |      |      |

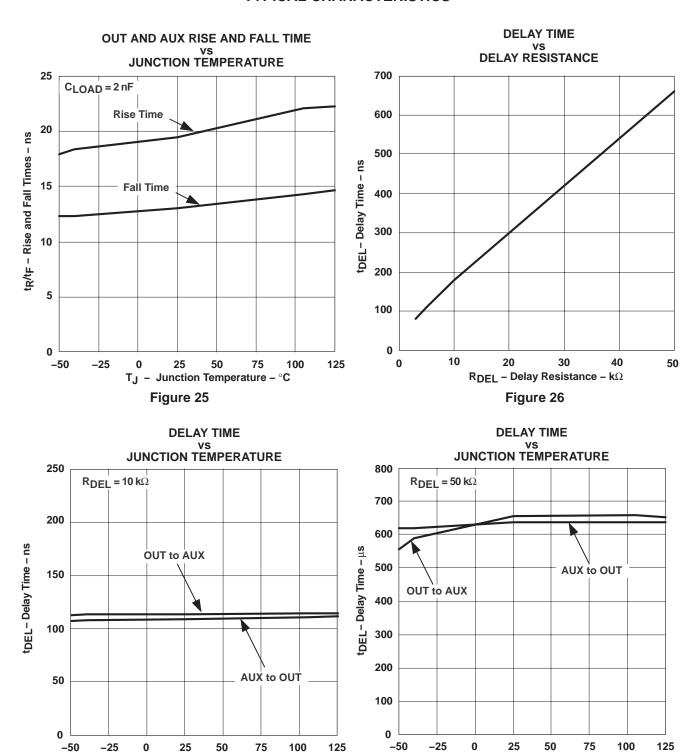

| t <sub>R</sub>         | Rise time                             | $C_{LOAD} = 2 nF$                                              | 10   | 19                         | 28   |      |

| tF                     | Fall time                             | $C_{LOAD} = 2 nF$                                              | 5    | 14                         | 23   |      |

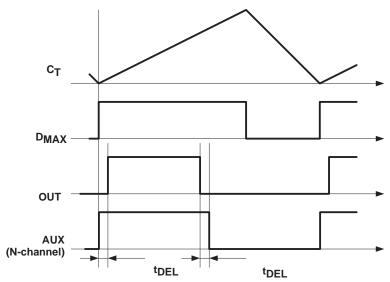

| <sup>t</sup> DEL       | Delay time (AUX to OUT)               | $C_{LOAD} = 2 \text{ nF}, \qquad R_{DEL} = 10 \text{ k}\Omega$ | 90   | 110                        | 130  | ns   |

| <sup>t</sup> DEL       | Delay time (OUT to AUX)               | $C_{LOAD} = 2 \text{ nF},  R_{DEL} = 10 \text{ k}\Omega$       |      | 115                        |      |      |

| I <sub>OUT(src)</sub>  | Output source current                 |                                                                |      | -2                         |      | ^    |

| I <sub>OUT(sink)</sub> | Output sink current                   |                                                                |      | 2                          |      | Α    |

| V <sub>OUT(low)</sub>  | Low-level output voltage              | I <sub>OUT</sub> = 150 mA                                      |      | 0.4                        |      |      |

| VOUT(high)             | High-level output voltage             | I <sub>OUT</sub> = -150 mA                                     |      | 0.9                        |      | V    |

<sup>(1)</sup> Set VDD above the start threshold before setting at 12 V.

<sup>(2)</sup> Does not include current of the external oscillator network.

<sup>(3)</sup> This pulse is typically 150 ns.

<sup>(4)</sup> Maximum pulse width needs to be less than D<sub>MAX</sub>, which is a function of R<sub>T(on)</sub> and R<sub>T(off)</sub>.

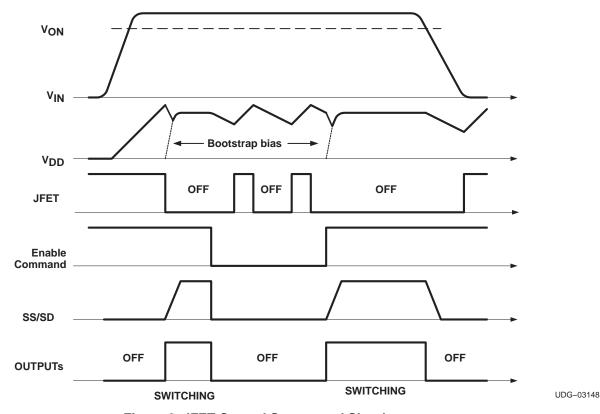

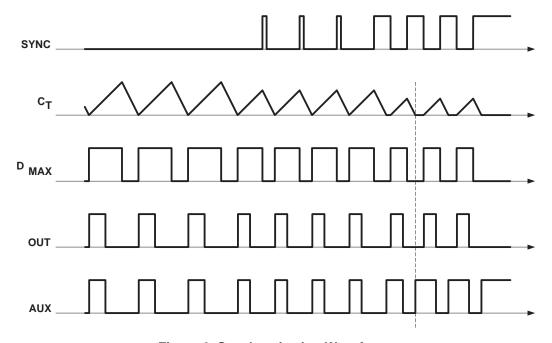

UDG-03147

Figure 1. Output Timing Diagram

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12 \ V^{\left(1\right)}, \ 1-\mu F \ capacitor \ from \ VDD \ to \ GND, \ 0.01-\mu F \ capacitor \ from \ VREF \ to \ GND, \ R_{T\left(on\right)} = R_{T\left(off\right)} = 75 \ k\Omega, \ R_{DEL} = 10 \ k\Omega, \ R_{SLOPE} = 50 \ k\Omega, \ -40 \ ^{\circ}C \le T_{A} = \ T_{J} \le 125 ^{\circ}C \ (unless \ otherwise \ noted)$

|                             | PARAMETER                     |             | TEST CONDITIONS       | MIN  | TYP  | MAX  | UNIT |  |  |  |

|-----------------------------|-------------------------------|-------------|-----------------------|------|------|------|------|--|--|--|

| CURRENT                     | CURRENT SENSE                 |             |                       |      |      |      |      |  |  |  |

| $V_{LVL}$                   | Current sense level shift vol | tage        |                       | 0.45 | 0.50 | 0.55 |      |  |  |  |

| VERR(max)                   | Maximum voltage error (clar   | nped)       |                       | 4.8  | 5.0  | 5.2  | .,   |  |  |  |

| .,                          |                               |             | V <sub>FB</sub> = 5 V | 0.43 | 0.48 | 0.53 | V    |  |  |  |

| VCS Current sense threshold |                               | Hiccup mode |                       | 0.71 | 0.76 | 0.81 |      |  |  |  |

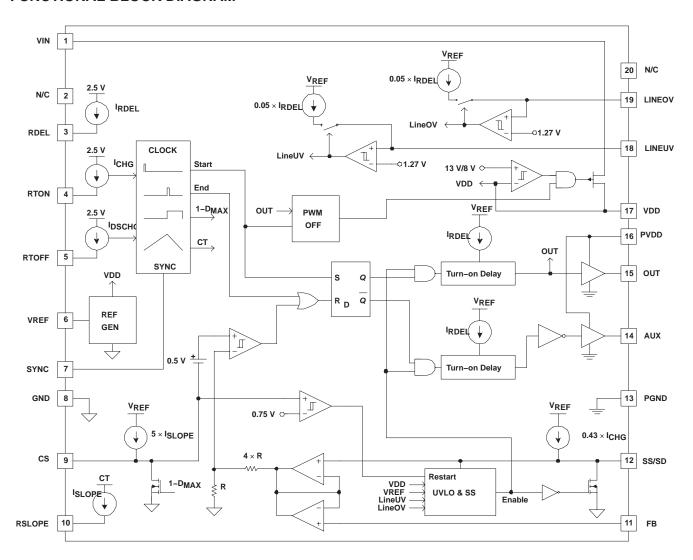

# **FUNCTIONAL BLOCK DIAGRAM**

# **TERMINAL FUNCTIONS**

| TER    | MINAL   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | UCC2897 | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AUX    | 14      | 0   | This output drives the auxiliary clamp P-channel MOSFET which is turned on when the main PWM switching device is turned off. The AUX pin can directly drive the auxiliary switch with 2-A source turnon current and 2-A sink turn-off current.                                                                                                                                                                                                                                                                         |

| CS     | 9       | I   | This pin is used to sense the peak current utilized for current mode control and for current limiting functions. The peak signal which can be applied to this pin before pulse-by-pulse current limiting activates is approximately 0.50 V for the UCC2897.                                                                                                                                                                                                                                                            |

| FB     | 11      | ı   | This pin is used to bring the error signal from an external optocoupler or error amplifier into the PWM control circuitry. Often, there is a resistor tied from FB to VREF, and an optocoupler is used to pull the control pin closer to GND to reduce the pulse width of the OUT output driving the main power switch of the converter.                                                                                                                                                                               |

| GND    | 8       | -   | This pin serves as the fundamental analog ground for the PWM control circuitry. This pin should be connected to PGND directly at the device.                                                                                                                                                                                                                                                                                                                                                                           |

| LINEOV | 19      | I   | Provides the LINE overvoltage function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LINEUV | 18      | ı   | This pin provides a means to accurately enable/disable the power converter stage by monitoring the bulk input voltage or another parameter. When the circuit initially starts (or restarts from a disabled condition), a rising input on LINEUV enables the outputs when the threshold of 1.27 V is crossed. After the circuit is enabled, then a falling LINEUV signal disables the outputs when the same threshold is reached. The hysteresis between the two levels is programmed using an internal current source. |

| OUT    | 15      | 0   | This output pin drives the main PWM switching element MOSFET in an active clamp controller. It can directly drive an N-channel device with 2-A source turn-on current and 2-A sink turn-off current.                                                                                                                                                                                                                                                                                                                   |

| PGND   | 13      | -   | The PGND should serve as the current return for the high-current output drivers OUT and AUX. Ideally, the current path from the outputs to the switching devices, and back would be as short as possible, and enclose a minimal loop area.                                                                                                                                                                                                                                                                             |

| PVDD   | 16      | I   | This is the supply pin for the power devices in the IC. It is separated internally from the VDD pin.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RSLOPE | 10      | ı   | A resistor connected from this pin to GND programs an internal current source that sets the slope compensation ramp for the current mode control circuitry.                                                                                                                                                                                                                                                                                                                                                            |

| RTDEL  | 3       | ı   | A resistor from this pin to GND programs the turn-on delay of the two gate drive outputs to accommodate the resonant transitions of the active clamp power converter.                                                                                                                                                                                                                                                                                                                                                  |

| RTOFF  | 5       | I   | A resistor connected from this pin to GND programs an internal current source that discharges the internal timing capacitor.                                                                                                                                                                                                                                                                                                                                                                                           |

| RTON   | 4       | ı   | A resistor connected from this pin to GND programs an internal current source that charges the internal timing capacitor.                                                                                                                                                                                                                                                                                                                                                                                              |

| SS/SD  | 12      | ı   | A capacitor from SS/SD to ground is charged by an internal current source of IRTON to program the soft-start interval for the controller. During a fault condition this capacitor is discharged by a current source equal to IRTON.                                                                                                                                                                                                                                                                                    |

| SYNC   | 7       | ı   | The SYNC pin serves as a bidirectional synchronization input/output for the internal oscillator. The synchronization function is implemented such that the user programmable maximum duty cycle (set by RTON and RTOFF) remains accurate during synchronized operation.                                                                                                                                                                                                                                                |

| VDD    | 17      | I   | This is the power supply for the device. There should be a minimum $0.1$ - $\mu F$ capacitor directly from VDD to PGND.                                                                                                                                                                                                                                                                                                                                                                                                |

| VIN    | 1       | I   | This pin is connected to the input power rail directly. Inside the device, a high-voltage start-up device is utilized to provide the start-up current for the controller until a bootstrap type bias rail becomes available.                                                                                                                                                                                                                                                                                           |

| VREF   | 6       | 0   | This is the 5-V reference voltage that can be utilized for an external load of up to 5 mA. Since this reference provides the supply rail for internal logic, it should be bypassed to AGND as close as possible to the device.                                                                                                                                                                                                                                                                                         |

#### **DETAILED PIN DESCRIPTIONS**

# VIN (pin 1)

The UCC2897 controller are equipped with a high voltage, P-channel JFET start up device to initiate operation from the input power source of the converter in applications where the input voltage does not exceed the 110-V maximum rating of the start up transistor. In these applications, the VIN pin can be connected directly to the positive terminal of the input power source. The internal JFET start up transistor provides approximately 15-mA charge current for the energy storage capacitor (C<sub>BIAS</sub>) connected across the VDD (pin 14) and PGND (pin 11) terminals. Note that the start up device is turned off immediately when the voltage on the VDD pin exceeds approximately 13.5 V, the controller's undervoltage lockout threshold for turn-on. The JFET is also disabled at all times when the high-current gate drivers are switching to protect against excessive power dissipation and current through the device.

For more information on biasing the UCC2897, refer to the Setup Guide and Additional Application Sections of this datasheet.

# RDEL (pin 3)

This pin is internally connected to an approximately 2.5-V DC source. A resistor (R<sub>DEL</sub>) to GND (pin 6) sets the turn-on delay for both gate drive signals of the UCC2987 controller. The delay time is identical for both switching transitions, between OUT (pin 13) is turning off and AUX (pin 14) is turning on as well as when AUX (pin 14) is turning off and OUT (pin 13) is turning on. The delay time is defined as:

$$t_{DEL} = R_{DEL} \times 1.1 \times 10^{-11}$$

(1)

For proper selection of the delay time refer to the various references describing the design of active clamp power converters.

# RTON (pin 4)

This pin is internally connected to an approximately 2.5-V DC source. A resistor (R<sub>ON</sub>) to GND (pin 6) sets the charge current of the internal timing capacitor. The RTON pin, in conjunction with the RTOFF pin (pin 3) are used to set the operating frequency and maximum operating duty cycle of the UCC2897.

#### RTOFF (pin 5)

This pin is internally connected to an approximately 2.5-V DC source. A resistor ( $R_{OFF}$ ) to GND (pin 6) sets the discharge current of the internal timing capacitor. The RTON and RTOFF pins are used to set the switching period ( $T_{SW}$ ) and maximum operating duty cycle ( $D_{MAX}$ ) according to the following equations:

$$t_{ON} = 37.33 \times 10^{-12} \times R_{ON}$$

(2)

$$t_{OFF} = 16 \times 10^{-12} \times R_{OFF} \tag{3}$$

$$T_{SW} = t_{ON} + t_{OFF}$$

(4)

$$D_{MAX} = \frac{t_{ON}}{T_{SW}} \tag{5}$$

# VREF (pin 6)

The controller's internal, 5-V bias rail is connected to this pin. The internal bias regulator requires a good quality ceramic bypass capacitor ( $C_{VREF}$ ) to GND (pin 6) for noise filtering and to provide compensation to the regulator circuitry. The recommended  $C_{VREF}$  value is 0.22- $\mu$ F. The minimum bypass capacitor value is 0.022- $\mu$ F limited by stability considerations of the bias regulator, while the maximum is approximately 22- $\mu$ F.

The VREF pin is internally current limited and can supply approximately 5-mA to external circuits. The 5-V bias is only available when the undervoltage lock out (UVLO) circuit enables the operation of UCC2897 controller.

For the detailed functional description of the undervoltage lock out (UVLO) circuit refer to the *Functional Description* section of this datasheet.

## SYNC (pin 7)

This pin is a bi-directioanl synchonization terminal.

This pin provides an input for an external clock signal which can be used to synchronize the internal oscillator of the UCC2897 controller. The synchronizing frequency must be higher than the free running frequency of the onboard oscillator ( $T_{SYNC} < T_{SW}$ ). The acceptable minimum pulse width of the synchronization signal is approximately 50 ns (positive logic), and it should remain shorter than  $(1 - D_{MAX}) \times T_{SYNC}$  where  $D_{MAX}$  is set by  $R_{ON}$  and  $R_{OFF}$ . If the pulse width of the synchronization signal stays within these limits, the maximum operating duty ratio remains valid as defined by the ratio of  $R_{ON}$  and  $R_{OFF}$ , and  $D_{MAX}$  is the same in free running and in synchronized modes of operation. If the pulse width of the synchronization signal would exceed the  $(1 - D_{MAX}) \times T_{SYNC}$  limit, the maximum operating duty cycle is defined by the synchronization pulse width.

In the stand-alone mode, the SYNC pin is driven by the internal oscillator which provides output pulses of approximately 100-ns wide 5-V amplitude square wave. This signal can be use to synchronize other PWM controllers or circuits needing a constant frequency time base.

For more information on synchronization of the UCC2897 refer to the *Functional Description* section of this datasheet.

# GND (pin 8)

This pin provides a reference potential for all small signal control and programming circuitry inside the UCC2897. Ground layout is critical for correct operation. High current surges from the MOSFET drivers conduct through PVDD, OUT, AUX, and PGND. TO localize these surges, PVDD must be bypassed directly to PGND. PGND current must be electrically, capacitively, and inductively isolated from GND with only one short trace connecting PGND to GND, located to best minimize noise into GND.

# **CS** (pin 9)

This is a direct input to the PWM and current limit comparators of the UCC2897 controller. The CS pin should never be connected directly across the current sense resistor ( $R_{CS}$ ) of the power converter. A small, customary R–C filter between the current sense resistor and the CS pin is necessary to accommodate the proper operation of the onboard slope compensation circuit and in order to protect the internal discharge transistor connected to the CS pin ( $R_{F}$ ,  $C_{F}$ ).

Slope compensation is achieved across  $R_F$  by a linearly increasing current flowing out of the CS pin. The slope compensation current is only present during the on-time of the gate drive signal of the main power switch (OUT) of the converter. The internal pull-down transistor of the CS pin is activated during the discharge time of the timing capacitor. This time interval is  $\left(1-D_{MAX}\right) \times T_{SW}$  long and represents the ensured off time of the main power switch.

The UCC2897 has a two level over-current protection. There are two different thresholds for cycle by cycle and hiccup mode current limit operation. The UCC2897 will operate continuously in cycle-by-cycle current limit mode with a 0.5-V maximum current sense voltage. In case the magnetic components would saturate and the current level increases by an additional 50% (0.75-V threshold), a hiccup cycle is initiated. The hiccup cycle consists of a wait period with no switching action while the soft-start capacitor is slowly discharged to 0.5 V followed by a normal soft start sequence.

# **RSLOPE** (pin 10)

A resistor ( $R_{SLOPE}$ ) connected between this pin and GND (pin 6) sets the amplitude of the slope compensation current. During the on time of the main gate drive output (OUT) the voltage across  $R_{SLOPE}$  is a representation of the internal timing capacitor waveform. As the timing capacitor is being charged, the voltage across  $R_{SLOPE}$  also increases, generating a linearly increasing current waveform. The current provided at the CS pin for slope compensation is proportional to this current flowing through  $R_{SLOPE}$ .

Due to the high speed, AC voltage waveform present at the RSLOPE pin, the parasitic capacitance and inductance of the external circuit components connected to the RSLOPE pin should be carefully minimized.

For more information on how to program the internal slope compensation refer to the *Setup Guide* section of this datasheet.

## FB (pin 11)

This pin is an input for the control voltage of the pulse width modulator of the UCC2897. The control voltage is generated by an external error amplifier by comparing the converters output voltage to a voltage reference and employing the compensation for the voltage regulation loop. Usually, the error amplifier is located on the secondary side of the isolated power converter and its output voltage is sent across the isolation boundary by an opto coupler. Thus, the FB pin is usually driven by the opto coupler. An external pull-up resistor to the VREF pin (pin 4) is also needed for proper operation as part of the feedback circuitry.

The control voltage is internally buffered and connected to the PWM comparator through a voltage divider to make it compatible to the signal level of the current sense circuit. The useful voltage range of the FB pin is between approximately 2.5 V and 4.5 V. Control voltages below the 2.5-V threshold result in zero duty cycle.

# **SS/SD** (pin 12)

A capacitor ( $C_{SS}$ ) connected between this pin and GND (pin 6) programs the soft start time of the power converter. The soft-start capacitor is charged by a precise, internal DC current source which is programmed by the  $R_{ON}$  resistor connected to pin 2. The soft-start current is defined as:

$$I_{SS} = \frac{2.5 \text{ V}}{R_{ON}} \times 0.43 \tag{6}$$

This DC current charges  $C_{SS}$  from 0 V to approximately 5 V. Internal to the UCC2897 controller, the soft start capacitor voltage is buffered and ORed with the control voltage present at the FB pin (pin 9). The lower of the two voltages manipulates the controller's PWM engine through the voltage divider described with regards to the FB pin. Accordingly, the useful control range on the SS pin is similar to the control range of the FB pin and it is between 2.5 V and 4.5 V approximately.

## PGND (pin 13)

This pin serves as a dedicated connection to all high-current circuits inside the UCC2897. The high-current portion of the controller consists of the two high-current gate drivers, and the various bias connections except VREF (pin 4). While the PGND (pin 11) and GND (pin 6) pins are connected internally, a low-impedance, external connection between the two ground pins is also required. It is recommended to form a separate ground plane for the low current setup components (RDEL, RON, ROFF, CVREF, CF, RSLOPE, CSS and the emitter of the opto-coupler in the feedback circuit). This separate ground plane (GND) should have a single connection to the rest of the ground of the power converter (PGND) and this connection should be between pin 6 and pin 11 of the controller.

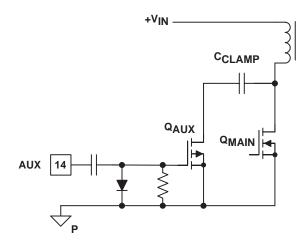

### **AUX (pin 14)**

This is a high-current gate drive output for the auxiliary switch to implement the active clamp operation for the power stage. The auxiliary output (AUX) of the UCC2897 drives a P-channel device as the clamp switch therefore it requires an active low operation (the switch is ON when the output is low).

# **OUT (pin 15)**

This high-current output drives an external N-channel MOSFET. Each controller in the UCC2897 uses active high drive signals for the main switch of the converter.

Due to the high speed and high-drive current capability of these outputs (AUX, OUT) the parasitic inductance of the external circuit components connected to these pins should be carefully minimized. A potential way of avoiding unnecessary parasitic inductances in the gate drive circuit is to place the controller in close proximity to the MOSFETs and by ensuring that the outputs (AUX, OUT) and the gates of the MOSFET devices are connected by wide, overlapping traces.

#### PVDD (pin 16)

The PVDD pin in the supply rail for the output power devices of the IC. It is completely separated internally by the VDD pin.

# **VDD (pin 17)**

The VDD rail is the primary bias for the internal, high-current gate drivers, the internal 5-V bias regulator and for parts of the undervoltage lockout circuit. To reduce switching noise on the bias rail, a good quality ceramic capacitor ( $C_{HF}$ ) must be placed very closely between the VDD pin and PGND (pin 11) to provide adequate filtering. The recommended  $C_{HF}$  value is 1- $\mu$ F for most applications but its value might be affected by the properties of the external MOSFET transistors used in the power stage.

In addition to the low-impedance, high-frequency filtering, the controller's bias rail requires a larger value energy storage capacitor ( $C_{BIAS}$ ) connected parallel to  $C_{HF}$ . The energy storage capacitor must provide the hold up time to operate the UCC2897 (including gate drive power requirements) during start up. In steady state operation the controller must be powered from a bootstrap winding off the power transformer or by an auxiliary bias supply. In case of an independent auxiliary bias supply, the energy storage is provided by the output capacitance of the bias supply.

# LINEUV (pin 18)

This input monitors the incoming power source to provide an accurate undervoltage lockout function with user programmable hysteresis for the power supply controlled by the UCC2897. The unique property of the UCC2897 is to use only one pin to implement these functions without sacrificing on performance. The input voltage of the power supply is scaled to the precise 1.27-V threshold of the undervoltage lockout comparator by an external resistor divider ( $R_{IN1}$ ,  $R_{IN2}$ ). Once the line monitor's input threshold is exceeded, an internal current source gets connected to the LINEUV pin. The current generator is programmed by the  $R_{DEL}$  resistor connected to pin 1 of the controller. The actual current level is given as:

$$I_{HYST} = \frac{2.5 \text{ V}}{R_{DEL}} \times 0.05 \tag{7}$$

As this current flows through  $R_{IN2}$  of the input divider, the undervoltage lockout hysteresis is a function of  $I_{HYST}$  and  $R_{IN2}$  allowing accurate programming of the hysteresis of the line monitoring circuit.

For more information on how to program the line monitoring function refer to the Setup Guide of this datasheet.

#### LINEOV (pin 19)

In the UCC2897 controller the high-voltage start-up device is not utilized thus pin 16 is used for a different function. This input monitors the incoming power source to provide an accurate overvoltage protection with user programmable hysteresis for the power supply controlled by the controller. The circuit implementation of the overvoltage protection function is identical to the technique used for monitoring the input power rail for undervoltage lockout. This allows implementing an accurate threshold and hysteresis using only one pin. The input voltage of the power supply is scaled to the precise 1.27-V threshold of the overvoltage protection comparator by an external resistor divider ( $R_{IN3}$ ,  $R_{IN4}$ ). Once the line monitor's input threshold is exceeded, an internal current source gets connected to the LINEOV pin. The current generator is programmed by the  $R_{DEL}$  resistor connected to pin 1 of the controller. The actual current level is given as:

$$I_{HYST} = \frac{2.5 \text{ V}}{R_{DEL}} \times 0.05 \tag{8}$$

As this current flows through  $R_{IN4}$  of the input divider, the overvoltage protection hysteresis is a function of  $I_{HYST}$  and  $R_{IN4}$  allowing accurate programming of the hysteresis of the line monitoring circuit.

For more information on how to program the overvoltage protection, refer to the Setup Guide of this datasheet.

#### **JFET Control and UVLO**

The UCC2897 controller includes the 110-V high voltage JFET start up transistor. The steady state power consumption of the of the control circuit which also includes the gate drive power loss of the two power switches of an active clamp converter exceeds the current and thermal capabilities of the device. Thus the JFET should only be used for initial start up of the control circuitry and to provide keep-alive power during stand-by mode when the gate drive outputs are not switching. Accordingly, the start-up device is managed by its own control algorithm implemented on board the UCC2897. The following timing diagram illustrates the operation of the JFET start up device.

Figure 2. JFET Control Startup and Shutdown

During initial power up the JFET is on and charges the  $C_{BIAS}$  and  $C_{HF}$  capacitors connected to the VDD pin (pin 14). The VDD pin is monitored by the controller's undervoltage lockout circuit to ensure proper biasing before the operation is enabled. When the VDD voltage reaches approximately 13.5 V (UVLO turn-on threshold) the UVLO circuit enables the rest of the controller. At that time, the JFET is turned off and 5 V appears on the VREF terminal (pin 4). Switching waveforms might not appear at the gate drive outputs unless all other conditions of proper operation are met. These conditions are:

- sufficient voltage on the VREF pin (V<sub>VRFF</sub> > 4.5V)

- the voltage on the CS pin is below the current limit threshold

- the control voltage is above the zero duty cycle boundary (V<sub>FB</sub> > 1.25 V)

- the input voltage is in the valid operating range (V<sub>VON</sub><V<sub>VIN</sub><V<sub>VOFF</sub>) i.e. the line under or overvoltage protections are not activated.

As the controller starts operation it draws its bias power from the  $C_{BIAS}$  capacitor until the bootstrap winding takes over. During this time VDD voltage is falling rapidly as the JFET is already off but the bootstrap voltage is still not sufficient to power the control circuits. It is imperative to store enough energy in  $C_{BIAS}$  to prevent the bias voltage to dip below the turn off threshold of the UVLO circuit during the start up time interval. Otherwise the power supply goes through several cycles of retry attempts before steady state operation might be established.

During normal operation the bias voltage is determined by the bootstrap bias design. The UCC2897 can tolerate a wide range of bias voltages between the minimum operating voltage (UVLO turn-off threshold) and the absolute maximum operating voltage as defined in the datasheet (14 V).

In applications where the power supply must be able to go to stand by in response to an external command, the bias voltage of the controller must be kept alive to be able to react intelligently to the control signal. In stand by mode, switching action is suspended for an undefined period of time and the bootstrap power is unavailable to bias the controller. Without an alternate power source the bias voltage would collapse and the controller would initiate a re-start sequence. To avoid this situation, the on board JFET of the UCC2897 controller can keep the VDD bias alive as long as the gate drive outputs remain inactive. As shown in the timing diagram, the JFET is turned on when VDD = 10 V and charges the  $C_{BIAS}$  capacitor to approximately 13.5 V. At that time the JFET turns off and VDD gradually decreases to 10 V then the procedure is repeated. When the power supply is enabled again, the controller is fully biased and ready to initiate its soft start sequence. As soon as the gate drive pulses appear the JFET are turned off and bias must be provided by the bootstrap bias generator.

During power down the situation is different as switching action might continue until the VDD bias voltage drops below the controller's own UVLO turn-off threshold (approximately 8 V). At that time the UCC2897 shuts down completely turning off its 5 V bias rail and returning to start up state when the JFET device is turned on and the C<sub>BIAS</sub> capacitor starts charging again. In case the converter's input voltage is re-established, the UCC2897 attempts to restart the converter.

# **Line Undervoltage Protection**

When the input power source is removed the power supply is turned off by the line undervoltage protection because the bootstrap winding keeps the VDD bias up as long as switching takes place in the power stage. As the power supply's input voltage gradually decreases towards the line cut off voltage the converter's operating duty cycle must compensate for the lower input voltage. At minimum input voltage the duty cycle nears its maximum value (D<sub>MAX</sub>). Under these conditions the voltage across the clamp capacitor approaches its highest value since the transformer must be reset in a relatively short time. The timing diagram in Figure 2 highlights that in the instance when the converter stops switching the clamp capacitor voltage might be at its maximum level. Since the clamp capacitor's only load is the power transformer, this high voltage could linger across the clamp capacitor for a long time when the converter is off. With this high voltage present across the clamp capacitor a soft start would be very dangerous. Due to the narrow duty cycle of the main switch and the long on-time of the clamp switch, easily cauing the power transformer to saturate during soft-start.

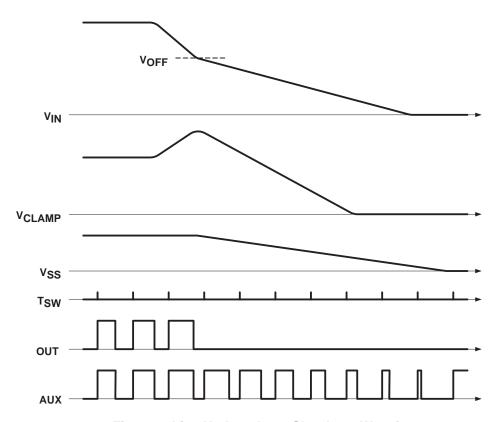

UDG-03149

#### **FUNCTIONAL DESCRIPTION**

Figure 3. Line Undervoltage Shutdown Waveforms

To eliminate this potential hazard the UCC2897 controller safely discharge the clamp capacitor during power down. As shown by the timing diagram in Figure 4, the undervoltage lockout circuits stop the power transfer in the converter by disabling the gate drive signal for the main switch (OUT). The AUX output keeps switching while the soft-start capacitor  $C_{SS}$  is being slowly discharged. Notice that the AUX pulse width gradually increases as the clamp voltage decreases never applying the high voltage across the transformer for extended period of time. During the slow discharge of the timing capacitor the converter can not be restarted even if the input voltage returns to the acceptable range.

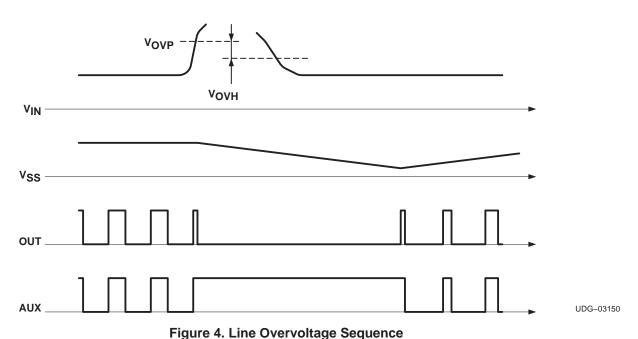

#### **Line Overvoltage Protection**

When the line overvoltage protection is triggered in the UCC2897 controller, the gate drive signals are immediately disabled. At the same time, the slow discharge of  $C_{SS}$  is initiated. While the soft-start capacitor is discharging the gate drive signals remains disabled. Once  $C_{SS} = 0.5 \text{ V}$  and the overvoltage disappears from the input of the power supply, operation resumes through a regular soft-start of the converter as it is demonstrated in Figure 5.

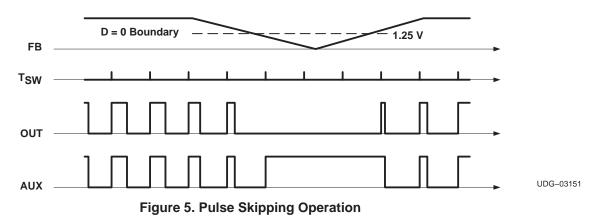

# **Pulse Skipping**

During output load current transients or light load conditions most PWM controller needs to be able to skip some number of PWM pulses. In an active clamp topology where the clamp switch is driven complementarily to the main switch, this would apply the clamp voltage across the transformer continuously. Since operating conditions might require skipping several switching cycles on the main transistor, saturating the transformer is very likely if the AUX output stays on.

To overcome this problem, the UCC2897 incorporates pulse skipping for both outputs in the controller. As can be seen above, when a pulse is skipped at the main output (OUT) because the feedback signal demands zero duty ratio, the corresponding output pulse on the AUX output is omitted as well. This operation allows to prevent reverse saturation of the power transformer and to preserve the clamp capacitor voltage level during pulse skipping operation.

# **Synchronization**

The UCC2897 has a bi-directional synchronization terminal (pin 7). In the stand-alone operation the SYNC pin is driven by the internal oscillator of the UCC2897 which provides an approximately TBD-ns wide TBD-V amplitude square wave output. This signal can be used to synchronize other PWM controllers or circuits needing a constant frequency time base. The synchronization output of the UCC2897 is generated when the internal timing capacitor reaches its peak value. Therefore, the synchronization waveform does not coincide with the turn on of the main gate driver output as it is usually implemented in PWM controllers.

The operation of the oscillator and relevant other waveforms in free running and synchronized mode are shown in Figure 6.

Figure 6. Synchronization Waveforms

The most critical and unique feature of the oscillator is to limit the maximum operating duty cycle of the converter. It is achieved by accurately controlling the charge and discharge intervals of the on board timing capacitor. The maximum on-time of OUT (pin 13), which is also the maximum duty cycle of the active clamp converter is limited by the charging interval of the timing capacitor. While the capacitor is being reset to its initial voltage level OUT is guaranteed to be off.

When synchronization is used, the rising edge of the signal terminates the charging period and initiate the discharge of the timing capacitor. Once the timing capacitor voltage reaches the predefined valley voltage, a new charge period starts automatically. This method of synchronization leaves the charge and discharge slopes of the timing waveform unaffected thus maintains the maximum duty cycle of the converter, independent of the mode of operation.

Although the synchronization circuit is level sensitive, the actual synchronization event occurs at the rising edge of the waveform. This allows the synchronizing pulse width to vary significantly but certain limitations must be observed. The minimum pulse width should be sufficient to guarantee reliable triggering of the internal oscillator circuitry, therefore it should be greater than approximately 50 nanoseconds. The other limiting factor is to keep it shorter than  $\left(1-D_{\text{MAX}}\right) \times T_{\text{SYNC}}$  where  $T_{\text{SYNC}}$  is the period of the synchronization frequency.

When a wider than  $\left(1-D_{MAX}\right) \times T_{SYNC}$  pulse is connected to the SYNC input, the oscillator is not able to maintain the maximum duty cycle, originally set by the timing resistor ratio (R<sub>ON</sub>, R<sub>OFF</sub>). Furthermore, the timing capacitor waveform has a flat portion as highlighted by the vertical marker in the timing diagram. During this flat portion of the waveform both outputs is off which state is not compatible with the operation of active clamp power converters. Therefore, this operating mode is not recommended .

Note that both outputs of the UCC2897 controller are off if the synchronization signal stays continuously high.

When two UCC2897's are synchronized by tying their SYNC pins together, they will operate in–phase. It is possible to set different maximum duty cycle limits for the two UCC2897's and still synchronize them by a simple connection between their respective SYNC terminals.

#### **APPLICATION INFORMATION: SETUP GUIDE**

Figure 7. UCC2897 Typical Setup

The UCC2897 offers a highly integrated feature set and excellent accuracy to control an active clamp forward or active clamp flyback power converter. In order to take advantage of all the benefits integrated in these controller, the following procedure can simplify the setup and avoid unnecessary iterations in the design procedure. Refer to Figure 7 setup diagrams for component names.

Before the controller design begins, the power stage design must be completed. From the power stage design the following operating parameters are needed to complete the setup procedure of the controller:

- Switching frequency (f<sub>SW</sub>)

- Maximum operating duty cycle (D<sub>MAX</sub>)

- Soft start duration (t<sub>SS</sub>)

- Gate drive power requirements of the external power MOSFETs (Q<sub>G(main)</sub>, Q<sub>G(aux)</sub>)

- Bias method and voltage for steady state operation (bootstrap or bias supply)

- Gate drive turn-on delay (t<sub>DFL</sub>)

- Turn-on input voltage threshold (V<sub>ON</sub>)

- Minimum operating input voltage (V<sub>OFF</sub>) where V<sub>IN (off)</sub> < V<sub>IN(on)</sub>

- Maximum operating input voltage (V<sub>OVP</sub>)

- overvoltage protection hysteresis (V<sub>OVH</sub>)

- The down slope of the output inductor current waveform reflected across the primary side current sense resistor (dV<sub>1</sub> /dt)

#### Step 1. Oscillator

The two timing elements of the oscillator can be calculated from f<sub>SW</sub> and D<sub>MAX</sub> by the following two equations:

$$R_{ON} = \frac{t_{ON}}{37.33 \times 10^{-12}} = \frac{D_{MAX}}{f_{SW} \times 37.33 \times 10^{-12}}$$

(9)

$$R_{OFF} = \frac{t_{OFF}}{16 \times 10^{-12}} = \frac{1 - D_{MAX}}{f_{SW} \times 16 \times 10^{-12}}$$

(10)

where D<sub>MAX</sub> is a dimensionless number between 0 and 1.

## Step 2. Soft Start

Once RON is defined, the charge current of the soft-start capacitor can be calculated as:

$$I_{SS} = \frac{2.5 \text{ V}}{R_{ON}} \times 0.43 \tag{11}$$

During soft start,  $C_{SS}$  is being charged from 0 V to 5 V by the calculated  $I_{SS}$  current. The actual control range of the soft-start capacitor voltage is between 1.25 V and 4.5 V. Therefore, the soft-start capacitor value must be based on this narrower control range and the required start up time ( $t_{SS}$ ) according to:

$$C_{SS} = \frac{I_{SS} \times t_{SS}}{4.5 \text{ V} - 1.25 \text{ V}}$$

(12)

Note, that t<sub>SS</sub> defines a time interval to reach the maximum current capability of the converter and not the time required to ramp the output voltage from 0 V to its nominal, regulated level. Using an open-loop start up scheme does not allow accurate control over the ramp up time of the output voltage. In addition to the I<sub>SS</sub> and C<sub>SS</sub> values, the time required to reach the nominal output voltage of the converter is a function of the maximum output current (current limit), the output capacitance of the converter and the actual load conditions. If it is critical to implement a tightly controlled ramp-up time at the output of the converter, the soft-start must be implemented using a closed loop technique. Closed loop soft-start can be implemented with the error amplifier of the voltage regulation loop when its voltage reference is ramped from 0 V to its final steady state value during the required t<sub>SS</sub> start up time interval.

# Step 3. VDD Bypass Requirements

First, the high-frequency filter capacitor is calculated based on the gate charge parameters of the external MOSFETs. Assuming that the basic switching frequency ripple should be kept below 0.1-V across  $C_{HF}$ , its value can be approximated as:

$$C_{HF} = \frac{Q_{G(main)} + Q_{G(aux)}}{0.1 \text{ V}}$$

(13)

The energy storage requirements are defined primarily by the start up time ( $t_{SS}$ ) and turn-on (approximately 13.5 V) and turn-off (approximately 8 V) thresholds of the controller's undervoltage lockout circuit monitoring the VDD voltage at pin 14. In addition, the bias current consumption of the entire primary side control circuit ( $I_{DD}$  +  $I_{EXT}$ ) must be known. This power consumption can be estimated as:

$$P_{BIAS} = \left[I_{DD} + I_{EXT} + \left(Q_{G(main)} + Q_{G(aux)} \times f_{SW}\right)\right] \times V_{DD}$$

(14)

During start up  $(t_{SS})$  this power is provided by  $C_{BIAS}$  while its voltage must remain above the UVLO turn-off threshold. This relationship can be expressed as:

$$P_{BIAS} \times t_{SS} < \frac{1}{2} \times C_{BIAS} \times (13.5^2 - 8^2)$$

(15)

Rearranging the equation yields the minimum value for C<sub>BIAS</sub>:

$$C_{BIAS} > \frac{2 \times P_{BIAS} \times t_{SS}}{\left(13.5^2 - 8^2\right)} \tag{16}$$

#### Step 4. Delay Programming

From the power stage design, the required turn-on delay ( $t_{DEL}$ ) of the gate drive signals is defined. The corresponding  $R_{DEL}$  resistor value to implement this delay is given by:

$$R_{DEL} = (t_{DEL} - 50 \times 10^{-9}) \times 0.87 \times 10^{11}$$

(17)

# **Step 5. Input Voltage Monitoring**

The input voltage monitoring functions is governed by the following two expressions of the voltage at the LINEUV terminal (pin 15):

$$V_{VON} = V_{ON} \times \frac{R_{IN2}}{R_{IN1} + R_{IN2}}$$

at turn on, and (18)

$$V_{VON} = \left(\frac{V_{OFF} - V_{VON}}{R_{IN1}} + I_{HYST}\right) \times R_{IN2} \text{ at turn off.}$$

(19)

Since  $V_{ON}$  and  $V_{OFF}$  are given by the power supply specification,  $V_{VON}$  equals the 1.27-V threshold of the line monitor and  $I_{HYST}$  is already defined as:

$$I_{HYST} = \frac{2.5 \text{ V}}{R_{DEL}} \times 0.05 \tag{20}$$

the two unknown,  $R_{IN1}$  and  $R_{IN2}$  are fully determined. Solving the equations results the following two expressions for the input voltage divider:

$$R_{IN1} = \frac{V_{ON} - V_{OFF}}{I_{HYST}}$$

(21)

$$R_{IN2} = R_{IN1} \times \frac{1.27 \text{ V}}{V_{ON} - 1.27 \text{ V}}$$

(22)

Similar methods can be used to define the divider components of the overvoltage protection input of the UCC2897 controller.

#### Step 6. Current Sense and Slope Compensation

The UCC2897 offers onboard, user programmable slope compensation. The programming of the right amount of slope compensation is accomplished by the appropriate selection of two external resistors, R<sub>F</sub> and R<sub>SI OPF</sub>.

First, the current sense filter resistor value ( $R_F$ ) must be calculated based on the desired filtering of the current sense signal. The filter consists of two components,  $C_F$  and  $R_F$ . The  $C_F$  filter capacitor is connected between the CS pin (pin 7) and the GND terminal (pin 6). While the value of  $C_F$  can be freely selected as the first step of the filter design, it should be minimized to avoid filtering the slope compensation current exiting the CS pin. The recommended range for the filter capacitance is between 50 pF and 270 pF. The value of the filter resistor can be calculated from the filter capacitance and the desired filter corner frequency  $f_F$ .

$$R_{F} = \frac{1}{2\pi \times f_{F} \times C_{F}} \tag{23}$$

After  $R_F$  is defined  $R_{SLOPE}$  can be calculated. The amount of slope compensation is defined by the stability requirements of the inner peak current loop of the control algorithm and is measured by the number m. When the slope of the applied compensation ramp equals the down slope of the output inductor current waveform reflected across the primary side current sense resistor  $(dV_L/dt)$ , m equals 1. The minimum value of m is 0.5 to prevent current loop instability. Best current mode performance can be achieved around m=1. The further increase of m moves the control closer to voltage mode control operation.

In the UCC2897, controller slope compensation is implemented by sourcing a linearly increasing current at the CS pin. When this current passes through the current sense filter resistor (R<sub>F</sub>), it is converted to a slope compensation ramp which can be characterized by its  $\left( dV_{S}/dt \right)$ . The  $\left( dV_{S}/dt \right)$  of the slope compensation current is defined by R<sub>SLOPE</sub> according to:

$$\frac{\text{dI}_{S}}{\text{dt}} = \frac{5 \times 2 \text{ V}}{\text{t}_{ON} \times \text{R}_{SLOPE}}$$

(24)

where

- 2V is the peak-to-peak ramp amplitude of the internal oscillator waveform

- 5 is the multiplication factor of the internal current mirror

The voltage equivalent of the compensation ramp  $(dV_S/dt)$  can be easily obtained by multiplying with R<sub>F</sub>. After introducing the application specific m and  $(dV_I/dt)$  values, the equation can be rearranged for R<sub>SLOPE</sub>:

$$R_{SLOPE} = \frac{5 \times 2 \text{ V} \times R_F}{t_{ON} \times m \times \left(\frac{dV_L}{dt}\right)}$$

(25)

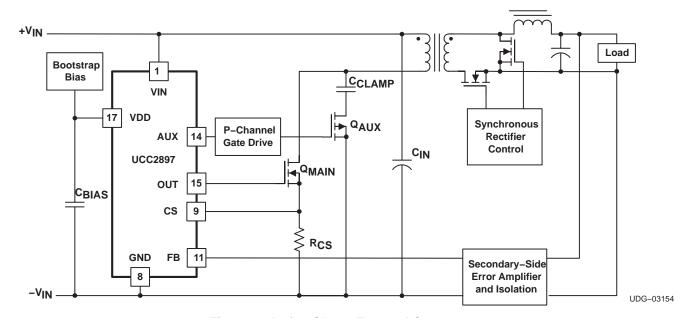

The UCC2897 controller is dedicated to control current mode active clamp flyback or forward converters in an isolated power supply. The key advantage of the active clamp topologies is the zero voltage switching (ZVS) of the primary side semiconductors. This operating mode reduces the switching losses of the converter, thus facilitates higher switching frequencies or improves efficiency when operated at similar frequencies as its hard switched counterparts. The simplified schematic below demonstrates the typical implementation of an active clamp forward converter with high-side clamp utilizing a P-channel auxiliary switch.

Detailed analysis and design examples of active clamp converters are published in the references listed at the end of this datasheet.

Figure 8. Active Clamp Forward Converter

### **Gate Drive Implementation**

The low side P-channel gate drive circuit involves a level shifter using a capacitor and a diode which ensures that the gate drive amplitude of the auxiliary switch is independent of the actual duty cycle of the converter.

Detailed analysis and design examples of these and many similar gate drive solutions are given in reference [6].

Figure 9. Low-Side P-Channel

# **Bootstrap Biasing**

Many converters use a bootstrap circuit to generate its own bias power during steady state operation. The popularity of this solutions is justified by the simplicity and high efficiency of the circuit. Usually, bias power is derived from the main transformer by adding a dedicated, additional winding to the structure. Using a flyback converter as shown in Figure 12, a bootstrap winding provides a quasi-regulated bias voltage for the primary side control circuits. The voltage on the VDD pin is equal to the output voltage times the turns ratio between the output and the bootstrap windings in the transformer. Since the output is regulated, the bias rail is regulated as well.

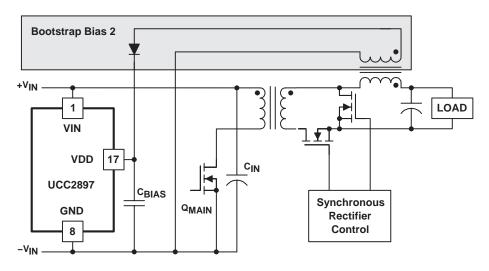

While the same arrangement can be used in a forward type converter, the bootstrap winding off the main power transformer would not be able to provide a quasi-regulated voltage. In the forward converter, the voltage across the bootstrap winding equals the input voltage times the turns ratio. Accordingly the bias voltage would vary with the input voltage and most likely would exceed the maximum operating voltage of the control circuits at high line. A linear regulator can be used to limit and regulate the bias voltage if the power dissipation is acceptable. Another possible solution for the forward converter is to generate the bias voltage from the output inductor as shown in Figure 13.

Figure 10. Bootstrap Bias 1, Flyback Example

This solution uses the regulated output voltage across the output inductor during the freewheeling period to generate a quasi-regulated bias for the control circuits.

UDG-03155

UDG-03156

Figure 11. Bootstrap Bias 2, Forward Example

TEXAS INSTRUMENTS www.ti.com

This solution uses the regulated output voltage across the output inductor during the freewheeling period to generate a quasi-regulated bias for the control circuits.

Both of the illustrated solution provides reliable bias power during normal operation. Note that in both cases, the bias voltages are proportional to the output voltage. This nature of the bootstrap bias supply causes the converter to operate in a hiccup mode under significant overload or under short-circuit conditions as the bootstrap winding is not able to hold the bias rail above the undervoltage lockout threshold of the controller.

# ADDITIONAL APPLICATION INFORMATION

## **References and Additional Development Tools**

- Evaluation Module: UCC2891EVM, 48-V to 3.3-V, 30-A Forward Converter with Active Clamp Reset.

- 2. User's Guide: Using the UCC2891EVM, 48-V to 3.3-V, 30-A Forward Converter with Active Clamp Reset, (SLUU178)

- 3. Application Note: Designing for High Efficiency with the UCC2891 Active Clamp PWM Controller, Steve Mappus (SLUA303)

- 4. Power Supply Design Seminar Topic: Design Considerations for Active Clamp and Reset Technique, D. Dalal, SEM1100–Topic3 (SLUP112)

- 5. Power Supply Design Seminar Topic: Active Clamp and Reset Technique Enhances Forward Converter Performance, B. Andreycak, SEM1000–Topic 3. (SLUP108)

- 6. Power Supply Design Seminar Topic: Design and Application Guide for High Speed MOSFET Gate Drive Circuits, L. Balogh, SEM1400–Topic 2 (SLUP169)

- 7. Datasheet: UCC3580, Single Ended Active-Clamp/Reset PWM Controller, (SLUS292A)

- 8. Evaluation Module: UCC3580EVM, Flyback Converters, Active Clamp vs. Hard-Switched.

- 9. Reference Designs: Highly Efficient 100W Isolated Power Supply Reference Design Using UCC3580–1. Texas Instruments Hardware Reference Design Number PMP206.

- 10. Reference Designs: Active Clamp Forward Reference Design using UCC3580–1. Texas Instruments Hardware Reference Design Number PMP368

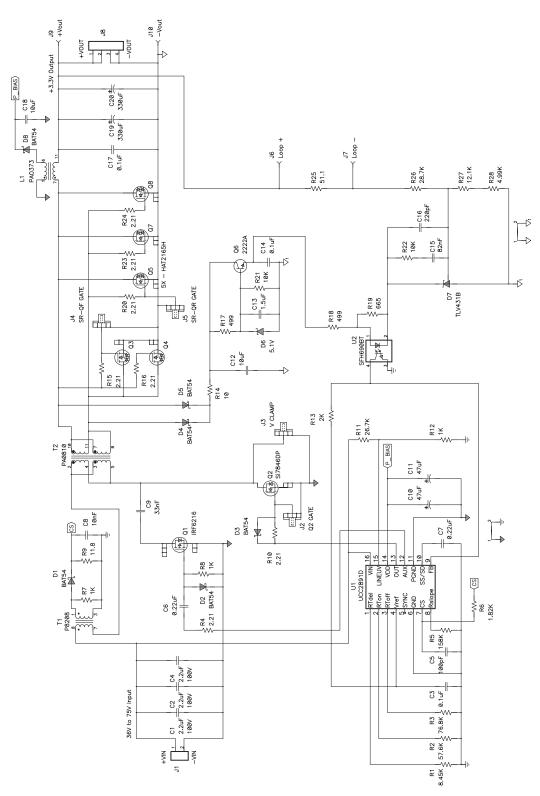

#### **Reference Circuit**

For completeness, the schematic diagram of a complete active clamp forward converter using the UCC2897 is shown in Figure 12. The UCC2891 includes many of the core features of the UCC2897 and their setup and operation are almost identical. The detailed description of the circuit operation and design procedure can be found in SLUU178.

Figure 12. UCC2891 EVM Schematic

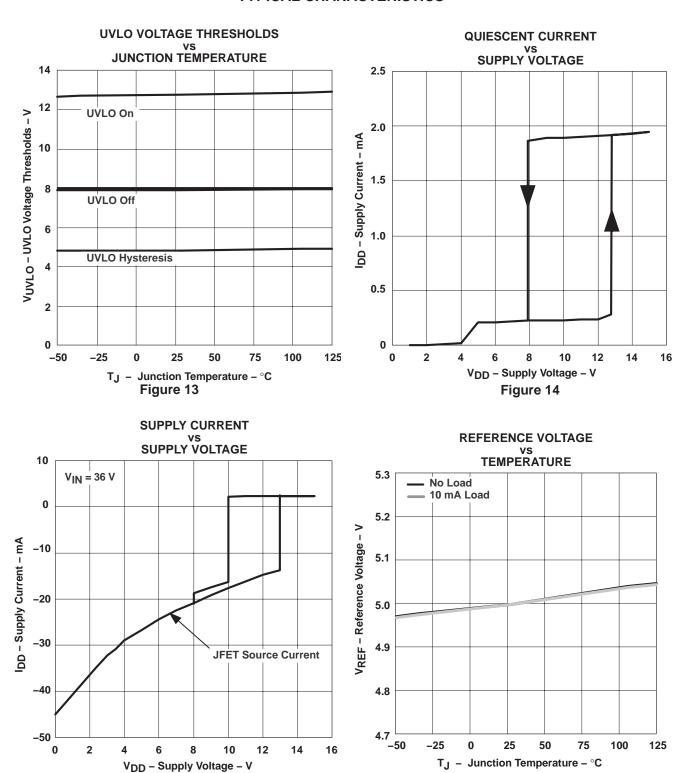

Figure 15

Figure 16

# SOFTSTART/SHUTDOWN THRESHOLD VOLTAGE

# **CURRENT SENSE THRESHOLD VOLTAGE** vs JUNCTION TEMPERATURE 1.4 V<sub>CS</sub> – Current Sense Threshold Voltage – V 1.2 1.0 8.0 **Hiccup Mode** 0.6 0.4 **Cycle-by-Cycle Current Limit** 0.2 0 -50 -25 25 50 75 100 125 T<sub>J</sub> - Junction Temperature - °C Figure 23

T<sub>J</sub> - Junction Temperature - °C

Figure 28

T<sub>J</sub> - Junction Temperature - °C

Figure 27

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| UCC2897PW        | NRND       | TSSOP        | PW                 | 20   | 70             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | UCC2897                 |         |

| UCC2897PWG4      | NRND       | TSSOP        | PW                 | 20   | 70             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | UCC2897                 |         |

| UCC2897PWR       | NRND       | TSSOP        | PW                 | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | UCC2897                 |         |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

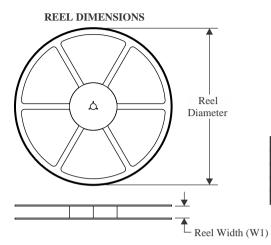

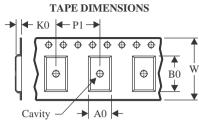

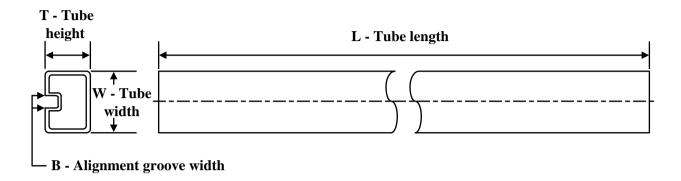

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

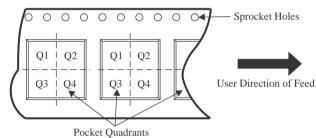

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UCC2897PWR | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

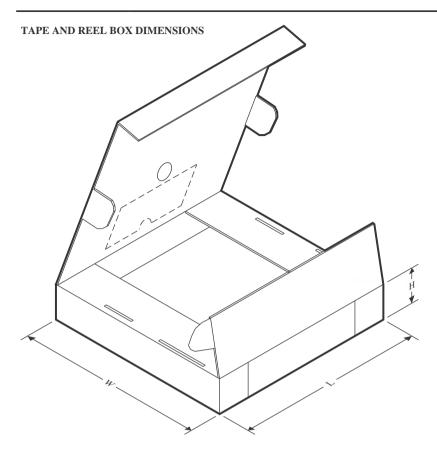

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

### \*All dimensions are nominal

| Г | Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|------------|--------------|-----------------|------|------|-------------|------------|-------------|

|   | UCC2897PWR | TSSOP        | PW              | 20   | 2000 | 356.0       | 356.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

# **TUBE**

#### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| UCC2897PW   | PW           | TSSOP        | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| UCC2897PWG4 | PW           | TSSOP        | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

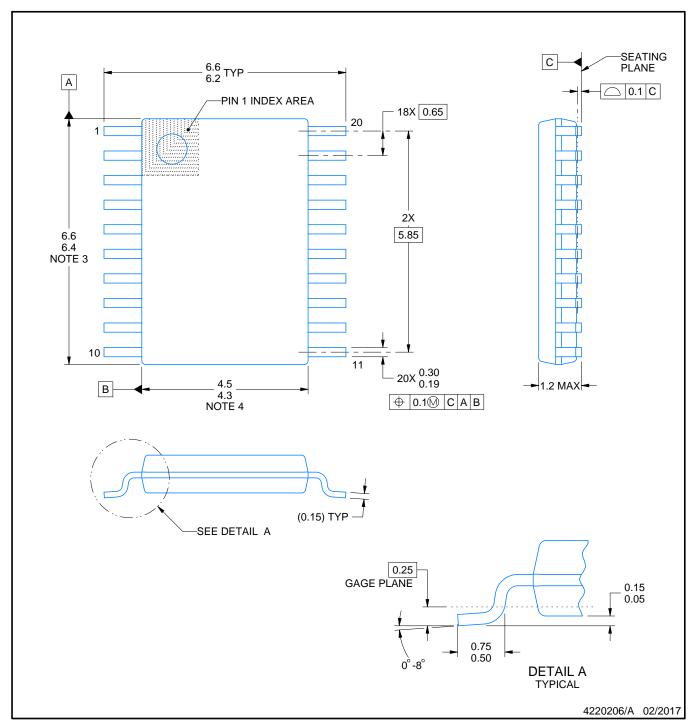

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

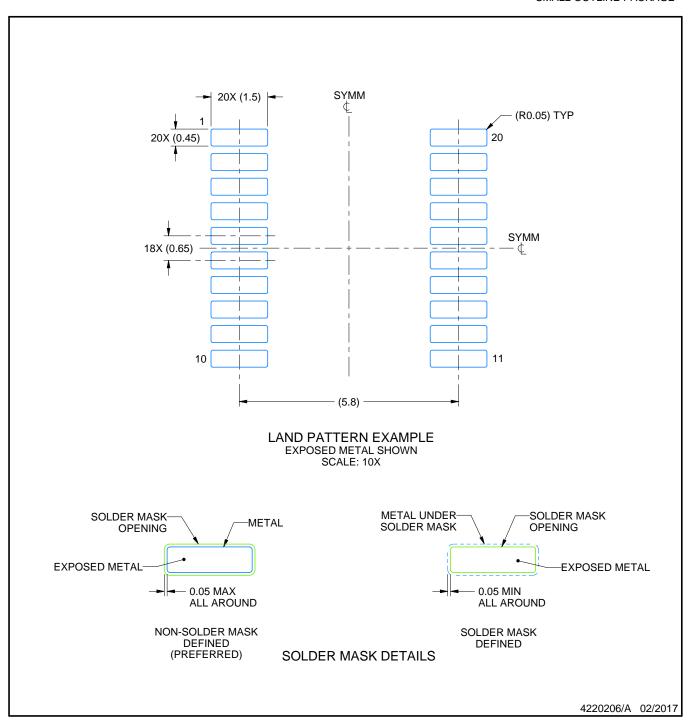

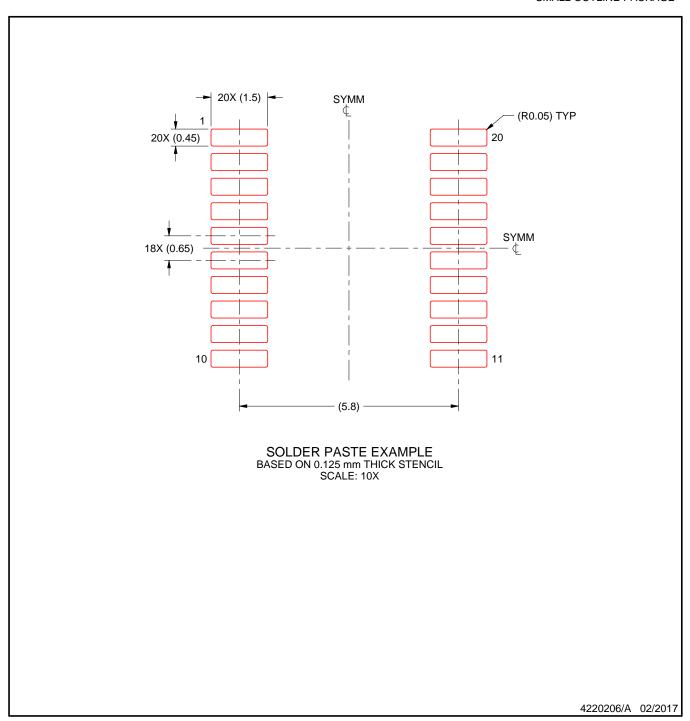

SMALL OUTLINE PACKAGE

NOTES: (continued)

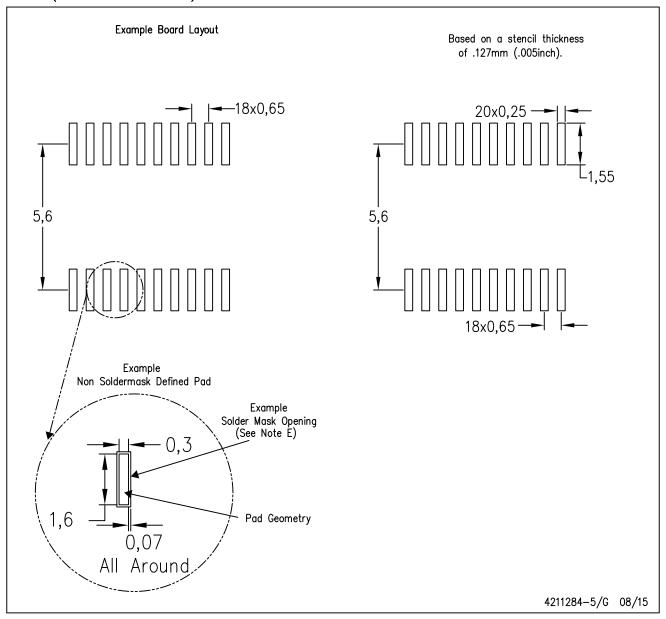

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.