SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

- Controlled Baseline

One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of -25°C to 110°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product Change Notification

- Qualification Pedigree<sup>†</sup>

- Zero to 100% Duty Cycle Control

- Programmable Output Turn-On Delay

- Compatible with Voltage or Current Mode Topologies

- Practical Operation at Switching Frequencies to 1 MHz

- Four 2 A Totem Pole Outputs

- 10 MHz Error Amplifier

- Under-Voltage Lockout

- <sup>†</sup> Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

- Outputs Active Low During UVLO

- Soft-Start Control

- Latched Over-Current Comparator With Full Cycle Restart

- Trimmed Reference

|                                                                                                                                      | DW PACKAGE<br>(TOP VIEW)                                                |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| VREF [<br>E/AOUT [<br>EA- [<br>EA+ [<br>CS+ [<br>SOFTSTART [<br>GND [<br>GND [<br>DELAYSET C-D [<br>NC [<br>OUTD [<br>OUTC [<br>VC [ | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | <ul> <li>28 GND</li> <li>27 RAMP</li> <li>26 SLOPE</li> <li>25 CLOCKSYNC</li> <li>24 FREQSET</li> <li>23 DELAYSET A-B</li> <li>22 GND</li> <li>21 GND</li> <li>20 GND</li> <li>19 NC</li> <li>18 OUTA</li> <li>17 OUTB</li> <li>16 PWRGND</li> <li>15 VIN</li> </ul> |  |  |  |  |  |  |  |  |

NC = No Connect

#### description/ordering information

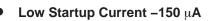

The UC2875 integrated circuit implements control of a bridge power stage by phase-shifting the switching of one half-bridge with respect to the other, allowing constant frequency pulse-width modulation in combination with resonant, zero-voltage switching for high efficiency performance at high frequencies. This circuit may be configured to provide control in either voltage or current mode operation, with a separate over-current shutdown for fast fault protection.

A programmable time delay is provided to insert a dead-time at the turn-on of each output stage. This delay, providing time to allow the resonant switching action, is independently controllable for each output pair (A–B, C–D).

| т <sub>А</sub> | PACKA    | AGE‡          | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |  |  |

|----------------|----------|---------------|--------------------------|---------------------|--|--|

| –25°C to 110°C | SOP – DW | Tape and reel | UC2875SDWREP             | UC2875SEP           |  |  |

**ORDERING INFORMATION**

<sup>‡</sup>Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2004 – 2008 Texas Instruments Incorporated

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

#### description/ordering information

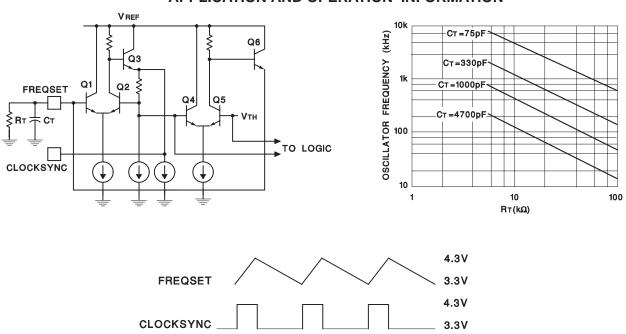

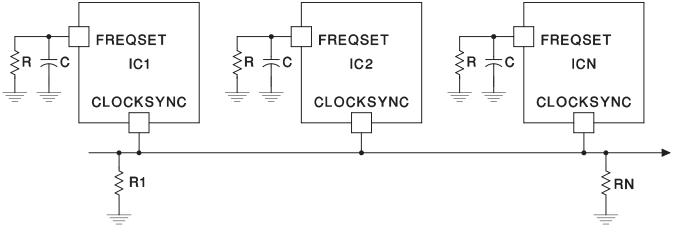

With the oscillator capable of operation at frequencies in excess of 2 MHz, overall switching frequencies to 1 MHz are practical. In addition to the standard free running mode, with the CLOCKSYNC pin, the user may configure these devices to accept an external clock synchronization signal, or may lock together up to 5 units with the operational frequency determined by the fastest device.

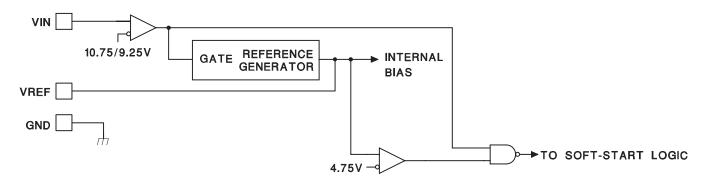

Protective features include an undervoltage lockout which maintains all outputs in an active-low state until the supply reaches a 10.75 V threshold. 1.5 V hysteresis is built in for reliable, boot-strapped chip supply. Over-current protection is provided, and will latch the outputs in the OFF state within 70 ns of a fault. The current-fault circuitry implements full-cycle restart operation.

Additional features include an error amplifier with band-width in excess of 7 MHz, a 5 V reference, provisions for soft-starting, and flexible ramp generation and slope compensation circuitry.

This device is available in 28-pin "bat-wing" SOIC plastic package for operation over -25°C to +110°C operation.

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

PACKAGE DW = Plastic SOIC

**TEMPERATURE INDICATOR** S = -25°C to 110°C

PRODUCT OPTION

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

| absolute maximum ratings over operating free-air temperature range                                                    | ge (unless otherwise noted) <sup>†‡</sup>       |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Supply voltage (VC, VIN)                                                                                              |                                                 |

| Output current (sink or source), I <sub>O,</sub> DC                                                                   | 0.50 A                                          |

| Pulse (0.5 μs)                                                                                                        |                                                 |

| Analog I/O voltage                                                                                                    | $\dots \dots \dots \dots \dots -0.3$ V to 5.3 V |

| Operating jucntion temperature range, T <sub>J</sub>                                                                  |                                                 |

| Storage temperature range, T <sub>stg</sub><br>Lead temperature soldering 1,6 mm (1/16 inch) from case for 10 seconds | 65°C to 150°C                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> Unless otherwise indicated, voltages are reference to ground and currents are positive into and negative out of the specified terminals.

## electrical characteristics, $T_A = -25^{\circ}$ C to $110^{\circ}$ C, VC = VIN = 12 V, $R_{FREQSET} = 12 k\Omega$ , $C_{FREQSET} = 330 \text{ pF}$ , $R_{SLOPE} = 12 k\Omega$ , $C_{RAMP} = 200 \text{ pF}$ , $C_{DELAYSET A-B} = C_{DELAYSET C-D} = 0.01 \mu$ F, $I_{DELAYSET A-B} = I_{DELAYSET C-D} = -500 \mu$ A, and $T_A = T_J$ (unless otherwise stated)

| PARAMETER                                    | TEST CONDITIONS                                                       | MIN  | TYP   | MAX   | UNITS  |

|----------------------------------------------|-----------------------------------------------------------------------|------|-------|-------|--------|

| Undervoltage Lockout                         |                                                                       |      |       |       |        |

| Start threshold                              |                                                                       |      | 10.75 | 11.75 | V      |

| UVLO hysteresis                              |                                                                       | 0.5  | 1.25  | 2     | V      |

| Supply Current                               |                                                                       |      |       |       |        |

| Supply current, I <sub>IN</sub> startup      | VIN = 8 V, VC = 20 V, R <sub>SLOPE</sub> open, I <sub>DELAY</sub> = 0 |      | 150   | 600   | μA     |

| Supply current, I <sub>C</sub> startup       | VIN = 8 V, VC = 20 V, R <sub>SLOPE</sub> open, I <sub>DELAY</sub> = 0 |      | 10    | 100   | μA     |

| Supply current, I <sub>IN</sub>              |                                                                       |      | 30    | 44    | mA     |

| Supply current, IC                           |                                                                       |      | 15    | 30    | mA     |

| Voltage Reference                            |                                                                       |      |       |       |        |

| Output voltage                               | $T_J = 25^{\circ}C$                                                   | 4.92 | 5     | 5.08  | V      |

| Line regulation voltage                      | VIN = 11 V to 20 V                                                    |      | 1     | 10    | mV     |

| Load regulation voltage                      | $I_{VREF} = -10 \text{ mA}$                                           |      | 5     | 20    | mV     |

| Total variation                              | Line, Load, Temperature                                               | 4.9  |       | 5.1   | V      |

| Noise voltage                                | 10 Hz to 10 kHz                                                       |      | 50    |       | μVrms  |

| Long term stability                          | 1000 hours, $T_{J} = 125^{\circ}C$                                    |      | 2.5   |       | mV     |

| Short circuit current                        | $VREF = 0 V, 	 T_J = 25^{\circ}C$                                     |      | 60    |       | mA     |

| Error Amplifier                              |                                                                       |      |       |       |        |

| Offset voltage                               |                                                                       |      | 5     | 15    | mV     |

| Input bias current                           |                                                                       |      | 0.6   | 3     | μΑ     |

| Open loop voltage gain (A <sub>VOL)</sub>    | $V_{E/AOUT} = 1 V \text{ to } 4 V$                                    | 60   | 90    |       | dB     |

| Common mode rejection ratio (CMRR)           | $V_{CM}$ = 1.5 V to 5.5 V                                             | 75   | 95    |       | dB     |

| PSRR                                         | VIN = 11 V to 20 V                                                    | 85   | 100   |       | dB     |

| Output sink current                          | V <sub>E/AOUT</sub> = 1 V                                             | 1    | 2.5   |       | mA     |

| Output source current                        | VE/AOUT = 4 V                                                         |      | -1.3  | -0.5  | mA     |

| High-level output voltage (V <sub>OH</sub> ) | I <sub>E/AOUT</sub> = -0.5 mA                                         | 4    | 4.7   | 5     | V      |

| Low-level output voltage (VOL)               | IE/AOUT = 1 mA                                                        | 0    | 0.5   | 1     | V      |

| Unity gain bandwidth                         |                                                                       | 7    | 11    |       | MHz    |

| Slew rate                                    |                                                                       | 6    | 11    |       | V/µsec |

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

# electrical characteristics, $T_A = -25^{\circ}$ C to $110^{\circ}$ C, VC = VIN = 12 V, $R_{FREQSET} = 12 k\Omega$ , $C_{FREQSET} = 330 pF$ , $R_{SLOPE} = 12 k\Omega$ , $C_{RAMP} = 200 pF$ , $C_{DELAYSET A-B} = C_{DELAYSET C-D} = 0.01 \mu F$ , $I_{DELAYSET A-B} = I_{DELAYSET C-D} = -500 \mu A$ , and $T_A = T_J$ (unless otherwise stated)

| PARAMETER                         | TEST CONDITIONS                                 | MIN  | TYP   | MAX  | UNITS |

|-----------------------------------|-------------------------------------------------|------|-------|------|-------|

| PWM Comparator                    |                                                 | •    |       |      |       |

| Ramp offset voltage               | $T_J = 25^{\circ}C$ , See Note 3                |      | 1.3   |      | V     |

| Zero phase shift voltage          | See Note 4                                      | 0.55 | 0.9   |      | V     |

|                                   | V <sub>E/AOUT</sub> > (Ramp Peak + Ramp Offset) | 98   | 99.5  | 102  |       |

| PWM phase shift (See Note 1)      | VE/AOUT < Zero Phase Shift Voltage              | 0    | 0.5   | 2    | %     |

| Output Skew (See Note 1)          | V <sub>E/AOUT</sub> < 1 V                       |      | 5     | ±20  | ns    |

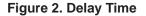

| Ramp to output delay              | See Note 6                                      |      | 65    | 125  | ns    |

| Oscillator                        |                                                 |      |       |      |       |

| Initial accuracy                  | $T_J = 25^{\circ}C$                             | 0.85 | 1     | 1.15 | MHz   |

| Voltage stability                 | VIN = 11 V to 20 V                              |      | 0.2   | 2    | %     |

| Total variation                   | Line, Temperature                               | 0.80 |       | 1.20 | MHz   |

| Sync pin threshold                | $T_{J} = 25^{\circ}C$                           |      | 3.8   |      | V     |

| Clock out peak                    | $T_{J} = 25^{\circ}C$                           |      | 4.3   |      | V     |

| Clock out low                     | $T_{J} = 25^{\circ}C$                           |      | 3.3   |      | V     |

| Clock out pulse width             | RCLOCKSYNC = $3.9 \text{ k}\Omega$              |      | 30    | 100  | ns    |

| Maximum frequency                 | $R_{FREQSET} = 5 k\Omega$                       | 2    |       |      | MHz   |

| Ramp Generator/Slope Compensation |                                                 |      |       |      |       |

| Minimum ramp current              | $I_{SLOPE} = 10 \mu A$ , $V_{FREQSET} = VREF$   |      | -11   | -14  | μΑ    |

| Maximum ramp current              | ISLOPE = 1 mA, VFREQSET = VREF                  | -0.8 | -0.95 |      | mA    |

| Ramp valley                       |                                                 |      | 0     |      | V     |

| Ramp peak – clamping level        | $R_{FREQSET} = 100 \text{ k}\Omega$             |      | 3.8   | 4.1  | V     |

| Current Limit                     |                                                 |      |       |      |       |

| Input bias current                | $V_{CS}$ + = 3 V                                |      | 2     | 5    | μΑ    |

| Threshold voltage                 |                                                 | 2.4  | 2.5   | 2.6  | V     |

| Delay to output                   |                                                 |      | 85    | 150  | ns    |

| Soft-Start/Reset Delay            |                                                 |      |       |      |       |

| Charge current                    | VSOFTSTART = 0.5 V                              | -20  | -9    | -3   | μΑ    |

| Discharge current                 | VSOFTSTART = 1 V                                | 120  | 230   |      | μΑ    |

| Restart threshold                 |                                                 | 4.3  | 4.7   |      | V     |

| Discharge level                   |                                                 |      | 300   |      | mV    |

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

## electrical characteristics, $T_A = -25^{\circ}$ C to 110°C, VC = VIN = 12 V, $R_{FREQSET} = 12 \text{ k}\Omega$ , $C_{FREQSET} = 330 \text{ pF}$ , $R_{SLOPE} = 12 \text{ k}\Omega$ , $C_{RAMP} = 200 \text{ pF}$ , $C_{DELAYSET A-B} = C_{DELAYSET C-D} = 0.01 \mu$ F, $I_{DELAYSET A-B} = I_{DELAYSET C-D} = -500 \mu$ A, and $T_A = T_J$ (unless otherwise stated)

| PARAMETER         | TEST CONDITIONS                               | MIN | TYP | MAX | UNITS |  |  |

|-------------------|-----------------------------------------------|-----|-----|-----|-------|--|--|

| Output Drivers    |                                               |     |     |     |       |  |  |

|                   | I <sub>OUT</sub> = 50 mA                      |     | 0.2 | 0.4 |       |  |  |

| Output low level  | I <sub>OUT</sub> = 500 mA                     |     | 1.2 | 2.6 | V     |  |  |

|                   | I <sub>OUT</sub> = -50 mA                     |     | 1.5 | 2.5 |       |  |  |

| Output high level | I <sub>OUT</sub> = -500 mA                    |     | 1.7 | 2.6 | V     |  |  |

| Delay Set         |                                               |     |     |     |       |  |  |

| Delay set voltage | I <sub>DELAY</sub> = -500 μA                  | 2.3 | 2.4 | 2.6 | V     |  |  |

| Delay time        | $I_{DELAY} = -250 \ \mu$ A, See Notes 2 and 5 | 150 | 250 | 600 | ns    |  |  |

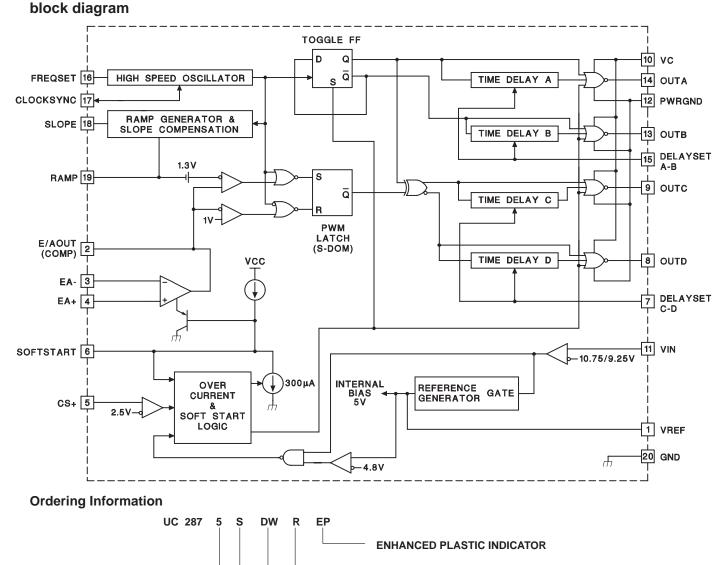

NOTES: 1. Phase shift percentage (0% = 0°, 100% = 180°) is defined as  $\theta$  = 200/T  $\Phi$ %, where  $\theta$  is the phase shift, and  $\Phi$  and T are defined in Figure 1. At 0% phase shift,  $\Phi$  is the output skew.

2. Delay time is defined as delay = T (1/2-(duty cycle)), where T is defined in Figure 1.

3. Ramp offset voltage has a temperature coefficient of about 4.0 mV/°C.

4. Zero phase shift voltage has a temperature coefficient of about 2.0 mV/°C.

5. Delay time can be programmed via resistors from the delay set pins to ground. Delay time  $\approx$  (62.5 x 10<sup>-12</sup>) / I<sub>DELAY</sub> sec where I<sub>DELAY</sub> = Delay set voltage / R<sub>DELAY</sub>. The recommended range for I<sub>DELAY</sub> is 25  $\mu$ A  $\leq$  I<sub>DELAY</sub>  $\leq$  1 mA

6. Ramp delay to output time is defined in NO TAG.

#### Figure 1. Phase Shift and Output Skew

#### APPLICATION AND OPERATION INFORMATION

#### **Pin Descriptions**

**CLOCKSYNC** (bi-directional clock and synchronization pin): Used as an output, this pin provides a clock signal. As an input, this pin provides a synchronization point. In its simplest usage, multiple devices, each with their own local oscillator frequency, may be connected together by the CLOCKSYNC pin and will synchronize on the fastest oscillator. This pin may also be used to synchronize the device to an external clock, provided the external signal is of higher frequency than the local oscillator. A resistor load may be needed on this pin to minimize the clock pulse width.

**E/AOUT** (error amplifier output): This is is the gain stage for overall feedback control. Error amplifier output voltage levels below 1 volt will force 0° phase shift. Since the error amplifier has a relatively low current drive capability, the output may be overridden by driving with a sufficiently low impedance source.

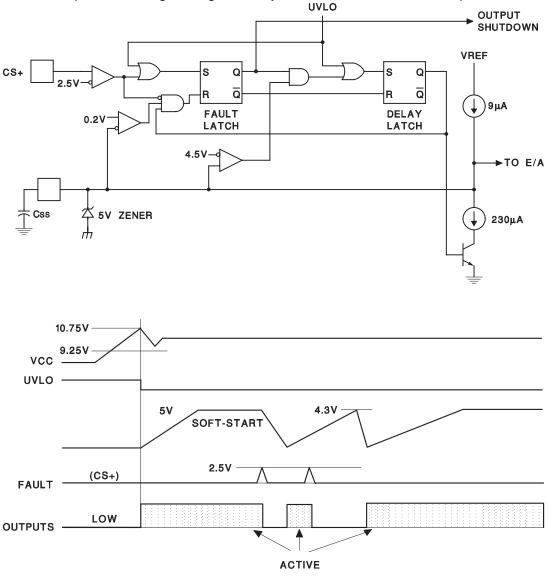

**CS+** (current sense): The non-inverting input to the current- fault comparator whose reference is set internally to a fixed 2.5 V (separate from VREF). When the voltage at this pin exceeds 2.5 V the current-fault latch is set, the outputs are forced OFF and a SOFT-START cycle is initiated. If a constant voltage above 2.5 V is applied to this pin the outputs are disabled from switching and held in a low state until the CS+ pin is brought below 2.5 V. The outputs may begin switching at 0 degrees phase shift before the SOFTSTART pin begins to rise -- this condition will not prematurely deliver power to the load.

**FREQSET** (oscillator frequency set pin): A resistor and a capacitor from FREQSET to GND will set the oscillator frequency.

**DELAYSET A–B, DELAYSET C–D** (output delay control): The user programmed current flowing from these pins to GND set the turn-on delay for the corresponding output pair. This delay is introduced between turn-off of one switch and turn-on of another in the same leg of the bridge to provide a dead time in which the resonant switching of the external power switches takes place. Separate delays are provided for the two half-bridges to accommodate differences in the resonant capacitor charging currents.

**EA**– (error amplifier inverting input): This is normally connected to the voltage divider resistors which sense the power supply output voltage level.

**EA+** (error amplifier non-inverting input): This is normally connected to a reference voltage used for comparison with the sensed power supply output voltage level at the EA+ pin.

**GND** (signal ground):All voltages are measured with respect to GND. The timing capacitor, on the FREQSET pin, any bypass capacitor on the VREF pin, bypass capacitors on V<sub>IN</sub> and the ramp capacitor, on the RAMP pin, should be connected directly to the ground plane near the signal ground pin.

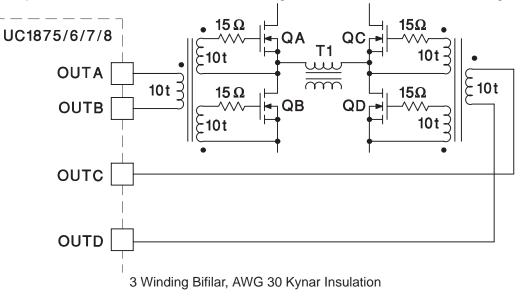

**OUTA-OUTD** (outputs A–D): The outputs are 2 A totem- pole drivers optimized for both MOSFET gates and level-shifting transformers. The outputs operate as pairs with a nominal 50% duty-cycle. The A–B pair is intended to drive one half-bridge in the external power stage and is syncronized with the clock waveform. The C–D pair will drive the other half-bridge with switching phase shifted with respect to the A–B outputs.

**PWRGND** (power ground):VC should be bypassed with a ceramic capacitor from the VC pin to the section of the ground plane that is connected to PWRGND. Any required bulk reservoir capacitor should parallel this one. Power ground and signal ground may be joined at a single point to optimize noise rejection and minimize DC drops.

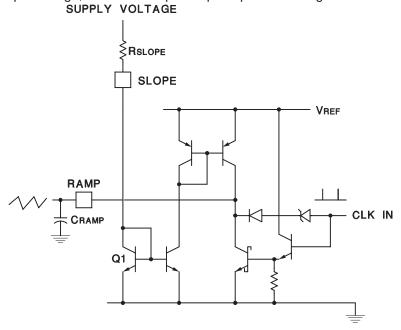

**RAMP** (voltage ramp): This pin is the input to the PWM comparator. Connect a capacitor from here to GND. A voltage ramp is developed at this pin with a slope:

$$\frac{dV}{dT} = \frac{\text{SenseVoltage}}{R_{\text{SLOPE}} \times C_{\text{RAMP}}}$$

Current mode control may be achieved with a minimum amount of external circuitry, in which case this pin provides slope compensation.

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

#### APPLICATION AND OPERATION INFORMATION

Because of the 1.3 V offset between the ramp input and the PWM comparator, the error amplifier output voltage can not exceed the effective ramp peak voltage and duty cycle clamping is easily achievable with appropriate values of  $R_{SLOPE}$  and  $C_{RAMP}$ .

**SLOPE** (set ramp slope/slope compensation): A resistor from this pin to V<sub>CC</sub> will set the current used to generate the ramp. Connecting this resistor to the DC input line voltage will provide voltage feed-forward.

**SOFTSTART** (soft start): SOFTSTART will remain at GND as long as VIN is below the UVLO threshold. SOFTSTART will be pulled up to about 4.8 V by an internal 9  $\mu$ A current source when VIN becomes valid (assuming a non-fault condition). In the event of a current-fault (CS+ voltage exceeding 2.5 V), SOFTSTART will be pulled to GND and them ramp to 4.8 V. If a fault occurs during the SOFTSTART cycle, the outputs will be immediately disabled and SOFTSTART must charge fully prior to resetting the fault latch.

For paralleled controllers, the SOFTSTART pins may be paralled to a single capacitor, but the charge currents will be additive.

**VC** (output switch supply voltage): This pin supplies power to the output drivers and their associated bias circuitry. Connect VC to a stable source above 3 V for normal operation, above 12 V for best performance. This supply should be bypassed directly to the PWRGND pin with low ESR, low ESL capacitors.

**VIN** (primary chip supply voltage): This pin supplies power to the logic and analog circuitry on the integrated circuit that is not directly associated with driving the output stages. Connect VIN to a stable source above 12 V for normal operation. To ensure proper chip functionality, these devices will be inactive until VIN exceeds the upper undervoltage lockout threshold. This pin should by bypassed directly to the GND pin with low ESR, low ESL capacitors.

NOTE: When VIN exceeds the UVLO threshold the supply current ( $I_{IN}$ ) will jump from about 100  $\mu$ A to a current in excess of 20  $\mu$ A. If the UC2875 is not connected to a well bypassed supply, it may immediately enter UVLO again.

**VREF**: This pin is an accurate 5 V voltage reference. This output is capable of delivering about 60 mA to peripheral circuitry and is internally short circuit current limited. VREF is disabled while VIN is low enough to force the chip into UVLO. The circuit is also in UVLO until VREF reaches approximately 4.75 V. For best results bypass VREF with a 0.1  $\mu$ F, low ESR, low ESL, capacitor to the GND pin.

#### Figure 3. Undervoltage Lockout

When power is applied to the circuit and VIN is below the upper UVLO threshold,  $I_{IN}$  will be below 600  $\mu$ A, the reference generator will be off, the fault latch is reset, the soft-start pin is discharged, and the outputs are actively held low. When VIN exceeds the upper UVLO threshold, the reference generator turns on. All else remains in the shut-down mode until the output of the reference, VREF, exceeds 4.75 V.

SGLS233A – FEBRUARY 2004 – REVISED DECEMBER 2008

#### **APPLICATION AND OPERATION INFORMATION**

The high frequency oscillator may be either free-running or externally synchronized. For free-running operation, the frequency is set via an external resistor and capacitor to ground from the FREQSET pin.

The CLOCKSYNC pin of the oscillator may be used to synchronize multiple UC2875 devices simply by connecting the CLOCKSYNC of each UC2875 to the others as in Figure 5.

Figure 5. Synchronizing Multiple UC2875–EP Devices

All ICs will sync to chip with the fastest local oscillator.

- R1 & RN may be needed to keep sync pulse narrow due to capacitance on line.

- R1 & RN may also be needed to properly terminate  $\mathsf{R}_{SYNC}$  line.

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

#### APPLICATION AND OPERATION INFORMATION

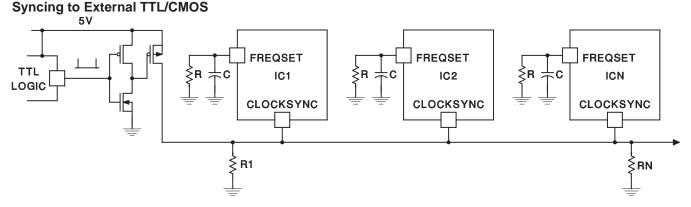

#### Figure 6. Snychronizing to an External TTL/CMOS Clock Signal

ICs will sync to fastest chip or TTL clock if it is higher frequency.

R and RN may be needed for same reasons as above.

Although each UC2875 has a local oscillator frequency, the group of devices will synchronize to the fastest oscillator driving the CLOCKSYNC pin. This arrangement allows the synchronizing connection between ICs to be broken without any local loss of functionality.

Synchronizing the device to an external clock signal may be accomplished with a minimum of external circuitry, as shown in Figure 6.

Capacitive loading on the CLOCKSYNC pin will increase the clock pulse width, and may adversely effect system performance. Therefore, a resistor to ground from the CLOCKSYNC pin is optional, but may be required to offset capacitive loading on this pin. These resistors are shown in the oscillator schematics as R1, RN.

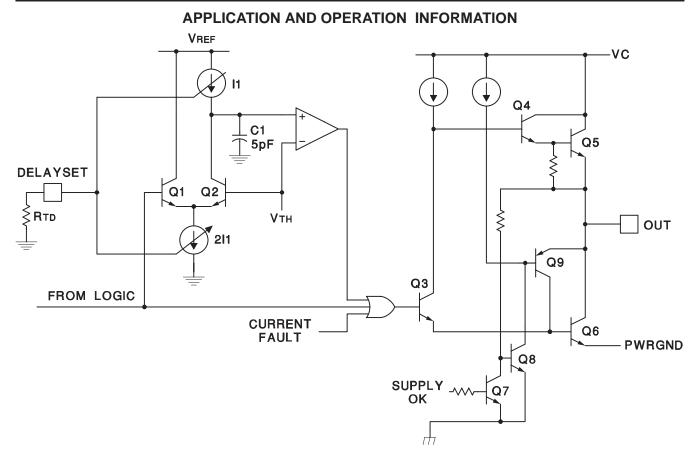

#### **Delay Blocks and Output Stages**

In each of the output stages, transistors Q3 through Q6 form a high-speed totem-pole driver which will source or sink more than one amp peak with a total delay of approximately 30 nanoseconds. To ensure a low output level prior to turn-on, transistors Q7 through Q9 form a self-biased driver to hold Q6 on prior to the supply reaching its turn-on threshold. This circuit is operable when the chip supply is zero. Q6 is also turned on and held low with a signal from the fault logic portion of the chip.

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

Figure 7. Delay Blocks and Output Stages

The delay providing the dead-time is accomplished with C1 which must discharge to  $V_{TH}$  before the output can go high. The time is defined by the current sources, I1, which is programmed by an external resistor,  $R_{TD}$ . The voltage on the Delay Set pins is internally regulated to 2.5 V and the range of dead time control is from 50 to 200 nanoseconds. NOTE: There is no way to disable the delay circuitry, and the delay time must be programmed.

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

#### **Output Switch Orientation**

The four outputs of the UC2875 interface to the full bridge converter switches as shown in Figure 8.

Figure 8. Output Switch Orientation

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

#### APPLICATION AND OPERATION INFORMATION

#### Fault/Soft-Start

The fault control circuitry provides two forms of power shutdown:

- Complete turn-off of all four output power stages.

- Clamping the phase shift command to zero.

Complete turn-off is ordered for an over-current fault or a low supply voltage. When the SOFTSTART pin reaches its low threshold, switching is allowed to proceed while the phase-shift is advanced from zero to its nominal value with the time constant of the SOFT–START capacitor.

The fault logic insures that a continuous fault will institute a low frequency "hiccup" retry cycle by forcing the SOFT–START capacitor to charge through its full cycle between each restart attempt.

Figure 9. Fault/Soft-Start

SGLS233A - FEBRUARY 2004 - REVISED DECEMBER 2008

### APPLICATION AND OPERATION INFORMATION

#### Slope/Ramp Pins

The ramp generator may be configured for the following control methods:

- Voltage Mode

- Voltage Feedforward

- Current Mode

- Current Mode with Slope Compensation

Figure 10 shows a voltage-mode configuration. With  $R_{SLOPE}$  tied to a stable voltage source, the waveform on  $C_{RAMP}$  will be a constant-slope ramp, providing conventional voltage-mode control. If  $R_{SLOPE}$  is connected to the power supply input voltage, a variable-slope ramp will provide voltage feedforward.

#### Figure 10. Slope/Ramp Pins

1. Simple voltage mode operation achieved by placing R<sub>SLOPE</sub> between VIN and SLOPE.

2. Voltage Feedforward achieved by placing R<sub>SLOPE</sub> between supply voltage and SLOPE pin of UC2875.

RAMP

$$\frac{\text{dV}}{\text{dT}} \approx \frac{\text{V}_{\text{Rslope}}}{\text{R}_{\text{SLOPE}} \times \text{C}_{\text{RAMP}}}$$

For current-mode control the ramp generator may be disabled by grounding the slope pin and using the ramp pin as a direct current sense input to the PWM comparator.

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| UC2875SDWREP     | ACTIVE        | SOIC         | DW                 | 28   | 1000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -25 to 110   | UC2875SEP               | Samples |

| V62/04752-01XE   | ACTIVE        | SOIC         | DW                 | 28   | 1000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -25 to 110   | UC2875SEP               | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### OTHER QUALIFIED VERSIONS OF UC2875-EP :

Catalog: UC2875

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

Texas

STRUMENTS

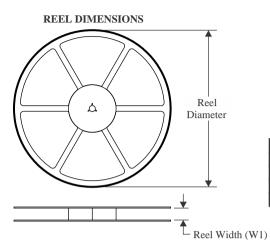

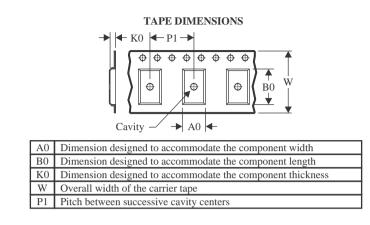

#### TAPE AND REEL INFORMATION

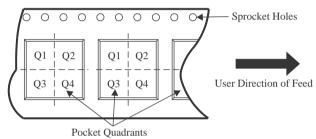

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |  |

|-----------------------------|--|

|                             |  |

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UC2875SDWREP | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

www.ti.com

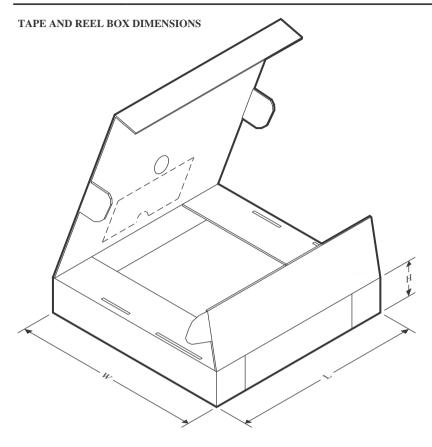

## PACKAGE MATERIALS INFORMATION

5-Apr-2023

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2875SDWREP | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated